## Exp. No. (1) Logic Gate and Boolean Algebra

## **Object**

To study the logical function and to get familiar with Boolean algebra.

## **Theory**

A number system is nothing more than a code representing quantity. For each circuit quantity, there is an assigned symbol for the quantity. After we memorize the code we can count and this lead to arithmetic and higher form of mathematics. So, the binary number system is a code that uses only two basic symbols. These symbols can be any two distinct characters like A and B or the customary 0 and 1.

Gate:- In logic circuit, this is a device with one output and two or more inputs, designed in such a way that there is an output for certain combinations of input signals.

In digital logic there are three basic elements:

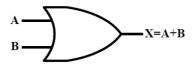

1. The OR gate: It is a device whose output is a logic (1) if either or both inputs are a logic (1). The OR gate is shown by the symbol in Fig.(1) with two inputs (A and B).

#### Fig. (1) The OR Gate.

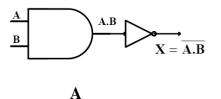

2. The AND gate: It is a device whose output is a logic (1) if both of it's inputs are logic (1). This gate is shown by the symbol in Fig(2) with two inputs marked A and B and one output marked X.

#### Fig. (2) The AND Gate.

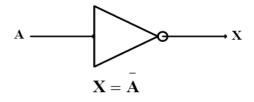

3. The Not gate (Inverter): Is another basic kind of a digital circuit, else called a complementing circuit which is most simple element of digital logic. The inverter is different from AND and OR gates, in that it has only a single input. As a result, it dose not perform any decision making function that is dependent on a combination of inputs. Instead the inverter simply convert logic (1) at it's input to logic (0) at it's output and conversely, a logic (0) to logic (1). The inverter can be represented by the symbol shown in Fig. (3).

Fig. (3) The NOT Gate.

#### Notes:

- The AND function may not be constructed of OR gates only.

- The OR function may not be constructed of AND gates only.

- The NOT function may not be constructed of AND, OR gates.

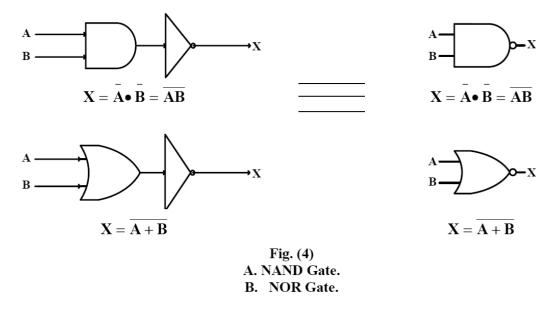

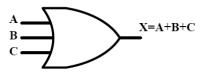

Two types of logic gates found often in digital circuit are the NAND (NOTAND) and NOR (NOT-OR). As their name imply, a NAND gate is an inverted AND function, each LOW (0) output of AND function is made HIGH (1). And NOR gate is equivalent of an inverted OR functions and will yield logic (1) output if both inputs are logic (0). NAND and NOR gates are shown in Fig. (4).

**Boolean algebra:** is a name given to mean of mathematically manipulation of Boolean expression for the purpose of putting them in their simplest form. There are three law of Boolean algebra:

1. The commutative law: States that, when inputs to a logic symbol are AND ed or OR ed, the order in which they are written doesn't affect the answer results, therefore:

$$AB = BA$$

$A + B = B + A$

2. The associative law: State that, the grouping of AND ed function as they written doesn't affect the value of the output, nor dose the grouping of OR ed function, therefore:

(AB)

$$C = A (BC)$$

(A + B) + C = A + (B + C)

3. Distributive law: Is a law provides a powerful tool for manipulation of Boolean expressions. It states that Boolean expression, as in (Convertional) algebra can be (Factored) or simplified through (expression), there are:

$\mathbf{AB} + \mathbf{AC} = \mathbf{A} (\mathbf{B} + \mathbf{C})$

#### <u>Identities</u>

| A + 1 = 1                     | $\mathbf{A} + \mathbf{A} = \mathbf{A}$ | $A \cdot 0 = 0$       |

|-------------------------------|----------------------------------------|-----------------------|

| $\mathbf{A} + 0 = \mathbf{A}$ | $A + \overline{A} = 1$                 | $A \cdot A = A$       |

| $\overline{\overline{A}} = A$ | A . 1 = A                              | A. $\overline{A} = 0$ |

#### <u>Truth Table</u>

A truth table is a list showing all input-output combination of logic circuit of a logic circuit. The number of horizontal rows in table equals  $(2^n)$ , where "n" is the number of input variable to the logic circuit. To include all possible input combination, we normally list the combination in a binary number progression.

#### Example (1):

Describe the truth table for a two-input OR gate and a three-input OR gate.

Two input OR gate. n = 2Therefore the horizontal rows =  $2^2 = 4$

| Α | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 1 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 1 | 1   |

Three input OR gate. n = 3Therefore the horizontal rows =  $2^3 = 8$

| Α | B | B | A+B |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 1 | 0 | 0 | 1   |

| 0 | 1 | 0 | 1   |

| 1 | 1 | 0 | 1   |

| 0 | 0 | 1 | 1   |

| 1 | 0 | 1 | 1   |

| 0 | 1 | 1 | 1   |

| 1 | 1 | 1 | 1   |

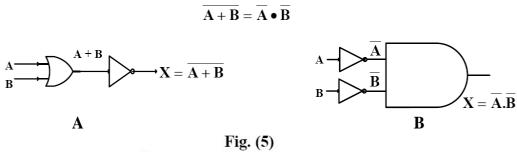

#### <u>De Morgan's Theorems</u>

Much of today logic implementation is based upon a set of rules called De Morgan's Theorems. Basically these theorems demonstrate that, any logic function can be formed from AND-NOT gates (NAND) or from OR-NOT gates (NOR).

These rules may be summarized in the state:

1. The complement of a sum equals the product of the complements.

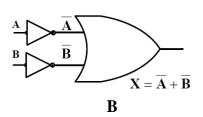

1<sup>st</sup> Law of De Morgan's Theorems

2. The complement of the product equals the sum of the complements.

$\overline{\mathbf{A} \bullet \mathbf{B}} = \overline{\mathbf{A}} + \overline{\mathbf{B}}$

Fig. (6) 2<sup>nd</sup> Law of De Morgan's Theorems

#### **Procedure**

- 1. Connect the circuit shown in Fig. (1).

- 2. Using different states of the inputs, find the truth table of the circuit.

- 3. Connect the circuit in the figures and for each connection repeat step (2).

- a) Fig. (2), (3).

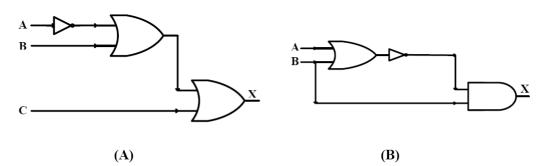

- b) Fig. (4 A and B).

- c) Fig. (5 A and B).

- d) Fig. (6 A and B).

- e) Fig. (7 A and B) and write the Boolean expression for the output.

- 4. Draw and implement the logic circuit for  $X = \overline{AB} + A\overline{B}$  using basic logic gates. Then describe it's truth table, and try to draw the logic circuit for the same function using NAND gate only.

Fig (7)

## **Discussion**

- 1. Prepare the implementation of three inputs AND gate by using NOR gate only. Then show how NAND gate can be used for build the logic circuit for X = A + BC.

- 2. Can you suggest why all logic function in a digital system are often generated with single gate type.

- 3. Draw the logical circuit (F) by using only NAND gate F = AB + D(B + C), and describe it's truth table.

- 4. Prove:

- 1.  $\mathbf{A} + \mathbf{AB} = \mathbf{A} + \mathbf{B}$ .

- 2.  $(A+B)(\overline{A}+C) = AC + \overline{AB} + BC$ .

- 3.  $\overline{\mathbf{A.B.C.D}} = \overline{\mathbf{A}} + \overline{\mathbf{B}} + \overline{\mathbf{C}} + \overline{\mathbf{D}}$ .

- 4.  $ABC + A\overline{B}C + AB\overline{C} = A(B + C)$ .

- 5.  $\overline{\mathbf{A}} \overline{\mathbf{C}} + \overline{\mathbf{A}} \overline{\mathbf{B}} \overline{\mathbf{C}} = \overline{\mathbf{C}} (\overline{\mathbf{A}} + \overline{\mathbf{B}}).$

- 6.  $\overrightarrow{AC} + \overrightarrow{ABC} + \overrightarrow{ACD} + \overrightarrow{CD} = \overrightarrow{A} + \overrightarrow{CD}$ .

## Exp. No. (2)

## **Exclusive OR Gate and it's Applications**

## <u>Object</u>

To study the logic function of exclusive OR (XOR) gate, and become familiar with some of it's applications.

## **Theory**

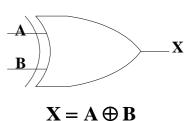

The output of XOR gate, is logic (1) when both inputs are different, and is logic (0) when inputs are the same, Fig. (1) gives the symbol and truth table for this gate.

| Α | В | $\mathbf{X} = \mathbf{A} \oplus \mathbf{B}$ |

|---|---|---------------------------------------------|

| 0 | 0 | 0                                           |

| 0 | 1 | 1                                           |

| 1 | 0 | 1                                           |

| 1 | 1 | 0                                           |

Fig. (1) Exclusive OR gate with it's Truth Table

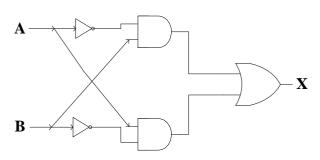

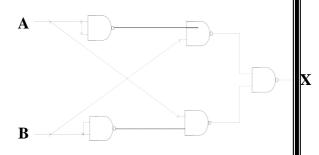

Algebraically XOR output can be written as  $\mathbf{X} = \overline{\mathbf{AB}} + \overline{\mathbf{AB}}$ , and can be implement as in Fig. (2):

(A) Different Gates.

(B) NAND Gates only.

1

#### Applications of XOR gate

There are many applications for XOR gate such as:

#### 1. Arithmetic Operations:

The XOR gate also called (Medulo Two Adder), since it is used t give the sum of two binary numbers, it has been used in many arithmetic circuits (it will be explained in latter experiments).

#### 2. Parity Checker:

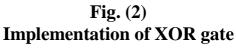

One of the advantages of using digital system, is it's capability of detecting and correction errors. This is used specially when digital information is transmitted or stored. One of the simplest form of error detecting is the parity checker, assume that, we have four bit word, to detect the occurrence of an odd number of errors in this word, a single bit will be added to the word that makes the number of "ones" in the word either even number "Even Parity" or odd number "Odd Parity", so, if an odd number of error occurred in the word then the total number of ones will not remain the same, it will change from odd to even or from even to odd. The XOR gate is the most suitable circuit to provide parity checker. Fig. (2) given the circuit of four bit even parity checker, to have an odd parity checker, we need to complement the output.

Fig. (3) Four Bit Even Parity Checker.

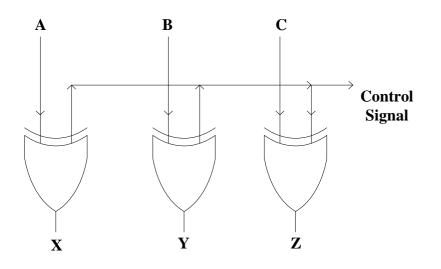

#### 3. Controlled Inverter:

The XOR gate can be used as a "NOT" gate by connecting one of the inputs to the logic (1), for this reason it can be used to complement a word by using one of the inputs as control line, as shown in Fig. (4), when control signal is logic (0) then, X = A; Y = B; Z = C. When control signal is logic (1) then,  $X = \overline{A}$ ;  $Y = \overline{B}$ ;  $Z = \overline{C}$

Fig. (4) Controlled Inverter.

#### 4. Binary to Gray / Gray to Binary Conversion:

The gray code is widely used in many digital systems, specially in shaft register encoders and analog to digital conversion, but it is difficult to use the gray-code in arithmetic operations, since there are only one bit change between two consecutive gray code number, and it is unweighted code, and the XOR gate is the most suitable gate for this purpose as shown in Fig. (5).

#### 5. Combinational Logic Circuit Minimization:

Another useful application for XOR gate is, it's use in minimizing combinational circuit which will be dealt with in detail in other experiment.

#### 6. Digital Comparator:

Many practical applications require the comparator of two numbers A & B searching for either (a) quality or (b) non quality.

If quality is what we looking for, this means A = B, then the output of the logic network (Z<sub>1</sub>) is expressed by the function concluded from the truth table below (Table 1).

$$\mathbf{Z}_1 = \mathbf{A}\mathbf{B} + \mathbf{A}\mathbf{B}$$

When non-quality is what we require, this means  $A \neq B$ , then we can concluded the Boolean expression for (Z<sub>2</sub>) from the truth table (Table 1).

#### $\mathbf{Z}_2 = \mathbf{A}\overline{\mathbf{B}} + \overline{\mathbf{A}}\mathbf{B}$

If the comparison is such that the states of one number with respect to the other is to be specified one of the three conditions A > B, A < B, or  $A \equiv B$  should be known the simple Boolean expressions are:

$AB \quad \text{for} \qquad A > B.$   $\overline{AB} \quad \text{for} \qquad A < B.$   $\& AB + \overline{A} \overline{B} \quad \text{for} \qquad A \equiv B.$

|   |     |     |                                                                                                                                                  | ſ        | I     |       |

|---|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|

| А | A B | ΑĤΒ | $A \bigoplus B \begin{vmatrix} AB + \overline{A}B \\ (Z_1) \end{vmatrix} = \begin{vmatrix} \overline{AB} + \overline{AB} \\ (Z_2) \end{vmatrix}$ |          | A > B | A < B |

|   | D   | ΠΨΒ |                                                                                                                                                  |          |       |       |

| 0 | 0   | 0   | 1                                                                                                                                                | 0        | 0     | 0     |

| 0 | 1   | 1   | 0                                                                                                                                                | 1        | 0     | 1     |

| 1 | 0   | 1   | 0                                                                                                                                                | 1        | 1     | 0     |

| 1 | 1   | 0   | 1                                                                                                                                                | 0        | 0     | 0     |

|   |     |     | T.1.1. (1                                                                                                                                        | <u> </u> |       |       |

Table (1)

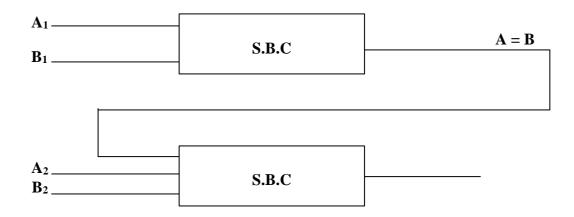

The comparison for two number of more than one binary bit may be summarized by the following steps:

Suppose the two numbers  $X = A_1 A_2$

$$\mathbf{Y} = \mathbf{B}_1 \quad \mathbf{B}_2$$

1. X = Y when  $A_1 = B_1$  and  $A_2 = B_2$ .

2. X > Y If  $A_1 > B_1$  or  $A_1 = B_1$  and  $A_2 > B_2$ .

3. X < Y If  $A_1 < B_1$  or  $A_1 = B_1$  and  $A_2 < B_2$ .

It is clear that to search for any of the three conditions it is only needed to found the equality condition for each higher bit to the next lower bit and so on. The way that equality condition is added to the single bit combater is shown:

Fig. (6) Block diagram of Two-Two Bit Comparator.

#### **Procedure**

- 1. Connect the circuit shown in Fig. (1) and Fig. (2-A) and find the truth table for the circuit.

- 2. Connect the circuit in Fig. (3), find the even parity bit for the numbers

---,----, then find the odd parity bit for the

numbers -----,---- and -----.

- 3. Connect a circuit that convert four bit word using XOR gate, find one's complement for the numbers ------, and ------.

- 4. Connect 5 bit gray to binary converter circuit and find the equivalent binary for the following gray code ------, and ------, then connect 3 bit binary to gray code converter circuit and find the equivalent gray code for these binary numbers -----, -----, and ------.

- 5. Referring to the truth table shown in Table (1) shown in the theory implement a circuit for single bit comparator.

#### **Discussion**

- 1. Draw the circuit diagram for four input XOR gate. Explain the circuit.

- 2. Draw a circuit diagram that detect errors is an odd parity 5 bit word.

- 3. Can you add more applications for XOR gates.

- 4. Write down the equivalent gray code for the numbers 0-15.

- 5. Design a logic circuit that can compare between two-two bit binary number. Draw the circuit and find it's truth table.

Suggest some application where comparator is useful

#### University of Technology Laser & Optoelectronics Engineering Department Digital Electronics lab .

#### Exp. No. (3) w Additional (Half and Full Add

**Binary Additional (Half and Full Adders)**

## <u>Object</u>

To be able to design a circuit to add two or three binary digits.

## **Theory**

## 1. The Half Adder:

Computer addition is performed using certain rules which are similar to those used in adding decimal numbers. Started for the binary system, these rules are as following:-

| Rule (1) | 0+0 | = | 0              |

|----------|-----|---|----------------|

| Rule (2) | 0+1 | = | 1              |

| Rule (3) | 1+1 | = | 0 (With Carry) |

A truth table for the rules of binary addition is shown in Fig. (1). A and B represent two-one bit binary numbers to be added. As the table shows, a sum will be produced when A is one or B one, but not when both bits are one. This can be stated in Boolean terms as  $\overline{AB} + A\overline{B}$  which, you may recall, is the output expression for the Exclusive OR (XOR) network. The expression for the carry output, derived from the table, is (AB). Which may capable of performing the addition of two-one bit number.

#### 2. The Full Adder:

In computer operation, the half-adder is not sufficient for adding more than two –one numbers. Adding binary numbers that have more than two bit position required the useful of Full Adder, which is capable of adding the two bits of each position. For example, adding 0101 and 0101:

| 1◄ | - 0 | <b>←</b> 1 | ← |             |

|----|-----|------------|---|-------------|

| 0  | 1   | 0          | 1 |             |

| 0  | 1   | 0          | 1 |             |

| 1  | 0   | 1          | 0 | = Sum       |

| 0  | -1  | -0-        | 1 | = Carry-Out |

The least significant bits of the two binary numbers are added. In this case, "1+1 = 0" with carry. A zero comes out to the adder as the least significant bit of the sum, and the "1" carry-out produced by this addition is stored. When the next addition is performed, the carry-out resulting from the first addition is fed into the adder along with two (0) bits. The addition of these two bits and the carry-in (carry-out from the first addition) is interpreted as "0+0+1 = 1". This equals (1) with no-carry. Therefore, the second addition produces a sum bit of (1) and no carry-out for the next addition. The third addition, in this case "1+1+0 = 0", equals (0) with carry. The carry is again stored, becoming a carry-in for the final addition. When the final addition is performed, then, "0+0+1 = 1" produced (1) with no carry. Table (2) shows all possible combinations for producing the sum and carry outputs, in truth table form.

Column A & B represented the two bits about to be added. The carry-in column shown the carry-out which will be produced by the pervious addition. The last two column show the sum and carry-out which will be produced by adding the content of the first three columns. The condition required to produce

a (1) in the SUM column of the truth table are defined by the Boolean expression:

## $\mathbf{SUM} = \overline{\mathbf{A}} \,\overline{\mathbf{B}} \,\mathbf{C} + \overline{\mathbf{A}} \,\mathbf{B} \,\overline{\mathbf{C}} + \mathbf{A} \,\overline{\mathbf{B}} \,\overline{\mathbf{C}} + \mathbf{A} \,\mathbf{B} \,\mathbf{C}$

By factoring "C" out of the first and last terms, the expression becomes:

$$\mathbf{SUM} = \mathbf{C}(\overline{\mathbf{A}}\,\overline{\mathbf{B}} + \mathbf{A}\,\mathbf{B}) + \overline{\mathbf{A}}\,\mathbf{B}\,\overline{\mathbf{C}} + \mathbf{A}\,\overline{\mathbf{B}}\,\overline{\mathbf{C}}$$

Next, by factoring " $\overline{\mathbf{C}}$ " out of two middle terms of the original expression, we get:

$$SUM = C(\overline{A}\overline{B} + AB) + \overline{C}(\overline{A}B + A\overline{B})$$

$$\mathbf{SUM} = \mathbf{C}(\mathbf{A} \oplus \mathbf{B}) + \mathbf{C}(\mathbf{A} \oplus \mathbf{B})$$

#### $\mathbf{SUM} = \mathbf{A} \oplus \mathbf{B} \oplus \mathbf{C}$

Similarly, the condition necessary to produced a "1" in the carry-out column of the truth table can be defined by the expression:

## $CARRY - OUT = A B \overline{C} + A \overline{B} C + A B C + \overline{A} B C$

The carry-out expression can be simplified as shown below:

$$CARRY - OUT = A B C + A B C + A B C + A B C$$

$$= \mathbf{A} \mathbf{B} \mathbf{C} + \mathbf{A} \mathbf{B} \mathbf{C} + \mathbf{B} \mathbf{C} (\mathbf{A} + \mathbf{A})$$

$$= \mathbf{A} \mathbf{B} \overline{\mathbf{C}} + \mathbf{A} \overline{\mathbf{B}} \mathbf{C} + \mathbf{B} \mathbf{C}$$

$$= \mathbf{A}\mathbf{B}\mathbf{C} + \mathbf{C}(\mathbf{A}\mathbf{B} + \mathbf{B})$$

$= AB\overline{C} + C(A\overline{B} + B)$

$$= \mathbf{A} \mathbf{B} \mathbf{\overline{C}} + \mathbf{A} \mathbf{C} + \mathbf{B} \mathbf{C}$$

$$= \mathbf{B} \left( \mathbf{A} \,\overline{\mathbf{C}} + \mathbf{C} \right) + \mathbf{A} \,\mathbf{C}$$

$$= \mathbf{B} (\mathbf{A} + \mathbf{C}) + \mathbf{A} \mathbf{C}$$

$$= \mathbf{A}\mathbf{B} + \mathbf{A}\mathbf{C} + \mathbf{B}\mathbf{C}$$

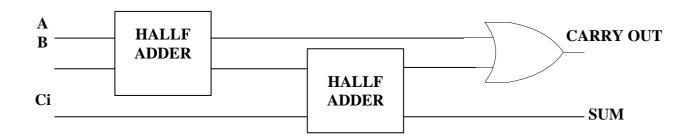

It is more common practice to construct a full adder using two-half adder, and OR gate. The basic technique is shown in Fig. (1).

## **Procedure**

- 1. Referring to the truth table (1) shown in the theory, implement a half adder circuit.

- 2. Referring to the truth table (2) shown in the theory, implement a full adder circuit.

- 3. What modification to the adder circuit are necessary to able to performed binary half-subtract?

Connect this circuit and find it's truth table.

4. Design a full subtract circuit and find it's truth table.

## **Discussion**

- 1. Explain how can you implement the half and full adder without using XOR gates, show the logical circuit and compare with one you have used.

- 2. With the aid of logic circuit, design an adder to add two-three bit binary numbers.

- 3. Discuss the methods used to speed up addition.

- 4. Design a half adder/subtract circuit. Using control line (Z), when Z = 1 we get half adder, and when Z = 0 we get half subtract.

| Α | В | SUM | CARRY OUT |

|---|---|-----|-----------|

| 0 | 0 | 0   | 0         |

| 0 | 1 | 1   | 0         |

| 1 | 0 | 1   | 0         |

| 1 | 1 | 0   | 1         |

# Table (1)Truth Table of Half Adder.

| Α | В | CARRY IN (Ci) | SUM | CARRY OUT (Co) |

|---|---|---------------|-----|----------------|

| 0 | 0 | 0             | 0   | 0              |

| 0 | 0 | 1             | 1   | 0              |

| 0 | 1 | 0             | 1   | 0              |

| 0 | 1 | 1             | 0   | 1              |

| 1 | 0 | 0             | 1   | 0              |

| 1 | 0 | 1             | 0   | 1              |

| 1 | 1 | 0             | 0   | 1              |

| 1 | 1 | 1             | 1   | 1              |

# $SUM = A \oplus B \oplus C$ CARRYOUT = A B + A C + B C

Table (2)Truth Table of Full Adder

Fig. (1) Full Adder Using Two Half Adder.

Exp. No. (4)

#### **Decoders and Encoders**

## **Object**

To be familiar with basics of conversion from binary to decimal by using decoder networks.

## **Theory**

## 1. <u>Decoder</u>

The process of taking some type of code and determining what it represents in terms of a recognizable number or character is called decoding. A decoder is a combinational logic circuit that performs the decoding function, and produce an output that indicates the (meaning) of the input code.

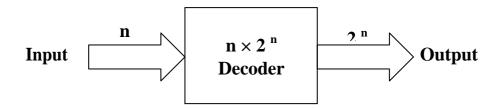

The decoder is an important part of the system which selects the cells to be read from and write into. This particular circuit is called a decoder matrix, or simply a decoder, and has a characteristic that for each of the possible  $2^n$  binary input number which can be taken by the n input cells, the matrix will have a unique one of its  $2^n$  output lines selected.

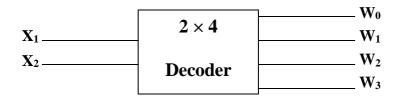

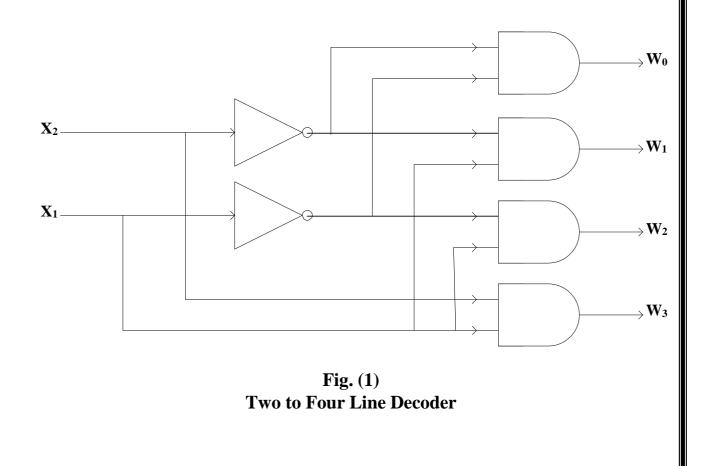

The decoder is called n to m where  $m < 2^n$  for example two to four line decoder, Fig. (1) shows a two to four line decoder and its truth table.

| INP            | UTS            | OUTPUTS        |                |       |                       |  |  |

|----------------|----------------|----------------|----------------|-------|-----------------------|--|--|

| X <sub>2</sub> | $\mathbf{X}_1$ | $\mathbf{W}_0$ | $\mathbf{W}_1$ | $W_2$ | <b>W</b> <sub>3</sub> |  |  |

| 0              | 0              | 1              | 0              | 0     | 0                     |  |  |

| 0              | 1              | 0              | 1              | 0     | 0                     |  |  |

| 1              | 0              | 0              | 0              | 1     | 0                     |  |  |

| 1              | 1              | 0              | 0              | 0     | 1                     |  |  |

Table (1)Two to Four Decoder Truth Table

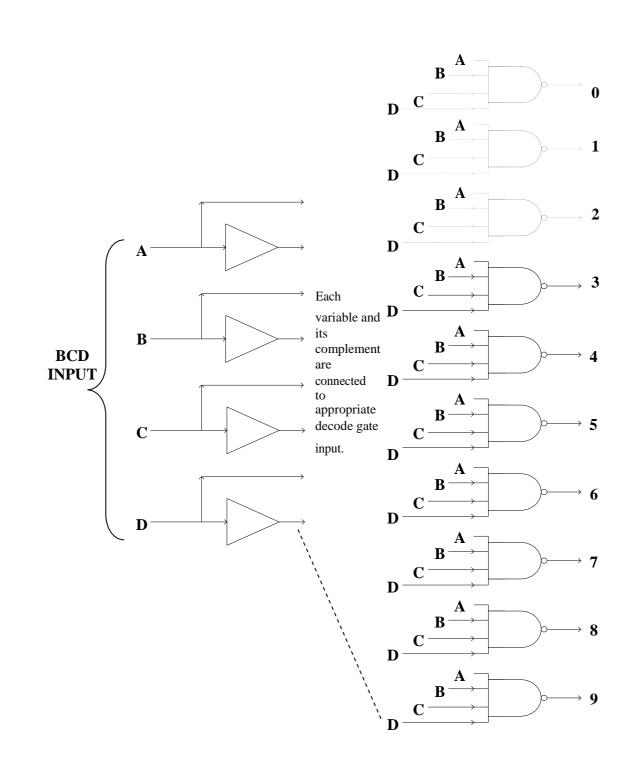

#### The BCD Decoder

The BCD decoder converts each BCD code (8421) into one of ten possible decimal digit indications. It is typically referred to as a 1 of 10 or 4 to 10 lines decoder, although other types of decoder also fall into this category (such as an Execs – 3 decoder). A list of the ten BCD code words and their corresponding decoding functions is shown in Table (2). Each of these decoding functions is implemented with NAND gates to provide active LOW outputs, as shown in Fig. (2).

| DECIMAL |   |   |   | C | )UTI | LOGIC FUNCTION |   |   |   |   |                                                                  |

|---------|---|---|---|---|------|----------------|---|---|---|---|------------------------------------------------------------------|

| DIGIT   | 0 | 1 | 2 | 3 | 4    | 5              | 6 | 7 | 8 | 9 | (X)                                                              |

| 0       | 0 | 1 | 1 | 1 | 1    | 1              | 1 | 1 | 1 | 1 | <b>DCBA</b>                                                      |

| 1       | 1 | 0 | 1 | 1 | 1    | 1              | 1 | 1 | 1 | 1 | <b>DCBA</b>                                                      |

| 2       | 1 | 1 | 0 | 1 | 1    | 1              | 1 | 1 | 1 | 1 | <b>DCBA</b>                                                      |

| 3       | 1 | 1 | 1 | 0 | 1    | 1              | 1 | 1 | 1 | 1 | <b>DCBA</b>                                                      |

| 4       | 1 | 1 | 1 | 1 | 0    | 1              | 1 | 1 | 1 | 1 | $\overline{\mathbf{D}}\mathbf{C}\overline{\mathbf{B}}\mathbf{A}$ |

| 5       | 1 | 1 | 1 | 1 | 1    | 0              | 1 | 1 | 1 | 1 | <b>DCBA</b>                                                      |

| 6       | 1 | 1 | 1 | 1 | 1    | 1              | 0 | 1 | 1 | 1 | <b>DCBA</b>                                                      |

| 7       | 1 | 1 | 1 | 1 | 1    | 1              | 1 | 0 | 1 | 1 | DCBA                                                             |

| 8       | 1 | 1 | 1 | 1 | 1    | 1              | 1 | 1 | 0 | 1 | DCBA                                                             |

| 9       | 1 | 1 | 1 | 1 | 1    | 1              | 1 | 1 | 1 | 0 | DCBA                                                             |

## Table (2)Truth Table of BDC to Decimal Decoder

The 7442 is an integrated circuit BCD to Decimal decoder. Note that on this device the inputs are A, B, C, and D where A is the least significant bit.

Fig (2) Logic for BCD Decoder.

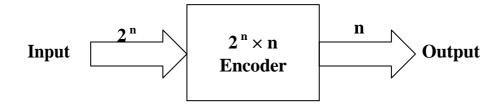

## 2. <u>Encoder</u>

An encoder is a combinational logic circuit that generate n output lines from  $2^n$  (or less) inputs. It has the reverse function of the decoder.

An encoder accepts digit on its inputs, such as a decimal or octal digit, and converts it to a coded output, such as a binary or BCD. Encoder can also be devised to encode various symbol and alphabetic characters. This process of converting from familiar symbols or numbers to a coded format is called encoding.

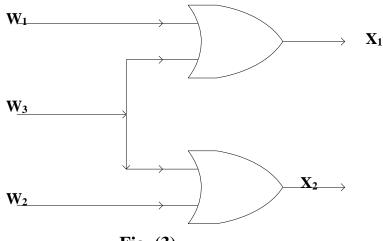

Figure (2) shown a four to two line encoder and its truth table.

|                | INP   | OUT            | PUTS  |   |   |

|----------------|-------|----------------|-------|---|---|

| W <sub>3</sub> | $W_2$ | X <sub>2</sub> | $X_1$ |   |   |

| 0              | 0     | 0              | 1     | 0 | 0 |

| 0              | 0     | 1              | 0     | 0 | 1 |

| 0              | 1     | 0              | 0     | 1 | 0 |

| 1              | 0     | 0              | 0     | 1 | 1 |

Table (3)Truth Table of Four to Two Line Encoder.

Fig. (3) Four to Two line Encoder

#### **Procedure**

- 1. Construct a circuit as shown in Fig. (1), set data switches as shown in the two to four lines decoder output table. Record the output indications of  $L_1$  to  $L_4$ .

- Install one 7442 BCD to Decimal Decoder in the logic lab. breadboard. Set data switches as shown in the BCD to Decimal Decoder output

table in Fig. (2). Record the output indications output pins.

3. Construct the circuit as shown in Fig. (3), set data switches as shown in the four to two line encoder truth table. Record the output indications of  $L_1 \& L_2$ .

#### **Discussion**

- 1. Design a full adder circuit using decoder.

- 2. Design  $3 \times 8$  decoder from  $2 \times 4$  decoder.

- 3. Design  $4 \times 16$  decoder from  $3 \times 8$  decoder.

- 4. Design octal to binary encoder.

## Exp. No. (5)

#### Multiplexer and Demultiplexer

## <u>Object</u>

To demonstrate a basic Multiplexer / Demultiplexer system, and become familiar with different types of multiplexer and demultiplexer.

## **Theory**

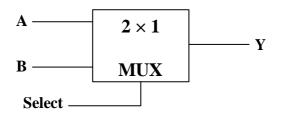

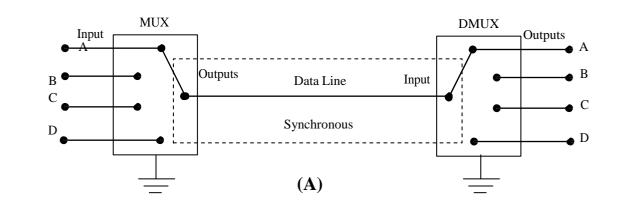

## 1. <u>Multiplexer</u>

It is not necessary to use only discrete gates (AND, OR, NAND, NOR, EXOR, EXNOR) in the design of the combinational logic circuit, with the availability of the medium scale integrated (MSI) and large scale integrated (LSI), it is possible to design a very complicated circuits with a simple procedure, for example it is waste of time in most cases to try to minimize combinational logic circuit which has eight input using tabular method, while it will simpler if we used multiplexers.

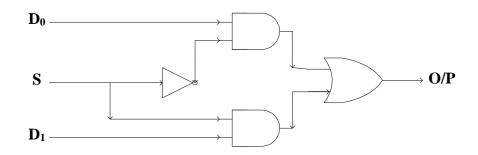

A multiplexer is a network that has many inputs and one output, and the value of the output will be the value of one of inputs which will be decided by some select lines. The simplest type of multiplexer is the two line to one line data multiplexer. Let A be one of the inputs and B is the other input and Y is the output as in Fig. (1), and S is the select line, then

Fig. (1) Two to One Line Multiplexer

Y = A if Select = 0. Y = B if Select = 1.

The logic circuit diagram of the Two to One line Multiplexer is shown in Fig. (2).

There are many 2 to 1 data selectors as a MSI, for example (7498, 74157, 74158) which contains four (quadruple) two-to-one data selectors in one chip.

There are other types of multiplexers 4-to-1 line, 8-to-1 line, and 16-to-1 line multiplexer, and the number of select lines of these multiplexer are 2, 3, and 4 lines respectively. Fig.(3) shows the four to one line multiplexer and its function block diagram.

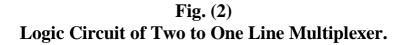

To use the multiplexer in the design of combinational logic circuit, usually the truth table of K-map of function is used in which the table or the map is divided into 2, 4, 8, or 16 equal parts according to the type of multiplexer used. Some of the inputs of the combinational circuit is connected directly to the select lines while data lines of the multiplexer will be a function to the other inputs according to the sun map or sub tables.

#### Example:

Design the following expression using multiplexer.

## $F(A,B,C) = \overline{A}C + \overline{B}C + AB\overline{C}$

#### Solution:

Number of variables = 3, it is better to use 4-to-1 line multiplexer, i.e.:

Number of selection lines = Number of variable -1.

The truth table of the function is shown below:

Y

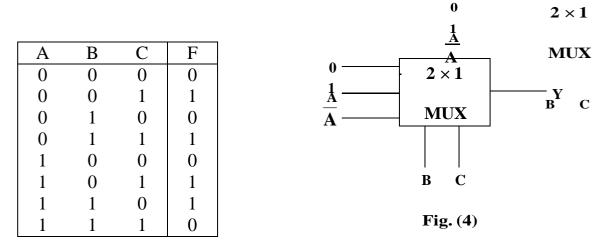

#### 2. <u>Demultiplexer</u>

A demultiplexer basically reverses<sup>4</sup> the multiplexing function. It is take data from one line and distribute them to given number of output lines. Fig. (3) shown a one to four line demultiplexer circuit. The input data line goes to all of the AND gates. The two select lines enable only one gate at a time and the data appearing on the input line will pas through the selected gate to the associated output line.

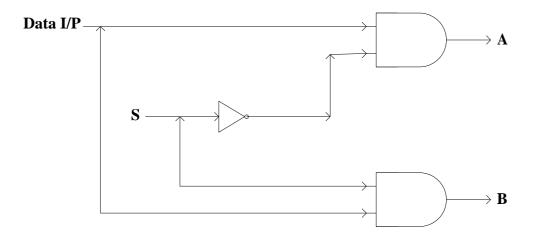

The simplest type of demultiplexer is the one to two lines DMUX. as shown in Fig. (5).

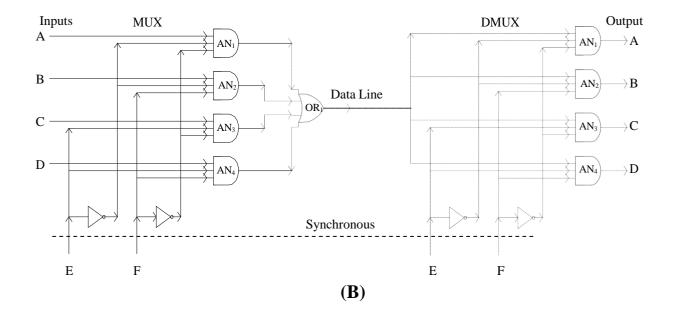

Fig. (3) MUX/DMUX System: (A). Switch Analog. (B). Logic Gate Circuit .

Fig. (5) One to Two Lines Demultiplexer

#### **Procedure**

- 1. Connect the circuit as shown in Fig. (2).

- Apply a signal to (A) input from clock (High Speed) of the logic INTIKIT unit. Draw the wave form.

- 3. Apply signal to (B) input from the pulse generator of amplitude = 5 Volt (p-

p) frequency = 50 KHz. Draw the wave form.

- 4. Set the selector control input (S = 0), draw the output waveform from the multiplexer.

- 5. Set S = 1, draw the output waveform of the multiplexer.

- 6. Connect the output of MUX to the DMUX circuit of Fig. (5) and find the output of demultiplexer when S = 0 and when S = 1.

#### **Discussion**

- 1. Construct  $8 \times 1$  MUX by using  $2 \times 1$  MUX.

- 2. Construct  $16 \times 1$  MUX by using  $4 \times 1$  MUX and  $2 \times 4$  Decoder.

- 3. Give some applications for the Multiplexer.

- How many chips of 2×1 MUX you will need if you want to design 16×1 MUX.

- 5. Design the following expression using multiplexer:

## $F(A,B,C) = \overline{A}B + AC$

Put the selection circuit  $S_1$ ,  $S_0 = A C$ , A B, B C.

University of Technology Laser & Optoelectronics Engineering Department Digital Electronics lab .

## Exp. No. (6)

## Flip – Flops

## <u>Object</u>

- 1. To familiar the student with Flip-Flops.

- 2. To differentiate between various types of the Flip-Flops.

- 3. How to determine the next state of each type of Flip-Flops.

## **Theory**

A Flip-Flop (F-F) is a multivibrator which has two stable state (Bistable) High and Low. Flip-Flop (F-F) are useful devices for applications such as counting, storing binary data and data conversion from serial to parallel

There are many different types of Flip-Flops:

- 1. a) Simple Set-Reset (S-R) Flip-Flip.

- b) Clocked (S-R) Flip-Flop.

- 2. J-K Flip-Flop.

- 3. D-Type Flip-Flop.

- 4. T-Type Flip-Flop.

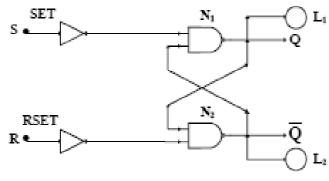

## 1. a) <u>The Set-Rest (S-R) Flip-Flop:</u>

Fig. (1) shows the basic construction of S-R F-F. It has two output called Q and  $\overline{\mathbf{Q}}$  and like the toggle switch, when it's (1) output is high, it's (0) output is low and vice-versa.

When the power is applied to the machine the F-F will go either to it's (Set) or (Reset) state. The initial state is arbitrary depending on the relative characteristics of the components which comprise the two logic gates.

Fig. (1-b) shows the meaning of Set and Reset states in terms of binary voltage levels. To see how F-F operates, refer to Fig. (1-a), Assume that the initial state is the (Set) state ( $L_1$  ON and  $L_2$  OFF), and that both the Set and Reset lines are low (0). The Set and Reset lines are both stable when they are low. In the Set state gate N<sub>1</sub> provides a high level to upper inputs of the N<sub>2</sub>. Therefore, both input to N<sub>2</sub> are high causing it to produce a low output which turns L<sub>2</sub> OFF. The low output of N<sub>2</sub> is also applied to the lower input terminal of N<sub>1</sub>. This produces a high output from gate N<sub>1</sub>, turning L<sub>1</sub> ON. In the set state then, N<sub>2</sub> is continually enabling N<sub>1</sub>, and N<sub>1</sub> continually disabling N<sub>2</sub>.

The two gates are latched in a condition that will remain until the input conditions on the S-R lines are changes.

If the F-F is initially in the Reset state ( $L_2$  ON and  $L_1$  OFF), in this case  $N_1$  is continually enabling  $N_2$  and  $N_2$  is continually disabling  $N_1$ . The circuit is again latched output but in the opposite direction.

Apply a high to the S terminal with the F-F in the Reset state ( $L_2$  ON and  $L_1$  OFF) at this case the output  $N_1$  go to High, reversing the latch condition of the previous case. If a high is then applied to the R terminal, the latch condition is reverses again (i.e. the  $L_1$  is OFF and  $L_2$  is ON).

The truth table for the S-R F-F is shown in Fig.(1-b). As the first line of the truth table shows no change (N.C.) occur in the F-F state if both S and R lines are Low (0).

The second line shows the input conditions needed to cause the F-F to go to the Reset state.

The third line of the truth table shows the input condition needed to cause the F-F to go to the Set State.

The fourth line shows a set of "illegal" input conditions which are usually avoided by the machine designer.

The F-F cannot "remember" this state. Since the primary value of the F-F is in its memory capability. The "illegal" input-output situation can be ignored.

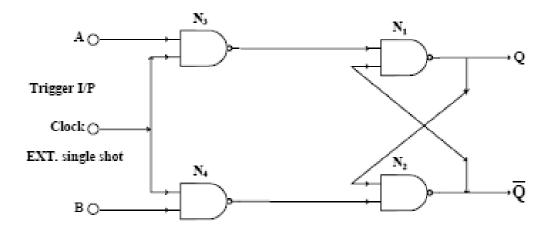

#### 1. b) <u>The Clocked Set-Rest ( Clock S-R) Flip-Flop:</u>

It is also called Steered S-R Flip-Flop. When a F-F is used, it is frequently desirable to establish the desired Set or Rest state first, then have it go to that state at some later point in time.

The process of pre-establishing the desired state is called (Steering).

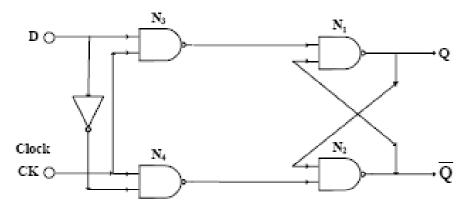

Fig.(2) shows a simple form of clocked S-R F-F. It is the same S-R F-F of Fig.(1-a) except that a steering network comprised of additional logic gates ( $N_3$  and  $N_4$ ) has been added to the input circuit. The input levels at steering terminals A and B cannot by themselves change the state of the F-F. A "trigger" or "clock" pulse or EXT. signal shot must be applied. When this occurs, the F-F will go to the state directed by the HIGH-LOW conditions at the steering terminal. If A is High when the clock pulse is applied, gate  $N_4$  will be enabled. This provide a low level to  $N_2$  switching the F-F to the reset state.

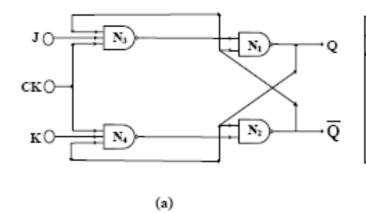

#### 2. <u>The J-K Flip-Flop:</u>

The J-K F-F combines the capability of the S-R and clocked S-R Flip-Flops into a single element. Fig.(4-a) shows the combination of the J-K F-F, and Fig. (4-b) shows the truth table of the J-K F-F.

#### 3. <u>D-Type Flip-Flop:</u>

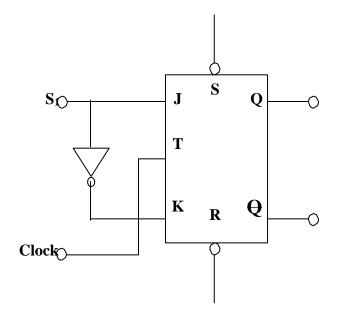

A D-type Flip-Flop can constructed from the S-R F-F as shown in Fig. (3) and from J-K F-F as shown in Fig.(6).

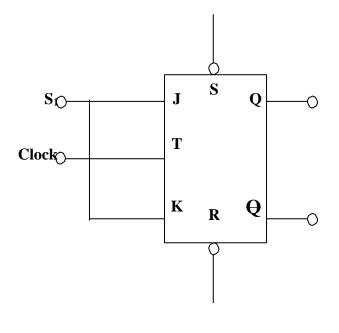

#### 4. <u>T-Type Flip-Flop:</u>

A T-type F-F can be constructed from the J-K F-F as shown in Fig. (7).

#### **Procedure:**

1. Hook up the simple S-R F-F circuit shown in Fig. (1-a) by using integrated circuit (I.C) type ------ and state it's truth table.

#### <u>Note:</u>

Logic (1) = +5 Volt = + VCC = HIGH.

Logic(0) = 0 Volt = GND = LOW.

- 2. Hook up the steering circuit for the clock S-R F-F of Fig.(2) and determine the next state truth table when:

- a. Clock equal to zero (GND) (Logic 0).

- b. Clock equal to + VCC (Logic 1).

- 3. Hook up D-type F-F in Fig. (3) by using (I.C.), type ------ with clock terminal set to EXT signal shot, when D in it's low position (GND). State the output Q, and when D in it's high position (+VCC) state the output Q.

- 4. Hook up J-K F-F shown in Fig.(5-a) and determine the output of the truth table of Fig. (5-b) by using (I.C.) type ------.

- 5. Hook up the circuit shown in Fig. (6) D-type F-F by using (I.C.) type ----------- and state it's truth table.

- 6. Repeat step 5 for Fig. (7) T-type F-F.

#### **Discussion:**

- 1. For the simple S-R F-F try to implement the same F-F using two NOR gates, give it's truth table.

- 2. What is the advantage of using J-K F-F over other types of Flip-Flops.

- Give an electronic circuit using discrete components i.e. transistors. Diodes and resistors for J-K F-F.

- 4. From the clocked S-R F-F, show how can you form D-type and T-type Flip-Flops.

| I/ | Р | 0   | /P  |

|----|---|-----|-----|

| S  | R | Q   | Q   |

| 0  | 0 | N.C | N.C |

| 0  | 1 | 0   | 1   |

| 1  | 0 | 1   | 0   |

| 1  | 1 | 1   | 1   |

Fig. (1-a) S-R Flip-Flop Construction.

Fig. (1-b) Truth Table of S-R Flip-Flop .

Fig. (2) Steering Circuit or Clocked S-R Flip-Flop.

Fig. (3) D-Type Flip-Flop Construction.

| I/ | Р | 0    | )/P    |

|----|---|------|--------|

| J  | Κ | Q    | State  |

| 0  | 0 | N.C. | N.C.   |

| 0  | 1 | 0    | Reset  |

| 1  | 0 | 1    | Set    |

| 1  | 1 | *    | Toggle |

\* Mean either 1 or 0 (b)

Fig. (4) (a): J-K F-F Construction. / (b): J-K F-F Truth Table.

| 1       |   | I/P E | Before C | lock |   | O/P Afte | r Clock |

|---------|---|-------|----------|------|---|----------|---------|

|         | s | R     | J        | K    | Q | Q(n+1)   | State   |

|         | 1 | 1     | 0        | 0    | 0 |          |         |

| 0JQO    | 1 | 1     | 0        | 0    | 1 |          |         |

| ск      | 1 | 1     | 0        | 1    | 0 |          |         |

| Ŭ T     | 1 | 1     | 0        | 1    | 1 |          |         |

|         | 1 | 1     | 1        | 0    | 0 |          |         |

| oK_R Q○ | 1 | 1     | 1        | 0    | 1 |          |         |

|         | 1 | 1     | 1        | 1    | 0 |          |         |

|         | 1 | 1     | 1        | 1    | 1 |          |         |

| (a)     |   |       |          | (b)  |   |          |         |

Fig. (5) (a): J-K F-F Chip. / (b): J-K F-F Truth Table.

University of Technology Laser & Optoelectronics Engineering Department Digital Electronics lab .

# Exp. No. (7)

### **Digital Counter**

### <u>Object</u>

After completing this experiment, you will able to:

- 1. Build and analyze various a synchronous up and down counter.

- 2. Change the model of the counter.

- 3. Use an IC counter and determine how the truncate its count sequence.

### **Theory**

Digital counter are classified as synchronous or asynchronous, dependent on how they are clocked.

Synchronous counters are a series of Flip-Flops, each clocked at the same time, causing the outputs of the stages (Flip-Flops) to change together. By contrast, asynchronous counters are a series of Flip-Flops, each clocked by the previous stage, one after the other.

Since all stages of the counter are not clocked together, a "ripple" effect propagates as various Flip-Flops are clocked. For this reason, asynchronous counters are called ripple counters. You can easily make a ripple counter from D or J-K Flip-Flops by connecting them in a toggle mode. The modulus of a counter is the number of different output states the counter may take. You can change the modulus of ripple counter by decoding any output state and using the decoded state to synchronously preset or clear the current count. Ripple counters can be made to count either up or down (it can be made to count both up and down, but usually it is easier to use a synchronous counter for an up/down counter).

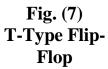

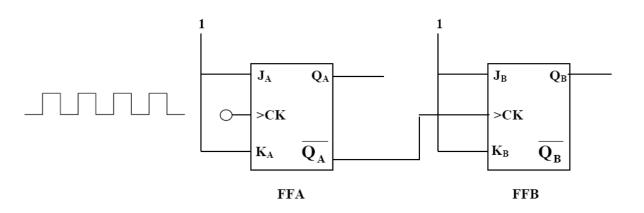

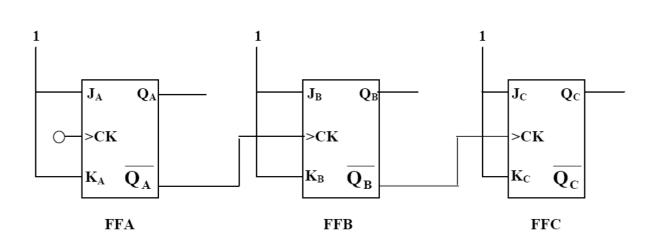

Fig. (1) shows a two-stage counter connected for asynchronous operation, notice that the clock line is connected to the clock (CK) input of only the first stage, FFA. The second stage, FFB, is triggered by the Q<sub>A</sub> output of FFA. FFA changes state at the positive-going edge of each clock pulse, but FFB change only when triggered by a positive-going transition of the Q<sub>A</sub> output of FFA.

Fig. (2) shows the timing diagram of QA and QB outputs.

Fig. (1) Two Stage Asynchronous Binary Counter.

Fig. (2) Timing Diagram For The Counter Of Fig. (1).

A three-stage asynchronous binary counter is shown in Fig. (3-a). The basic operation is the same as that of the two-stage counter just discussed, except that it has eight states due to its three states. A timing diagram appears in Fig. (3-b) for eight clock pulse.

| Clock Pulse | QC | QB | QA |

|-------------|----|----|----|

| 0           | 0  | 0  | 0  |

| 1           | 0  | 0  | 1  |

| 2           | 0  | 1  | 0  |

| 3           | 0  | 1  | 1  |

| 4           | 1  | 0  | 0  |

| 5           | 1  | 0  | 1  |

| 6           | 1  | 1  | 0  |

| 7           | 1  | 1  | 1  |

Table (1) State Table for a Three-Stage Binary Counter.

Fig. (3-a) Three-Stages Asynchronous Counter.

| CK-              |   | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|------------------|---|---|---|---|---|---|---|---|---|

| Q <sub>A</sub>   | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| Q <sub>B</sub> _ | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| <b>Q</b> c _     | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

Fig. (3-b) Timing Diagram of Three-Stage Asynchronous Counter.

Notice that the counter progress through a binary count of 0 to 7 and then recycles to the 0 state.

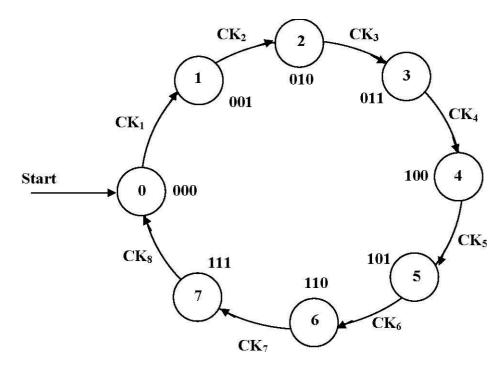

This counter sequence is presented in the state diagram shown in Fig. (4).

Fig. (4) State Diagram For A Three-Stage Binary Counter.

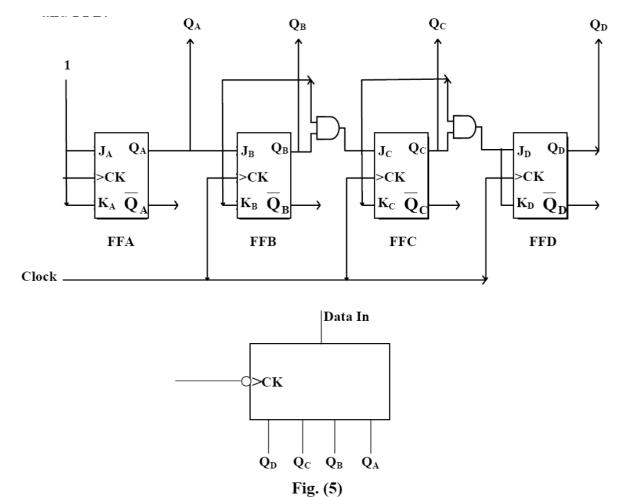

The synchronous counter is also called a parallel counter because the clock line is connected in parallel to each Flip-Flop. Notice that an arrangement different from that for the asynchronous counter. Fig. (5) shows a four-stage binary counter and its equivalent logic symbol.

This circuit can be connected by using IC 74163 which has several futures in addition to basic functions previously discussed for the general synchronous binary counter. First, the counter can be preset to any for-bit binary number by applying the proper levels to the data inputs.

The circuit below is a 4-bit synchronous binary counter. The J and K inputs of FFA are connected to HIGH. FFB has its J-K inputs connected to the output of FFA, and the J-K inputs of FFC are connected to the output of an AND gate that is fed by the outputs of FFA and FFB, also the J-K inputs of FFD are connected to the output of AND gate that is fed by the output of FFC and FFB.

A Four-Stage Synchronous Binary Counter.

#### **Decade Counter**

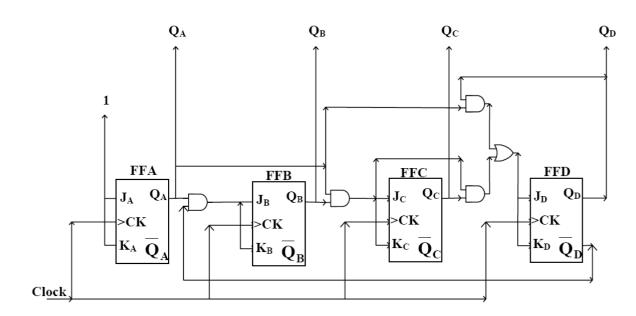

Decade counters are very important category of digital counter because of their wide application, a decade counter has ten states in its sequence that is, it has modulus of ten. It consist of four stages and can have any given sequence of states as long as there are ten. A very common type of decade counter is the BCD (8421) counter, which exhibits a binary-coded-decimal sequence as shown in Table (2).

As you can see, the BCD decade counter goes through a straight binary sequence through the binary 9 state, rather than going to the binary 10 state, it recycles to the 0 state. A synchronous BCD decade counter is shown in Fig. (6).

| СК | QD | QC | QB | QA |

|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  |

| 1  | 0  | 0  | 0  | 1  |

| 2  | 0  | 0  | 1  | 0  |

| 3  | 0  | 0  | 1  | 1  |

| 4  | 0  | 1  | 0  | 0  |

| 5  | 0  | 1  | 0  | 1  |

| 6  | 0  | 1  | 1  | 0  |

| 7  | 0  | 1  | 1  | 1  |

| 8  | 1  | 0  | 0  | 0  |

| 9  | 1  | 0  | 0  | 1  |

Table (2) States Of BCD Decade Counter

Fig. (6) BCD Synchronous Decade Counter

#### **<u>Up-Down Counters</u>**

An up-down counter is one that is capable of progressing in either direction through a certain sequence. An up-down counter some time called a bidirectional counter and can have any specified sequence of states.

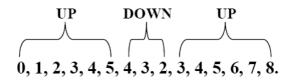

In general, most up-counters can be reversed at any point in their sequence. For example the following sequence:

#### **Procedure**

- 1. Connect the circuit shown in Fig. (1) and find the truth table and its timing diagram.

- 2. Connect the circuit shown in Fig. (3-a) and find it's truth table and the timing diagram.

- 3. Use 74163 to design a four-stage synchronous counter, and find it's truth table and timing diagram.

- 4. Use 74190 to design the BCD up/down counter, then find it's truth table and timing diagram for BCD up counter.

- 5. Design parallel counter (Up/Down) using J-K F-F for the following sequence (3, 4, 5, 6, 7, 4, 3, 2).

#### **Discussion**

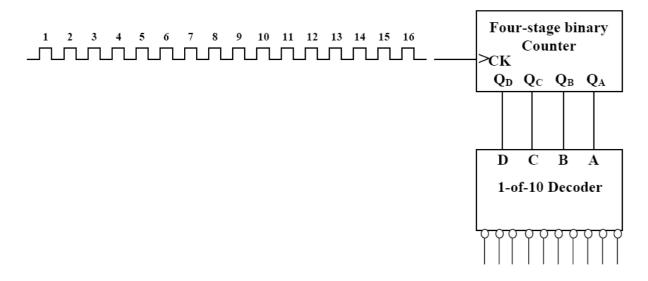

1. For the four-stage binary counter connected to the 1-of-10 decoder in Figure below, determine each of the decoder output wave form in relation to the clock pulses. QA is the LSB of counter, and A is LSB of decoder.

Given a BCD decade counter, show the decoding logic required to decade each the following states and how it should be connected to the counter. A HIGH output indication is required for each decade state.

MSB is to the left.

(a). 0101 (b). 0111 (c). 1000

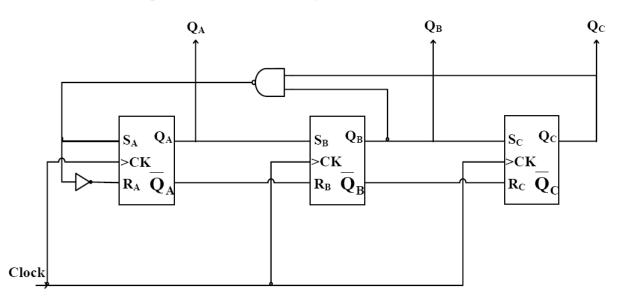

3. Determine the sequence of the following counter:

- 4. What are the applications of counter?

- 5. Design a counter that counts the following sequence: (1, 3, 5, 7, 9,

- 11) and repeat using J-K F-F.

# Exp. N0. (8)

The Shift Registers and There Applications

#### **Object**

- 1. To familiar the students with the shift register.

- 2. To make use of shift register in data transfer.

#### **Theory**

Any binary machine is said to have a particular "Word Length". These terms defines the number of bits required to represent data,

In other words, a machine which said to have a four-bit word length has its flip flops arranged in groups of four. The group of flip flops are consider as a single unit called a "Register".

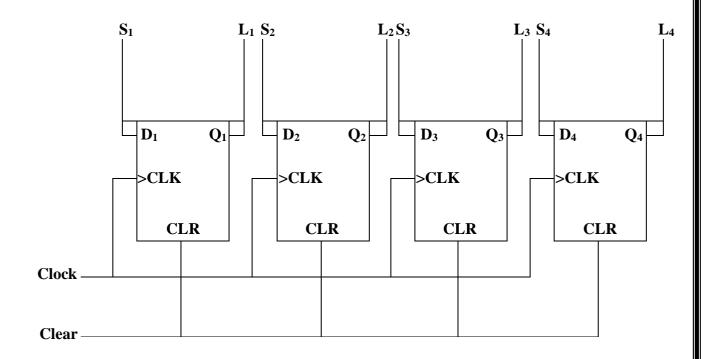

The binary number is "Shifted" one bit at time from one flip flop to the next. The device used in this type of transfer operation it called a "Shift Register"

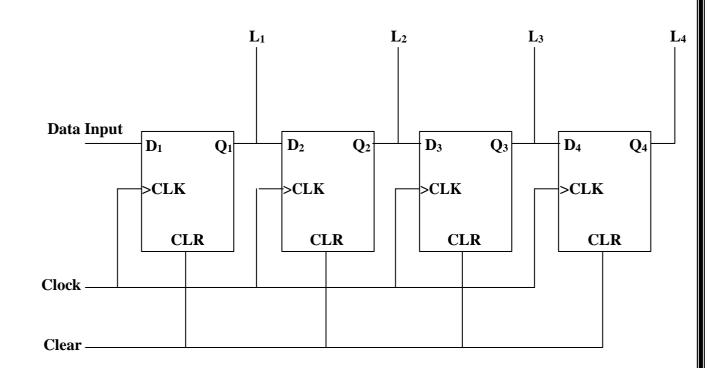

A shift register is a series of interconnected flip flops used for temporary storage of data as shown in Fig. (1). The output of one flip flop becomes the input of another, all the flip flops in the shift register have a common clock signal connection and all can be set or reset at the same time. Because the data were loaded to the circuit one bit after another and the shift register shifted them from one flip flop to another, this sequence is referred to as serial data loading and the circuit is called a "4-BIT SERIAL IN-SERIAL OUT SHIFT REGISTER" as shown in Fig. (1).

This type of shift register accepts digital data serially that is one bit at the time on one line. It produces the stored information on its output also in serial form.

The alternative to serial loading of the shift register is parallel loading, for a register with parallel data input, the bits are entered simultaneously into their respective stages on parallel-lines, rather than on a bit-by-bit basis on one line as with serial data inputs. Fig. (2) shows a "4 BIT PARALLEL IN-PARALLEL OUT REGISTER". In the parallel output register the output of each stage is available, once the data are stored, each bit appears on its respective output line and all bits are available simultaneously, rather than on a bit-by-bit basis as with the serial output.

If the data are loaded serially and read out in parallel, the shift register is functioning as a "SERIAL-TO-PARALLEL CONVERTER". If the data is loaded in parallel and shifted out serially, the shift register is functioning as a "PARALLEL-TO-SERIAL CONVERTER". Some shift registers are configured to allow shifting the data in both the right and left direction. These shift registers are usually called "Universal Shift Register", because they can shift data in either right or left direction, can load data either serially or in parallel and can output data either serially or in parallel.

#### **Procedure**

- 1. Connect the circuit as shown in Fig. (1) by using 74174 I.C.

- 2. To clear the register set the pin CLR to GND then to VCC.

- 3. Show how you can store binary number 1010 in this chip. Find the state of each flip flop after each clock pulse as shown in Table bellow and draw the timing diagram for this case.

| CLK | <b>D</b> <sub>1</sub> | <b>Q</b> <sub>1</sub> | Q <sub>2</sub> | <b>Q</b> <sub>3</sub> | <b>Q</b> <sub>4</sub> |

|-----|-----------------------|-----------------------|----------------|-----------------------|-----------------------|

| 0   | 0                     | 0                     | 0              | 0                     | 0                     |

| 1   | 1                     |                       |                |                       |                       |

| 2 | 0 |

|---|---|

| 3 | 1 |

| 4 | 0 |

4. Connect the circuit as shown in Fig. (2), show how you can store the binary number 011011 in this chip.

#### **Discussion**

- 1. What is the output binary number after 3-clock pulses if the number stored in the register is 1101, and D<sub>1</sub> is connected to GND (0).

- In Fig. (1) if the output Q<sub>4</sub> is returned to the D<sub>1</sub> input of flip flop 1, and the number stored in the register is binary 1101, what would be the output after 7-clock pulse?

- 3. Design 4-bit Parallel In-Serial Out shift register (PISO), using D-type Flip-Flop.

- 4. Design 3-bit Serial In-Parallel Out shift register (SIPO), using J-K Flip-Flop.

Fig. (1) Serial In – Serial Out Shift Register.

Fig. (2) Parallel In – Parallel Out Shift Register.

#### Exp no. (9)

### **Microprocessor Training Kit**

### **Object:-**

General description to Microprocessor training kit M85-0X .

### **Introduction:-**

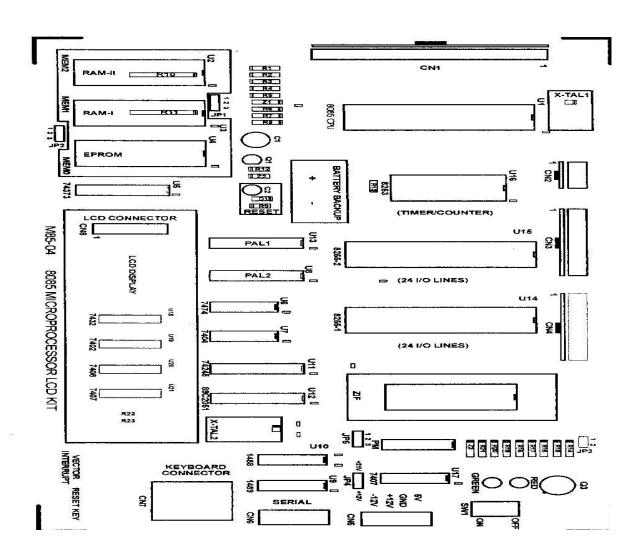

The M85-0x LCD Kit is a single board Microprocessor Training Kit based on 8085 Microprocessor, which is widely used to train engineers to develop software/hardware for any industrial process & control.

M85-0x LCD Kit provides powerful monitor EPROM & user RAM with Battery Backup as shown in figure (1). The kit has 101 IBM compatible PC keyboard & 20x2 LCD display for any Data entry / display.

This kit has line Assemble feature so that one can enter the program in Assemble language . The kit also has the capability of interacting with PC (computer) through RS-232C Serial link .

The input/output structure of M85-0x LCD kit provided 48 programmable I/O lines Using 2Nos. of 8255. It has got 16 bit 3channel programmable Timer/Counter using 8253.

The on board residents system monitor software is very powerful and provides various software utilities like INSERT, DELETE, BLOCK MOVE, RELOCATE, STRING, FILL&MEMORY COMPARE etc. which are very helpful in debugging/ developing The software.

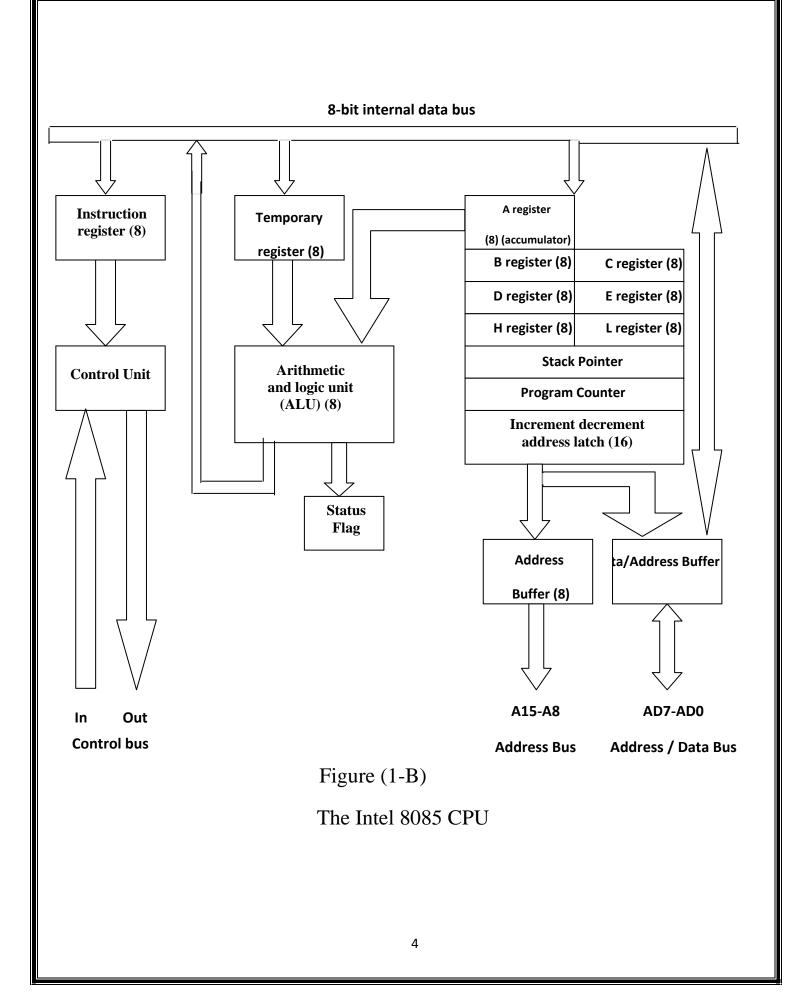

#### THE 8085 MICROPROCESSOR:

The 8085 represents the first generation of microprocessor chips. It is an 8 bit micro with 8 bit data bus, 16 bit address bus and a 6 bit control bus.

The data bus is used for the transfer of information between the micro chip and the rest of the system.

The address bus is used for addressing the required place of memory. Since the address bus is a 16 bit, then the maximum size of memory is  $(2)^{16}$ =64K byte of memory.

The control bus is composed of six signals to control the (Read/Write) of memory and (I/O) selection.

Internally the 8085 chip contain 8 bit accumulator, used as part of all arithmetic and logic operations performed by the microprocessor. The flag is an 8 bit register, but utilizing only five of the bits namely: zero, sign, carry, parity, and auxiliary carry. Also the 8085 contain six another 8 bit general purpose register, namely: B, C, D, E, H and L.

General purpose registers can be combined as register pairs – BC, DE, and HL – to perform some 16-bit operations. For register pair BC, register C can be determined as the low register and register B as the high. So that registers (D and E) and registers (H and L).

The Program Counter (PC) is 16 bit register used to point the location of the next program step to be executed. The Stack Pointer (SP) is also a 16 bit register used to point the location of the stack area in memory. The Processor Status Word (PSW), is another 16 bit register which comprises the accumulator and the flag register

(PSW: high byte=A, Low byte=Flag register).

Fig(1-a)

### \*Keyboard Description:-

The M85-0x LCD kit has 101 ASCII keys and 20x2 liquid Crystal Display to communicate with the outside world. As M85-0x LCD kit is switched on, a message "8085 LCD TRAINER KIT M85-0X\_" is displayed on the LCD display and all keys are in command mode.

### LIST OF ASCKII KEYBOARD COMMANDS

- 1. L :- list a memory block .

- 2. M :- Examine/Modify Memory .

- 3. E :- Enter a memory block .

- 4. R :- Examine /modify Register .

- 5. S :- Single Step.

- 6. G :- Go.

- 7. B :- Block Move .

- 8. I :- Insert.

- 9. D :- Delete .

- 10. N :- Insert Data .

- 11. O :- Delete Data .

- 12. F :- Fill .

- 13. H :- Relocate.

- 14. J :- Memory compare

- 15. K :- String

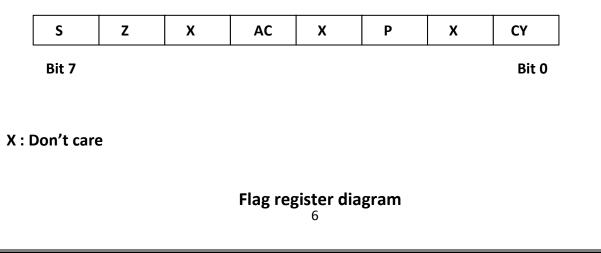

The flag register is affected by the result of arithmetic and logical operations

only. The structure of flag register is as follow:

### S (Sign flag):

This bit is set (logic 1) if the most significant bit of the result of an operation is "1" otherwise it is reset (logic 0).

### Z (Zero flag):

This bit is set if the content of the accumulator after an operation is zero, otherwise it is reset.

### CY (Carry flag):

This bit is set if an operation causes carry or borrow out of the most significant bit of the accumulator.

### AC (Auxiliary Carry):

This bit is set if there is a carry between the fourth and fifth bits of the accumulator.

### P (Parity flag):

This bit is set if the number of ones in the accumulator is even, otherwise it is reset.

### THE 8085 INSTRUCTION SET

The 8085 instruction set includes five different types of instructions.

1. Data Transfer Group:

Move data between registers or between memory and register.

2. Arithmetic Group:

Add, subtract increment or decrement data in registers or memory.

3. Logical Group:

AND, OR, EXCLUSIVE-OR, compare, rotate or complement data in registers or in memory.

4. Branch Group:

Conditional and unconditional jump instructions, subroutine call instructions and return instructions.

5. Stack, I/O, and Machine Control Group:

Includes I/O instructions, as well as instructions for maintaining the stack and internal control flags.

Note: only Arithmetic and logical instructions affected the flag register.

The 8085 can operate either on the internal CPU registers (A, B, C, D, E, H, & L) or in the system memory (RAM or ROM). The different addressing capabilities on the 8085 are:

a. Implied:

Meaning that the operation involves an operation on one of the registers. (E.g. ADD B, INR C).

b. Immediate:

Which involves an operation with a type supplied immediately after the instruction. (E.g. ADI 03, ORI 02).

c. Direct:

Which involves an operation with data sound on the address supplied as two bytes after the instruction. (e.g. LDA 2050, STA 2051).

### ASSEMBLY LANGUAGE PROGRAM

Examples of instructions:

| N<br>o | Instructio<br>n | Туре               | No.<br>of<br>Byte<br>s | Function           | Effect<br>on flags |

|--------|-----------------|--------------------|------------------------|--------------------|--------------------|

| 1      | MVI<br>rd,byte  | Data transfer      | 2                      | rd=byte            | None               |

| 2      | MOV rd,rs       | Data transfer      | 1                      | rd=rs              | None               |

| 3      | INR r           | arithmetic         | 1                      | r=r+1              | All but<br>CY      |

| 4      | DCR r           | arithmetic         | 1                      | r=r-1              | All but<br>CY      |

| 5      | HLT             | Machine<br>Control | 1                      | Stop<br>processing | None               |

| 6      | RST5            | Restart            | 1                      | Pc=0008            | None               |

r: register (8-bit)

rd: destination register (8-bit)

rs: source register (8-bit)

Assembly language programs are written in a standard format as follows:

| <u>Address</u> | Hexcode   | Label  | <b>Opcode</b> | Operand | <u>Comment</u>           |

|----------------|-----------|--------|---------------|---------|--------------------------|

| 2000           | <i>3E</i> | START: | MVI           | A, 03   | ; A=3                    |

| 2001           | 03        |        |               |         |                          |

| 2002           | 3C        |        | INR           | А       | ; A=A+1=4                |

|                |           |        |               |         | ; S=0, Z=0, Ac=0,<br>P=0 |

| 2003           | EF        |        | RST5          |         | ; End                    |

The address field specifies the address of the respective instruction.

Language program. This field contains the data to be entered to the machine. The label field specifies the label for the program.

Opcode field specifies the 8085 instructions to be executed.

Operand field specifies the data to be operated by the corresponding instruction. Comment field is an optional field used to comment lines.

#### Memory Modification and Program Entry:

**Reset** key is used to reset the system.

**M** key from keyboard is used to locate memory location to examine or modify its contents.

**ENTER** key from keyboard is used to store the display data byte in memory and go to the next memory Location and display its contents.

DOT (.) key from keyboard is used to start execution or to terminate program

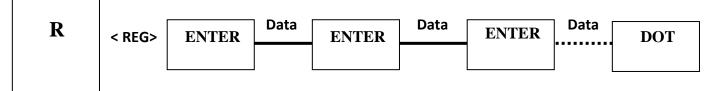

| PRESS | Address | ENTER | Data | ENTER | Data | ENTER | Data | DOT |

|-------|---------|-------|------|-------|------|-------|------|-----|

| Μ     |         |       | 1    |       | 2    |       | n    |     |

e.g. Suppose we want to enter the following values in the computer:

| 2000 | 3E, | MVI  | А, | 3 |

|------|-----|------|----|---|

|      | 03  |      |    |   |

| 2002 | 3C  | INR  | А  |   |

| 2003 | EF  | RST5 |    |   |

Then the following steps are to be performed:

| 1. | Press | Μ          |       |

|----|-------|------------|-------|

| 2. | Press | 2000       | ENTER |

| 3. | Press | <b>3</b> E | ENTER |

| 4. | Press | 03         | ENTER |

| 5. | Press | <b>3</b> C | ENTER |

| 6. | Press | EF         | ENTER |

| 7. | Press | DOT        |       |

In order to check the entries of the program, we do the following steps:

| 1. | Press | Μ     |       |

|----|-------|-------|-------|

| 2. | Press | 2000  | ENTER |

| 3. | Press | ENTER |       |

| 4. | Press | ENTER |       |

| 5. | Press | ENTER |

|----|-------|-------|

| 6. | Press | DOT   |

#### **Register Display and Modification:**

**R** key from keyboards used to display the contents of registers.

e.g. To display the contents of the register, do the following steps:

- 1. Press R key from keyboard .

- 2. Press A and ENTER, the contents of the acc. Is displayed.

- 3. Press ENTER, the contents of the register B is displayed.

- 4. Press ENTER, the contents of the register C is displayed.

Continuing in the same way, the contents of the registers D, E, F (flags), I (Interrupt mask), H, L, SPH, SPL, PCH and PCL will be displayed.

Note:- If you need to examine the register contents, terminates the program with

the instruction RST5 (machine code EF) instead of HLT (machine code 76). The RST

instruction stops the user's program and returns control of the computer to the

monitor program.

### **<u>Run and Single Step Modes:</u>**

**S** key is used to execute the program, one instruction at a time.

To execute a program in a single step mode, do the following:

e.g. To execute a program at address 2000. Do the following:

| 1. | Press | S     |       |

|----|-------|-------|-------|

| 2. | Press | 2000  | ENTER |

| 3. | Press | ENTER |       |

| 4. | Press | ENTER |       |

| 5. | Press | DOT   |       |

To run the program at address 2000, we use:

| G | Address | DOT |  |

|---|---------|-----|--|

|   |         |     |  |

**G** key Press from keyboard is used to locate memory location to start execution. To execute program at address 2000, do the following:

| 1. | Press | G    |     |

|----|-------|------|-----|

| 2. | Press | 2000 | DOT |

#### Lab work

#### Q) Shown below is a coding of a sample assembly program:

| <u>Address</u> | <u>Hexcode</u> | <u>Label</u> | <u>Opcode</u> | <u>Operand</u> | <u>Comments</u>       |

|----------------|----------------|--------------|---------------|----------------|-----------------------|

| 2000           | <i>3E</i>      | START:       | MVI           | A, 05          | ; A=5                 |

| 2001           | 05             |              |               |                |                       |

| 2002           | 3D             |              | DCR           | А              | ; A=A-1=4             |

|                |                |              |               |                | ; S=0, Z=0, Ac=0, P=0 |

| 2003           | 3D             |              | DCR           | А              | ; A=A-1=3             |

|                |                |              |               |                | ; S=0, Z=0, Ac=0, P=1 |

| 2004           | 3D             |              | DCR           | А              | ; A=A-1=2             |

|                |                |              |               |                | ; S=0, Z=0, Ac=0, P=0 |

| 2005           | EF             |              | RST5          |                | ; End                 |

- 1. Enter the above program in the memory.

- 2. Check the values of the entered program.

- 3. Run the program using single step command and check the values of the registers.

- 4. Run the program using direct run mode.

### Home Work

Write programs with effects

- 1. B=C+1 when C=50h.

- 2. Enter A=10 then decrement 4 from register A.

## Exp.no. (10)

# **Command Description**

# **Object:**

To explain the command description & understand what meaning each character in the keyboard.

# **Theory:**

The M85-0X LCD kit has 101 ASCII keys and 20x2 liquid crystal display to communicate with the outside word. As M85-0X LCD kit is switched on, a message "8085 LCD TRAINER KIT M85-0X" is displayed on the LCD display and all keys are in command mode.

### List of AskII keyboard commands

### > 1. memory block (L)

${\bf L}$  command dump specified memory block in the PC screen .

### **FORMAT**

### L low address, High address (.)

Type L followed by the starting address of the memory block to be listed , followed by a comma (,) and then the end address of the memory block followed by (.) dot

### **Example**

Suppose you want to list the data from 2000 to 2010 .

### L 2000,2010 (.)

| 2000 | 21 | 00 | 21 | 46 | AF | 23 | 86 | 05  | C2 | 05 |

|------|----|----|----|----|----|----|----|-----|----|----|

| 200A | 20 | 32 | 00 | 21 | FF | FF | FF | (.) |    |    |

## > 2.EXAMINE/MODIFY MEMORY (M)

The M command allows you to examine and modify memory locations individually.

The command functions as follows:

### <u>Format</u>

## M Address,(Data),....(.)

- Type M, followed by the hexadecimal address of the first memory location you wish to examine, followed by a space or comma.

- ✤ The contents of the location are displayed followed by a dash '-'.

- To modify the contents of the location displayed, type the new data , followed by a comma. The higher memory location will automatically be displayed as the step (2). A (.) at any stage terminates the command.

### **Example**

### M 2000, C3 - 3E, 23 - 01, FC - 06, 02, 21 - 80, 3E - EF (.)

The contents of 2000 to 2002 , 2004 & 2005 are changed from C3 to 3E , 23 to 01 , FC to 06 , 21 to 80 & 3E to EF respectively where as the data at 2003 remains as it is .

| Location | Old contents | New contents |

|----------|--------------|--------------|

| 2000     | C3           | 3E           |

| 2001     | 23           | 01           |

| 2002     | FC           | 06           |

| 2003     | 02           | 02           |

| 2004     | 21           | 80           |

| 2005     | 3E           | EF           |

### > 3.ENTER A MEMORY BLOCK (E)

E command allows user to enter a program or a block of data in the RAM.

### **Format**

### E address : data , data .....(.)

- Type E followed by the starting address of the memory block to be entered, followed by a colon (:).

- Each byte followed by a comma as it is entered from the SIOD is deposited in the consecutive location of the memory.

- In case the terminator is colon (:) the proceeding parameter is taken as a fresh address and the subsequent data bytes are stored in memory location starting from the fresh address.

- A (.) terminates the command.

### **Example**

E 2000 (enter)

2000: 3E, 01, 06, 02, 80, EF(.)

### > 4.EXAMINE/MODIFY REGISTER (R)

Display & modification of CPU register is accomplished via 'R' command.

### **Format**

####

| Register Identifier | Register            |

|---------------------|---------------------|

| А                   | Register A          |

| В                   | Register B          |

| С                   | Register C          |

| D                   | Register D          |

| E                   | Register E          |

| F                   | Flag byte           |

| Ι                   | Interrupt Mask      |

| Н                   | Register H          |

| L                   | Register L          |

| S                   | Stack Point MSB     |

| Р                   | Program Counter MSB |

Type 'R' Followed by a single alphabet register identifier . The contents may

now be changed if so desired. In case you do not want to modify the contents, Just enter a comma. The contents of the next register will be printed. The register identifiers for various CPU registers are given above.

### **Example**

RA-11,B-22,C-33

## > 5.SINGLE INSTRUCTIONS (S)

This command allows executing the program one instruction at a time.

## **Format**

S (Starting Address),

- Pressing of 'S' Key will list the PC and first byte of the program. In case one want to modify it, user has to entered the new address and then press comma. The new address will be listed. In this way one can execute the program in single instruction mode.

- This command can be terminated at any time by enter (.)

## **Example**

The following program is to be executed in single instruction mode:

| Address | Opcode | Instruction |

|---------|--------|-------------|

| 2000    | 3E 01  | MVI A,01    |

| 2002    | 06 02  | MVI B,02    |

| 2004    | 80     | ADD B       |

| 2005    | EF     | RST 5       |

On executing 'S' command S2000:3E/,2002:06/,2004:80/.if one wants to execute

Further, press enter otherwise one presses (.)

## ➢ 6.GO COMMAND (GO)

This command is used to execute the program in full clock speed. On pressing this key, the program counter contents are displayed. Enter the starting address of the program and press (.) key . The CPU will starts executing the program.

## **FORMAT**

The format for this command will be as follows:

G (Starting address) (.)

Pressing of 'G' Key will display the PC content and the first byte of the instruction.

To modify it, enter the desired address & then press comma, the PC will be modified

with new contents & the corresponding data will be listed . When (.) key is pressed,

CPU starts executing the program.

Suppose the program starts from 2000 then the format will be G 2000 (.)

## **EXAMPLE**

Execute the below sample program from 2000 location.

| Address | opcode | instruction |

|---------|--------|-------------|

| 2000    | 3E 01  | MVI A,01    |

| 2002    | 06 02  | MVI B,02    |

| 2004    | 80     | ADD B       |

| 2005    | EF     | RST 5       |

G 2000 (.)

## 7.Block move command (B)

This command allows to move the block of data from one memory location to another location. On pressing this key,'B\_'is displayed,type starting address, ending address of the block to be moved and enter the destination address and press (.) key. The format for the command is as follows:

## **FORMAT**

B(Starting address of the source),(End address of the source),(Starting address of the destination)(.)

## ▶ 8.Insert Command (I)

This command allows to insert one or more instructions in the user's program with automatic modification of the memory referenced instructions.On pressing this command,'I-'is displayed, enter the starting address of the program press (enter),enter the ending the byte or bytes are to be entered press (enter), enter the no.of bytes press (enter )enter the required data and press (.).When all the bytes are entered '8085 LCD TRAINER KIT M85-0X\_' is displayed . The format for this command is as follows:

## **FORMAT**

I (Starting address of the program),(End address of the program),(Addess from where the byte or bytes are to be entered),(No.of bytes),(Data),,(.)

## **EXAMPLE**

| Address | opcode | instruction |

|---------|--------|-------------|

| 2000    | 3E 01  | MVI A,01    |

| 2002    | 06 02  | MVI B,02    |

| 2004    | 80     | ADD B       |

| 2005    | EF     | RST 5       |

Now we want to insert three bytes at location 2005 (32 00 21) i.e. STA 2100 instruction.

I 2000,2005,2005,3,32,00,21,

Verify that the bytes have been inserted using examine memory command.

## ➢ 9.DELETE COMMAND (D)

This command allows to delete one or more instruction from the user program. In this command all the memory referenced instructions also get modified accordingly to keep the logic of the program.On pressing this command , D\_ is displayed , enter the starting address of the program press (enter) enter Ending address of the program press (enter) enter Ending address of the program press (enter) starting addresses from where the bytes are to be deleted press (enter) ending address till where the bytes are to be deleted and press(.)after that '8085 LCD TRAINER KIT M85-0X\_' is displayed. The format for this command is as follows:

## **FORMAT**

D(Starting address of the program),(End address of the program),(Starting address from where the bytes are to be deleted),(End address till where the bytes are to be deleted)(.).

# ▶ 10.FILL(F)

This command allows the user to fill amemory area(RAM)with aconstant data .

## **FORMAT**

F(Starting address of the program),(End address of the program),(Data to be filled)(.)

## EXAMPLE

Suppose the RAM area, from 2000 to 2010 is to be filled with FF.The format will be:

F 2000,2010,XX-FF(.)

Verify that the memory area from 2000 to 2010 is filled with constant data FF by using Examine memory command.

## ▶ 11.RELOCATE (H)

This command allows the user to relocate the program from one memory area to another memory area. The relocate command is somewhat different from Block Move command. This can be set to be the intelligent mode of Block Move command i.e. if user wants to execute a program from a different RAM area, this command will set the program as required. This can be understood clearly after working with the example given below.

## **FORMAT**

H(Starting address), (Ending Address), (Destination address) (.)

## > 12.MEMORY COMPARE (J)

This command allows the user to compare two blocks of memory for equality. If they are not equal the address of the first block at which there is a difference will be displayed.

## **FORMAT**

J(Starting address of first block),(Ending address of first block),(Straying address of second block)(.)

## EXAMPLE

Enter the following data using Examine Memory command:

| Address | opcode | instruction |

|---------|--------|-------------|

| 2000    | 3E 01  | MVI A,01    |

| 2002    | 06 02  | MVI B,02    |

| 2004    | 80     | ADD B       |

| 2005    | EF     | RST 5       |

Now block move this block to 2100 using Block move command. Now user Memory

Compare command as follows:

J 2000,2005,2100(.)

If the two blocks are identical,'8085 LCD TRAINER KIT M85-0X\_'is displayed.

Now change the contents of 2004 location to 10 using EXAMINE MEMORY Command. Again use the memory compare command as mentioned above. You will see that an address 2004 with its data will be displayed. On pressing (enter) '8085 LCD TRAINER KIT M85-0X\_' is displayed. It mean other contents are compared same.

## > 13.STRING(K)

This command allows to find the address or addresses at which a particular string of data is lying with in a specified program. The word string here means a few bytes of data lying consecutively one after another.

## **FORMAT**

K(Starting address),(Ending address),(Address where the first byte lies),(Address where the last byte lies)(.)

## **EXAMPLE**

Suppose in the example given below , if you want to find out the addresses at which the CALL DELAY instruction is lying.

| Address | opcode   | instruction |

|---------|----------|-------------|

| 2000    | 3E 80    | MVI A,80    |

| 2002    | D3 03    | OUT 03      |

| 2004    | 3E 55    | MVI A,55    |

| 2006    | D3 00    | OUT 00      |

| 2008    | CD A6 03 | CALL DELAY  |

| 200B    | 3E AA    | MVI A,AA    |

| 200D    | D3 00    | OUT 00      |

| 200F    | CD A6 03 | CALL DELAY  |

| 2012    | C3 04 20 | JMP 2004    |

### K 2000,2014,2006,2008(.)

In the above example, note the two addresses at which CALL DELAY is lying.

These addresses will be 2008 and 200F. Verify by Examine Memory command that CD A6 03 is lying at 2008 on wards. As the string found at location 2008, the message"STRING FOUND AT:2008" will come. Now go ahead by pressing (enter).

## Lab work:

1. Inter to register A (04) and to register B (05) and then change the content of register B to (02).

2. Delete three bytes of the program from 2005 to 2007.

| Address | opcode   | instruction |

|---------|----------|-------------|

| 2000    | 3E 01    | MVI A,01    |

| 2002    | 06 02    | MVI B,02    |

| 2004    | 80       | ADD B       |

| 2005    | 32 00 21 | STA 2100H   |

| 2008    | EF       | RST5        |

3. Move the program from location 2000-2005 to location 2100.

| Address | opcode | instruction |

|---------|--------|-------------|

| 2000    | 3E 01  | MVI A,01    |