University of Technology

Laser and Optoelectronics Engineering Department

Fourth Year

**Digital Design**

Prepared by Dr. Sinan Majid M. Sc. Eman Yousif Nasir

# Textbooks:

- 1. Digital Design, Morris M. Mano, (3rd Edition), Prentice Hall, 2002

- 2. Digital Fundamentals, Thomas L. Floyd, (9th Edition), Prentice Hall, 2006

- 3. Microprocessor Architecture, Programming, and Applications with the 8085, by

R. Gaonkar.

#### **Overview**

- The design of computers

It all starts with numbers

Building circuits

Building computing machines

- Digital systems

- Understanding decimal numbers

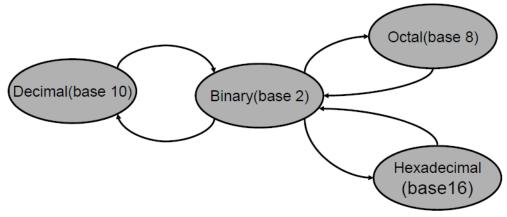

- Binary and octal numbersThe basis of computers!

- Conversion between different number systems

## **Digital Systems**

• Digital systems consider *discrete* amounts of data. Examples

- •26 letters in the alphabet

- •10 decimal digits

- Larger quantities can be built from discrete values:

- •Words made of letters

- •Numbers made of decimal digits (e.g. 239875.32)

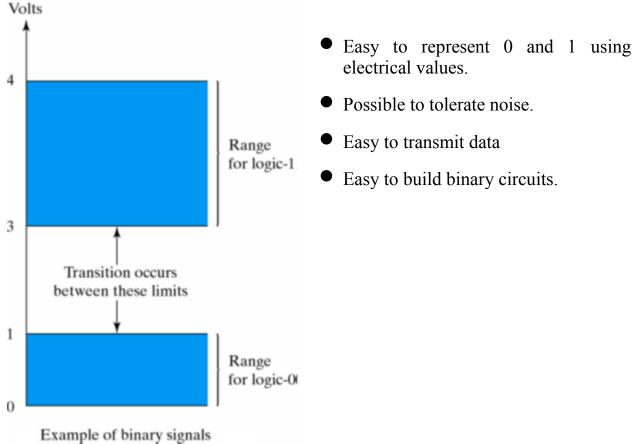

- Computers operate on *binary* values (0 and 1)

- Easy to represent binary values electrically

- •Voltages and currents.

- •Can be implemented using circuits

- •Create the building blocks of modern computers

#### **Understanding Decimal Numbers**

Decimal numbers are made of decimal digits: (0,1,2,3,4,5,6,7,8,9)

But how many items does a decimal number represent? 8653 = 8\*10<sup>3</sup>+ 6\*10<sup>2</sup> + 5\*10<sup>1</sup> + 3\*10<sup>0</sup>

What about fractions? 97654.35 = 9\*10<sup>4</sup>+ 7\*10<sup>3</sup> + 6\*10<sup>2</sup> + 5\*10<sup>1</sup> + 4\*10<sup>0</sup>+ 3\*10<sup>-1</sup> + 5\*10<sup>-2</sup>

•In formal notation -> (97654.35)<sub>10</sub>

## **Understanding Binary Numbers**

Binary numbers are made of binary digits (bits): 0 and 1

How many items does a binary number represent? (1011)2= 1\*2<sup>3</sup>+ 0\*2<sup>2</sup> + 1\*2<sup>1</sup> + 1\*2<sup>0</sup> = (11)<sub>10</sub>

What about fractions? (110.10)2= 1\*2<sup>2</sup> + 1\*2<sup>1</sup> + 0\*2<sup>0</sup>+ 1\*2<sup>-1</sup> + 0\*2<sup>-2</sup>

Groups of eight bits are called a *byte* (11001001)<sub>2</sub>

Groups of four bits are called a *nibble*. (1101)<sub>2</sub>

#### Why Use Binary Numbers?

# **Conversion Between Number Bases**

- Learn to convert between bases.

- Already demonstrated how to convert from binary to decimal.

## Convert an Integer from Decimal to another Base

For each digit position:

- 1. Divide decimal number by the base (e.g. 2)

- 2. The remainder is the lowest-order digit3.Repeat first two steps until no divisor remains.

# Example for (13)<sub>10:</sub>

|        | Integer<br>Quotien | t | Remainder | Coefficient        |

|--------|--------------------|---|-----------|--------------------|

| 13/2 = | 6                  | + | 1/2       | a <sub>0</sub> = 1 |

| 6/2 =  | 3                  | + | 0         | a <sub>1</sub> = 0 |

| 3/2 =  | 1                  | + | 1/2       | a <sub>2</sub> = 1 |

| 1/2 =  | 0                  | + | 1/2       | a <sub>3</sub> = 1 |

Answer  $(13)_{10} = (a_3 a_2 a_1 a_0)_2 = (1101)_2$

# Convert an Fraction from Decimal to another Base1.

- 1. Multiply decimal number by the base (e.g. 2)

- 2. The *integer* is the highest-order digit

- 3. Repeat first two steps until fraction becomes zero.

## Example for (0.625)<sub>10:</sub>

| Integer     | F | ractio | n Co | efficient           |

|-------------|---|--------|------|---------------------|

| 0.625 x 2 = | 1 | +      | 0.25 | a <sub>-1</sub> = 1 |

| 0.250 x 2 = | 0 | +      | 0.50 | a <sub>-2</sub> = 0 |

| 0.500 x 2 = | 1 | +      | 0    | a <sub>-3</sub> = 1 |

Answer

$$(0.625)_{10} = (0.a_{-1}a_{-2}a_{-3})_2 = (0.101)_2$$

## The Growth of Binary Numbers

| n | 2 <sup>n</sup>     |          | n  | 2 <sup>n</sup>        |      |

|---|--------------------|----------|----|-----------------------|------|

| 0 | 2º=1               | <b>•</b> | 8  | 2 <sup>8</sup> =256   |      |

| 1 | 21=2               |          | 9  | 2º=512                |      |

| 2 | 22=4               |          | 10 | 210=1024              |      |

| 3 | 23=8               |          | 11 | 211=2048              |      |

| 4 | 24=16              |          | 12 | 2 <sup>12</sup> =4096 |      |

| 5 | 25=32              |          | 20 | 2 <sup>20</sup> =1M   | Mega |

| 6 | 2 <sup>6</sup> =64 |          | 30 | 2 <sup>30</sup> =1G   | Giga |

| 7 | 27=128             | 1        | 40 | 2 <sup>40</sup> =1T   | Tera |

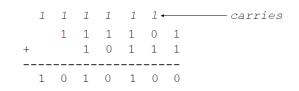

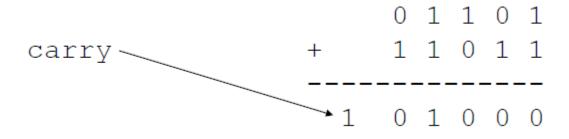

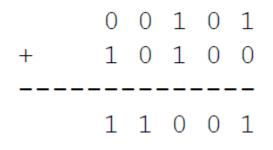

## **Binary Addition**

- Binary addition is very simple.

- This is best shown in an example of adding two binary numbers...

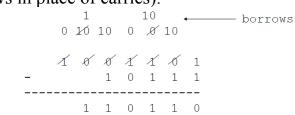

## **Binary Subtraction**

- We can also perform subtraction (with borrows in place of carries).

- Let's subtract (10111)<sub>2</sub> from (1001101)<sub>2</sub>...

## **Binary Multiplication**

Binary multiplication is much the same as decimal multiplication, except that the multiplication operations are much simpler...  $1 \quad 0 \quad 1 \quad 1 \quad 1$

| Х |   |             | 1 | 0<br>1           | 1<br>0 | _ | - |

|---|---|-------------|---|------------------|--------|---|---|

| 1 | 0 | 1<br>0<br>1 | 0 | 0<br>1<br>0<br>1 | 1      | - | 0 |

| 1 | 1 | 1           | 0 | 0                | 1      | 1 | 0 |

#### **Understanding Octal Numbers**

- Octal numbers are made of octal digits: (0,1,2,3,4,5,6,7)

- How many items does an octal number represent?

(4536)<sub>8</sub> = 4x8<sup>3</sup> + 5x8<sup>2</sup> + 3x8<sup>1</sup> + 6x8<sup>0</sup> = (1362)<sub>10</sub>

- What about fractions?

(465.27)<sub>8</sub> = 4x8<sup>2+</sup> 6x8<sup>1+</sup> 5x8<sup>0</sup> + 2x8<sup>-1+</sup> 7x8<sup>-2</sup>

- ° Octal numbers don't use digits 8 or 9

## Convert an Integer from Decimal to Octal

- 1. Divide decimal number by the base (8)

- 2. The *remainder* is the lowest-order digit

- 3. Repeat first two steps until no divisor remains.

Example for (175)<sub>10:</sub>

|         | Integer<br>Quotie |   | Remainder | Coefficient        |

|---------|-------------------|---|-----------|--------------------|

| 175/8 = | 21                | + | 7/8       | a <sub>0</sub> = 7 |

| 21/8 =  | 2                 | + | 5/8       | a <sub>1</sub> = 5 |

| 2/8 =   | 0                 | + | 2/8       | a <sub>2</sub> = 2 |

Answer  $(175)_{10} = (a_2 a_1 a_0)_2 = (257)_8$

## Convert an Fraction from Decimal to Octal

- 1. Multiply decimal number by the base (e.g. 8)

- 2. The *integer* is the highest-order digit

- 3. Repeat first two steps until fraction becomes zero.

Example for (0.3125)<sub>10:</sub>

| I                    | nteger | Fra    | ction | (      | Coefficient                                |

|----------------------|--------|--------|-------|--------|--------------------------------------------|

| 0.3125 x<br>0.5000 x | -      | 2<br>4 |       | 5<br>0 | a <sub>-1</sub> = 2<br>a <sub>-2</sub> = 4 |

Answer  $(0.3125)_{10} = (0.24)_8$

### **Understanding Hexadecimal Numbers**

- Hexadecimal numbers are made of <u>16</u> digits:

(0,1,2,3,4,5,6,7,8,9,A, B, C, D, E, F)

- <sup>o</sup> How many items does an hex number represent?

- $(3A9F)_{16} = 3x16^3 + 10x16^2 + 9x16^1 + 15x16^0 = 14999_{10}$

- ° What about fractions?

- (2D3.5)<sub>16</sub> = 2x16<sup>2</sup> + 13x16<sup>1</sup> + 3x16<sup>0</sup> + 5x16<sup>-1</sup> = 723.3125<sub>10</sub>

- Note that each hexadecimal digit can be represented with four bits.

- (1110) 2 = (E)16

- <sup>°</sup> Groups of four bits are called a *nibble*.

- (1110) <sub>2</sub>

## **Putting It All Together**

| Decimal | Binary | Octal | Hexadecimal |

|---------|--------|-------|-------------|

| 0       | 0      | 0     | 0           |

| 1       | 1      | 1     | 1           |

| 2       | 10     | 2     | 2           |

| 3       | 11     | 3     | 3           |

| 4       | 100    | 4     | 4           |

| 5       | 101    | 5     | 5           |

| 6       | 110    | б     | 6           |

| 7       | 111    | 7     | 7           |

| 8       | 1000   | 10    | 8           |

| 9       | 1001   | 11    | 9           |

| 10      | 1010   | 12    | А           |

| 11      | 1011   | 13    | в           |

| 12      | 1100   | 14    | С           |

| 13      | 1101   | 15    | D           |

| 14      | 1110   | 16    | Е           |

| 15      | 1111   | 17    | F           |

- Binary, octal, and hexadecimal similar

- Easy to build circuits to operate on these representations

- Possible to convert between the three formats

## **Converting Between Base 16 and Base 2**

$3A9F_{16} = 0011 1010 1001 1111_2$ 3 A 9 F

°Conversion is easy!

• Determine 4-bit value for each hex digit

°Note that there are 24= 16 different values of four bits

°Easier to read and write in hexadecimal.

°Representations are equivalent!

## Converting Between Base 16 and Base 8

| 3A9F <sub>16</sub> = | <u>0011</u> | <u>1010</u> | <u>) 100</u> | <u>)1</u> <u>1</u> | 111 <sub>2</sub> |

|----------------------|-------------|-------------|--------------|--------------------|------------------|

|                      | 3           | А           | 9            |                    | F                |

|                      |             |             | Ļ            |                    |                  |

| 35237 <sub>8</sub> = | 0 <u>11</u> | <u>101</u>  | <u>010</u>   | <u>011</u>         | <u>111</u> 2     |

|                      | 3           | 5           | 2            | 3                  | 7                |

- 1. Convert from Base 16 to Base 2

- 2. Regroup bits into groups of three starting from right

- 3. Ignore leading zeros

- 4. Each group of three bits forms an octal digit.

## Signed Numbers

## **How to Represent Signed Numbers**

•Plus and minus sign used for decimal numbers: 25 (or +25), -16, etc.

•For computers, desirable to represent everything as bits.

•Three types of signed binary number representations: signed magnitude, 1's complement, 2's complement.

•In each case: left-most bit indicates sign: positive (0) or negative (1).

Consider signed magnitude:

## **One's Complement Representation**

•The one's complement of a binary number involves inverting all bits.

•1's comp of 00110011 is 11001100

•1's comp of 10101010 is 01010101

•For an n bit number N the 1's complement is  $(2^{n}-1) - N$ .

•Called diminished radix complement by Mano since 1's complement for base (radix 2).

•To find negative of 1's complement number take the 1's complement.

## **Two's Complement Representation**

•The two's complement of a binary number involves inverting all bits and adding 1.

•2's comp of 00110011 is 11001101

•2's comp of 10101010 is 01010110

•For an n bit number N the 2's complement is  $(2^{n}-1) - N + 1$ .

•Called radix complement by Mano since 2's complement for base (radix 2).

•To find negative of 2's complement number take the 2's complement.

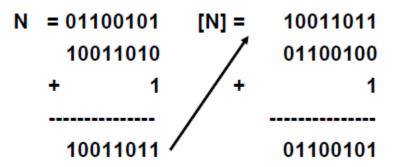

# **Two's Complement Shortcuts**

°Algorithm –Simply complement each bit and then add 1 to the result.

•Finding the 2's complement of (01100101)2and of its 2's complement...

#### **<u>1's Complement Addition</u>**

°Using 1's complement numbers, adding numbers is easy.

°For example, suppose we wish to add  $+(1100)_2$  and  $+(0001)_2$ .

°Let's compute  $(12)_{10} + (1)_{10}$ .

• $(12)_{10}$ = + $(1100)_2$  = 01100<sub>2</sub> in 1's comp.

• $(1)_{10}$ = + $(0001)_2$ = 00001<sub>2</sub> in 1's comp.

| Chan de Add bin and annah ann                                    | er bit 0 0 1 1 0 1<br>Add carry ↓ 0 |    |   |   |   |   |   |        |

|------------------------------------------------------------------|-------------------------------------|----|---|---|---|---|---|--------|

| Step 1: Add binary numbers<br>Step 2: Add carry to low-order bit | Add car                             | ry | 0 | 0 | 1 | 1 | 0 | 1<br>0 |

|                                                                  | Final<br>Result                     |    |   | 0 | 1 | 1 | 0 | 1      |

°Adding the carry bit, the sign bit is seen to be zero, indicating a positive result,

$(01101)_2 = +(1101)_2 = +(13)_{10}$

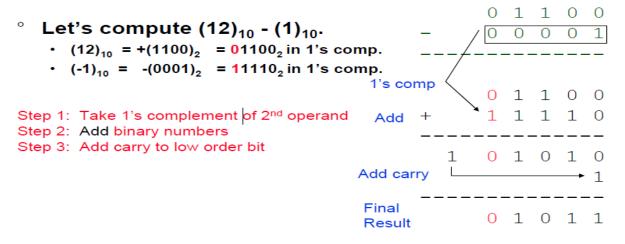

## **1's Complement Subtraction**

°Using 1's complement numbers, subtracting numbers is also easy.

°For example, suppose we wish to subtract  $+(0001)_2$  from  $+(1100)_2$ .

°Adding the carry bit, the sign bit is seen to be zero, indicating a positive result,  $(01011)_2 = +(1011)_2 = +(11)_{10}$

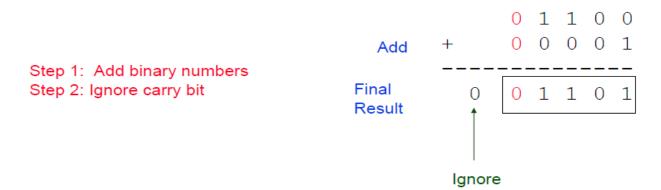

## 2's Complement Addition

°Using 2's complement numbers, adding numbers is easy.

°For example, suppose we wish to add  $+(1100)_2$  and  $+(0001)_2$ .

°Let's compute  $(12)_{10} + (1)_{10}$ .

• $(12)_{10}$  = + $(1100)_2$  = 01100<sub>2</sub> in 2's comp.

• $(1)_{10}$ = + $(0001)_2$ = 00001<sub>2</sub> in 2's comp.

°Discarding the carry bit, the sign bit is seen to be zero, indicating a positive result,

$(01101)_2 = +(1101)_2 = +(13)_{10}$

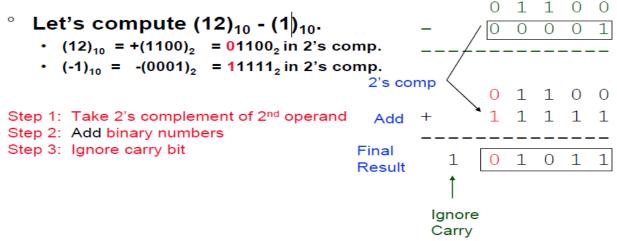

## 2's Complement Subtraction

°Using 2's complement numbers, follow steps for subtraction

°For example, suppose we wish to subtract  $+(0001)_2$  from  $+(1100)_2$ .

°Discarding the carry bit, the sign bit is seen to be zero, indicating a positive result,  $(01011)_2 = +(1011)_2 = +(11)_{10}$

## 2's Complement Subtraction: Example #2

°Let's compute  $(13)_{10}$ – $(5)_{10}$ .

$\bullet(13)_{10} = +(1101)_2 = (01101)_2$

•(-5)<sub>10</sub>= -(0101)<sub>2</sub>= (11011)<sub>2</sub>

°Adding these two 5-bit codes...

°Discarding the carry bit, the sign bit is seen to be zero, indicating a positive result,  $(01000)_2 = +(1000)_2 = +(8)_{10}$

## 2's Complement Subtraction: Example #3

°Let's compute  $(5)_{10}$ -(12)<sub>10</sub>.

•

$$(-12)_{10} = -(1100)_2 = (10100)_2$$

$$(5)_{10} = +(0101)_2 = (00101)_2$$

°Adding these two 5-bit codes...

°Here, there is no carry bit and the sign bit is 1. This indicates a negative result, which is what we expect.  $(11001)_2 = -(7)_{10}$ .

## **Binary Coded Decimal**

| Digit | BCD<br>Code | Digit | BCD<br>Code |

|-------|-------------|-------|-------------|

| 0     | 0000        | 5     | 0101        |

| 1     | 0001        | 6     | 0110        |

| 2     | 0010        | 7     | 0111        |

| 3     | 0011        | 8     | 1000        |

| 4     | 0100        | 9     | 1001        |

- Binary coded decimal (BCD) represents each decimal digit with four bits

- Ex.  $0011 0010 1001 = 329_{10}$

3 2 9

° This is <u>NOT</u> the same as 001100101001<sub>2</sub>

## **Putting It All Together**

| Decimal | Binary | Octal | Hexadecimal | BCD       |

|---------|--------|-------|-------------|-----------|

| 0       | 0      | 0     | 0           | 0000      |

| 1       | 1      | 1     | 1           | 0001      |

| 2       | 10     | 2     | 2           | 0010      |

| 3       | 11     | 3     | 3           | 0011      |

| 4       | 100    | 4     | 4           | 0100      |

| 5       | 101    | 5     | 5           | 0101      |

| 6       | 110    | 6     | 6           | 0110      |

| 7       | 111    | 7     | 7           | 0111      |

| 8       | 1000   | 10    | 8           | 1000      |

| 9       | 1001   | 11    | 9           | 1001      |

| 10      | 1010   | 12    | А           | 0001 0000 |

| 11      | 1011   | 13    | в           | 0001 0001 |

| 12      | 1100   | 14    | C           | 0001 0010 |

| 13      | 1101   | 15    | D           | 0001 0011 |

| 14      | 1110   | 16    | Е           | 0001 0100 |

| 15      | 1111   | 17    | F           | 0001 0101 |

<sup>o</sup> BCD not very efficient

Used in early computers (40s, 50s)

- Used to encode numbers for sevensegment displays.

- ° Easier to read?

#### Gray Code

| Digit | Binary | Gray |   |

|-------|--------|------|---|

| Ŭ     |        | Code | 0 |

| 0     | 0000   | 0000 |   |

| 1     | 0001   | 0001 |   |

| 2     | 0010   | 0011 |   |

| 3     | 0011   | 0010 | 0 |

| 4     | 0100   | 0110 | Ŭ |

| 5     | 0101   | 0111 |   |

| 6     | 0110   | 0101 | 0 |

| 7     | 0111   | 0100 |   |

| 8     | 1000   | 1100 | 0 |

| 9     | 1001   | 1101 | - |

| 10    | 1010   | 1111 |   |

| 11    | 1011   | 1110 |   |

| 12    | 1100   | 1010 |   |

| 13    | 1101   | 1011 |   |

| 14    | 1110   | 1001 |   |

| 15    | 1111   | 1000 |   |

Gray code is not a number system.

It is an alternate way to represent four bit data

Only one bit changes from one decimal digit to the next

Useful for reducing errors in communication.

Can be scaled to larger numbers.

#### ASCII Code

- American Standard Code for Information Interchange

- ASCII is a 7-bit code, frequently used with an 8<sup>th</sup> bit for error detection (more about that in a bit).

| Character | ASCII (bin) | ASCII (hex) | Decimal | Octal |

|-----------|-------------|-------------|---------|-------|

| Α         | 1000001     | 41          | 65      | 101   |

| В         | 1000010     | 42          | 66      | 102   |

| С         | 1000011     | 43          | 67      | 103   |

|           |             |             |         |       |

| Z         |             |             |         |       |

| а         |             |             |         |       |

|           |             |             |         |       |

| 1         |             |             |         |       |

| "         |             |             |         |       |

ASCII Codes and Data Transmission

- ° ASCII Codes

- <sup>°</sup> A Z (26 codes), a z (26 codes)

- ° 0-9 (10 codes), others (@#\$%^&\*....)

## **Parity Codes**

<sup>o</sup>Parity codes are formed by concatenating a *parity bit*, *P* to each code word of C. <sup>o</sup>In an *odd-parity code*, the parity bit is specified so that the total number of ones is odd.

°In an even-*parity code*, the parity bit is specified so that the total number of ones is even.

| Р                   | Informa | Information Bits |     |    |    |    |    |     |     |     |

|---------------------|---------|------------------|-----|----|----|----|----|-----|-----|-----|

| 1 1 0 0 0 0 1<br>↑  | 1       | 0<br>↑           | 1   | 0  | 0  | 0  | 0  | 1   | 1   |     |

| '<br>Added even par | ity bit | Åd               | lde | ed | 00 | dd | pa | ari | ity | bit |

## Parity Code Example

<sup>o</sup>Concatenate a parity bit to the ASCII code for the characters 0, X, and = to produce both odd-parity and even-parity codes.

| Character | ASCII   | Odd-Parity<br>ASCII | Even-Parity<br>ASCII |

|-----------|---------|---------------------|----------------------|

| 0         | 0110000 | 10110000            | 00110000             |

| x         | 1011000 | 01011000            | 11011000             |

| =         | 0111100 | 10111100            | 00111100             |

# **Boolean Algebra and Logic Gates**

**Combinational Circuit:** The outputs at any instance of time are entirely dependent upon the inputs present at that time.

°Analysis problem:

•Determine binary outputs for each combination of inputs

°Design problem: given a task, develop a circuit that accomplishes the task

•Many possible implementation

•Try to develop "best" circuit based on some criterion (size, power, performance, etc.)

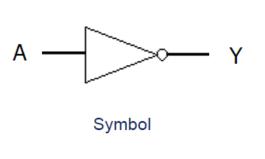

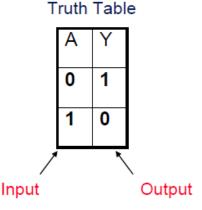

**Describing Circuit Functionality: Inverter**

°Basic logic functions have symbols.

°The same functionality can be represented with truth tables.

•Truth table completely specifies outputs for all input combinations.

°The above circuit is an inverter.

•An input of 0 is inverted to a 1.

•An input of 1 is inverted to a 0.

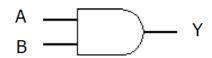

#### The AND Gate

- ° This is an AND gate.

- So, if the two inputs signals are asserted (high) the output will also be asserted.

Otherwise, the output will be deasserted (low).

| А | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

#### The OR Gate

- <sup>°</sup> This is an OR gate.

- So, if either of the two input signals are asserted, or both of them are, the output will be asserted.

| А | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

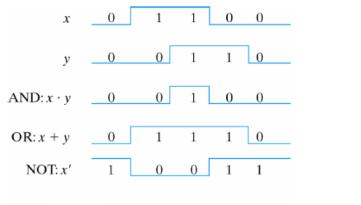

## **Describing Circuit Functionality: Waveforms**

| AND Gate |   |   |  |  |  |  |  |

|----------|---|---|--|--|--|--|--|

| А        | В | Y |  |  |  |  |  |

| 0        | 0 | 0 |  |  |  |  |  |

| 0        | 1 | 0 |  |  |  |  |  |

| 1        | 0 | 0 |  |  |  |  |  |

| 1        | 1 | 1 |  |  |  |  |  |

Input-output signals for gates

°Waveforms provide another approach for representing functionality.

°Values are either high (logic 1) or low (logic 0).

°Can you create a truth table from the waveforms?

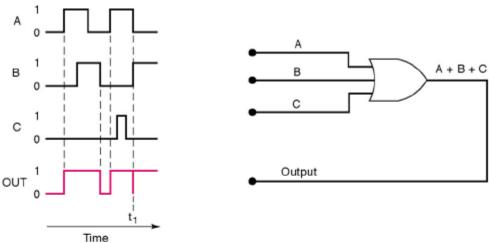

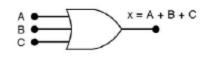

## **Consider three-input gates**

3 Input OR Gate

| A | В | С | x = A + B + C |

|---|---|---|---------------|

| 0 | 0 | 0 | 0             |

| 0 | 0 | 1 | 1             |

| 0 | 1 | 0 | 1             |

| 0 | 1 | 1 | 1             |

| 1 | 0 | 0 | 1             |

| 1 | 0 | 1 | 1             |

| 1 | 1 | 0 | 1             |

| 1 | 1 | 1 | 1             |

## **Boolean Algebra**

- •A *Boolean algebra* is defined as a closed algebraic system containing a set K or two or more elements and the two operators, . and +.

- •Useful for identifying and minimizing circuit functionality

- •Identity elements

- $\mathbf{a} + \mathbf{0} = \mathbf{a}$

- a . 1 = a

- •0 is the identity element for the + operation.

- •1 is the identity element for the . operation.

#### **Commutativity and Associativity of the Operators**

- •The Commutative Property: For every a and b in K, a + b = b + aa, b = b, a

- •The Associative Property:

For every a, b, and c in K,

a + (b + c) = (a + b) + c $a \cdot (b \cdot c) = (a \cdot b) \cdot c$

# **Distributivity of the Operators and Complements**

•The Distributive Property:

For every a, b, and c in K,

a + (b . c) = (a + b) . (a + c)

$a \cdot (b + c) = (a \cdot b) + (a \cdot c)$

•The Existence of the Complement:

For every a in K there exists a unique element called a'(*complement of a*) such that,

a + a' = 1 $a \cdot a' = 0$

•To simplify notation, the . operator is frequently omitted. When two elements are written next to each other, the AND (.) operator is implied...

$a + b \cdot c = (a + b) \cdot (a + c)$ a + bc = (a + b)(a + c)

## **Duality**

- •The principle of *duality* is an important concept. This says that if an expression is valid in Boolean algebra, the dual of that expression is also valid.

- •To form the dual of an expression, replace all + operators with . operators, all . operators with + operators, all ones with zeros, and all zeros with ones.

- •Form the dual of the expression

$\mathbf{a} + (\mathbf{b}\mathbf{c}) = (\mathbf{a} + \mathbf{b})(\mathbf{a} + \mathbf{c})$

•Following the replacement rules...

```

a(b+c) = ab+ac

```

•Take care not to alter the location of the parentheses if they are present.

# **Involution**

•This theorem states:

a''= a

- Remember that aa'=0 and a+a'=1.

- •Therefore, a' is the complement of a and a is also the complement of a'.

- •As the complement of a' is unique, it follows that a''=a.

Taking the double inverse of a value will give the initial value.

# **Absorption**

```

•This theorem states:

```

```

a + ab = a \qquad a(a+b) = a

•To prove the first half of this theorem:

a + ab = a \cdot 1 + ab= a (1 + b)= a (b + 1)= a (1)= a

```

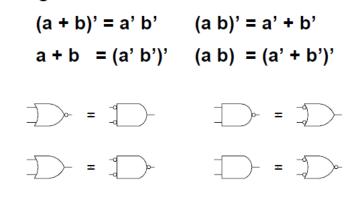

#### **DeMorgan'sTheorem**

•A key theorem in simplifying Boolean algebra expression is DeMorgan'sTheorem. It states:

(a + b)' = a'b' (ab)' = a' + b'

•Complement the expression a(b + z(x + a')) and simplify.

$$(a(b+z(x + a')))' = a' + (b + z(x + a'))'$$

= a'+ b'(z(x + a'))'

= a'+ b'(z'+ (x + a')')

= a'+ b'(z'+ x'a'')

= a'+ b'(z'+ x'a)

- •Basic logic functions can be made from AND, OR, and NOT (invert) functions

- •The behavior of digital circuits can be represented with waveforms, truth tables, or symbols

- •Primitive gates can be combined to form larger circuits

- •Boolean algebra defines how binary variables can be combined

- •Rules for associativity, commutativity, and distribution are similar to algebra

- •DeMorgan'srules are important.

Will allow us to reduce circuit sizes.

| The following table lists the most basic relations of Boolean algebra. All the |

|--------------------------------------------------------------------------------|

| relations can be proven by means of truth tables:                              |

| X+0=X           | X.0=0           |

|-----------------|-----------------|

| X+1=1           | X.1=X           |

| X+X=X           | X.X=X           |

| X+X'=1          | X.X'=0          |

| X+Y=Y+X         | XY=YX           |

| X+(Y+Z)=(X+Y)+Z | X(YZ)=(XY)Z     |

| X(Y+Z)=XY+XZ    | X+YZ=(X+Y)(X+Z) |

| (X+Y)'=X'Y'     | (XY)'=X'+Y'     |

| X''=X           | X+X'Y=X+Y       |

| X+XY=X          | X(X+Y)=X        |

| XY+XY'=X        | (X+Y)(X+Y')=X   |

## **Boolean Functions**

•Boolean algebra deals with binary variables and logic operations.

•Function results in binary 0 or 1

•Boolean algebra deals with binary variables and logic operations. •Function results in binary 0 or 1

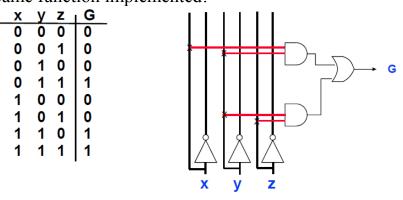

| X | У | Ζ | ху | yz | G |                                                                             |

|---|---|---|----|----|---|-----------------------------------------------------------------------------|

| 0 | 0 | 0 | 0  | 0  | 0 |                                                                             |

| 0 | 0 | 1 | 0  | 0  | 0 | х ху                                                                        |

| 0 | 1 | 0 | 0  | 0  | 0 |                                                                             |

| 0 | 1 | 1 | 0  | 1  | 1 | G = xy + yz                                                                 |

| 1 | 0 | 0 | 0  | 0  | 0 | z                                                                           |

| 1 | 0 | 1 | 0  | 0  | 0 | yz yz                                                                       |

| 1 | 1 | 0 | 1  | 0  | 1 | We will have have to transition hat your acception                          |

| 1 | 1 | 1 | 1  | 1  | 1 | We will learn how to transition between equation, symbols, and truth table. |

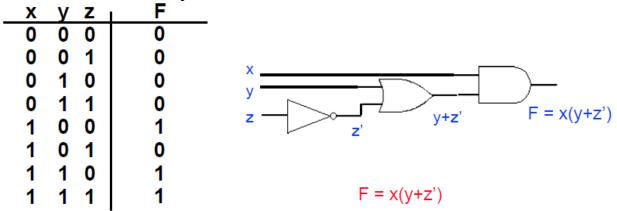

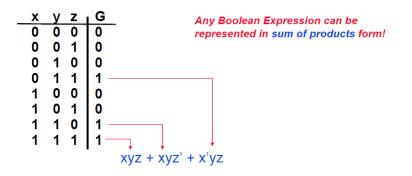

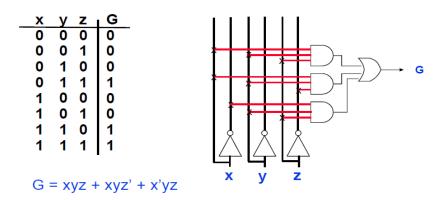

## Truth Table to Expression

•Converting a truth table to an expression

- •Each row with output of 1 becomes a product term

- •Sum product terms together.

#### **Equivalent Representations of Circuits**

•All three formats are equivalent

•Number of 1's in truth table output column equals AND terms for Sum-of-Products (SOP)

#### **Reducing Boolean Expressions**

•Is this the smallest possible implementation of this expression? No!

- •Use Boolean algebra rules to reduce complexity while preserving functionality.

- Step 1: Use Theorum1 (a + a = a) So xyz + xyz'+ x'yz= xyz + xyz + xyz'+ x'yz

Step 2: Use distributive rule a(b + c) = ab+ ac So xyz+ xyz+ xyz'+ x'yz= xy(z+ z') + yz(x+ x')

Step 3: Use Postulate 3 (a + a'= 1) So xy(z+ z') + yz(x+ x') = xy.1 + yz.1

Step 4: Use Postulate 2 (a . 1 = a)

- So xy.1 + yz.1 = xy+ yz= xyz + xyz'+ x'yz

#### **Reduced Hardware Implementation**

•Reduced equation requires less hardware! •Same function implemented!

G = xyz + xyz' + x'yz = xy + yz

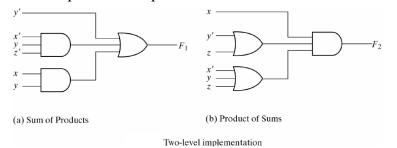

# Sum of Product (SOP) and Product of Sum (POS)

#### **Minterms and Maxterms**

•Each variable in a Boolean expression is a literal

- •Boolean variables can appear in normal (x) or complement form (x')

- •Each AND combination of terms is a minterm

- •Each OR combination of terms is a maxterm

| For ex    | ample:                     | For example:       |                |  |  |  |  |

|-----------|----------------------------|--------------------|----------------|--|--|--|--|

| Minte     | erms                       | Maxterms           |                |  |  |  |  |

| x y z     | Minterm                    | x y z Maxterr      | $M_0$          |  |  |  |  |

| 0 0 0     | x'y'z' m <sub>o</sub>      | 0 0 0 x+y+z        |                |  |  |  |  |

| 0 0 1     | x'y'z m <sub>1</sub>       | 0 0 1 x+y+z'       |                |  |  |  |  |

| 1 0 0     | xy'z' m <sub>4</sub>       | <br>1 0 0 x'+y+z   | $M_4$          |  |  |  |  |

| <br>1 1 1 | xy <b>z</b> m <sub>7</sub> | <br>1 1 1 x'+y'+z' | M <sub>7</sub> |  |  |  |  |

## **Representing Functions with Minterms**

•Minterm number same as row position in truth table (starting from top from 0) •Shorthand way to represent functions

| <b>0 0 0 0</b> $G = xyz + xyz' + x'yz$         |   |

|------------------------------------------------|---|

| 0 0 1 0                                        |   |

| 0 1 0 0                                        |   |

| 0 1 1 1 1                                      | ~ |

| <b>G</b> = $m_7 + m_6 + m_3 = \Sigma(3, 6, 7)$ | ) |

| 1 0 1 0 1                                      |   |

| 1 1 0 1                                        |   |

| 1 1 0 1<br>1 1 1 1                             |   |

This format is called Sum Of Product (SOP)

## **Complementing Functions**

•Minterm number same as row position in truth table (starting from top from 0) •Shorthand way to represent functions

| _ | X | У | Z | I G | ĽĠ, |                                       |

|---|---|---|---|-----|-----|---------------------------------------|

|   | 0 | 0 | 0 | 0   | [1  | G = xyz + xyz' + x'yz                 |

|   | 0 | 0 | 1 | 0   | 1   | 0 xj2 xj2 x xj2                       |

|   | 0 | 1 | 0 | 0   | 1   |                                       |

|   | 0 | 1 | 1 | 1   | 0   | G' = (xyz + xyz' + x'yz)'             |

|   | 1 | 0 | 0 | 0   | 1   |                                       |

|   | 1 | 0 | 1 | 0   | 1   |                                       |

|   | 1 | 1 | 0 | 1   | 0   | Can we find a simpler representation? |

|   | 1 | 1 | 1 | 1   | 0   |                                       |

#### **Complementation Example**

•Find complement of F = x'z+yz This format is called sum of product F'=(x'z+yz)'

•DeMorgan's

F' = (x'z)'(yz)'

•DeMorgan's

F' = (x'' + z')(y' + z')

•Reduction -> eliminate double negation on x

F'=(x+z')(y'+z') This format is called product of sums

## **Conversion Between Canonical Forms**

•Easy to convert between minterm and maxterm representations

•For maxterm representation, select rows with 0's

| Χ | У | Ζ | l G |          |                                                |

|---|---|---|-----|----------|------------------------------------------------|

| 0 | 0 | 0 | 0   | ←        | G = xyz + xyz' + x'yz                          |

| 0 | 0 | 1 | 0   | ←        |                                                |

| 0 | 1 | 0 | 0   | ←        | ·                                              |

| 0 | 1 | 1 | 1   |          | $G = m_7 + m_6 + m_3 = \Sigma(3, 6, 7)$        |

| 1 | 0 | 0 | 0   | ←        |                                                |

| 1 | 0 | 1 | 0   | ←        | ·                                              |

| 1 | 1 | 0 | 1   |          | $G = M_0 M_1 M_2 M_4 M_5 = \Pi(0, 1, 2, 4, 5)$ |

| 1 | 1 | 1 | 1   |          |                                                |

|   |   |   |     | G = (x+y | (x+z)(x+y+z')(x+y'+z)(x'+y+z)(x'+y+z')         |

|   |   |   |     |          | This format is called Product Of Sum (POS)     |

#### **Representation of Circuits**

- •All logic expressions can be represented in 2-level format

- •Circuits can be reduced to minimal 2-level representation

- •Sum of products representation most common in industry.

- Q) Assume the output (1,0,1,0, 1,0,1,0):

- 1- Construct the truth table

- 2- Find the Expression using sum of product then simplify the expression and draw the logic circuit diagram

- 3- Find the Expression using product of sum

| Inputs |   |   | Output |        |                |

|--------|---|---|--------|--------|----------------|

| Α      | В | С | F      |        |                |

| 0      | 0 | 0 | 1      | A'B'C' | $m_0$          |

| 0      | 0 | 1 | 0      |        | $m_1$          |

| 0      | 1 | 0 | 1      | A'BC'  | $m_2$          |

| 0      | 1 | 1 | 0      |        | m <sub>3</sub> |

| 1      | 0 | 0 | 1      | AB'C'  | $m_4$          |

| 1      | 0 | 1 | 0      |        | $m_5$          |

| 1      | 1 | 0 | 1      | ABC'   | m <sub>6</sub> |

| 1      | 1 | 1 | 0      |        | m <sub>7</sub> |

2)  $F = A'B'C' + A'BC' + AB'C' + ABC' = m_0 + m_2 + m_4 + m_6 = \sum (0,2,4,6)$

$$=A'C'(B'+B)+AC'(B'+B)=A'C'(1)+AC'(1)=A'C'+AC'=C'(A'+A)=C'(1)=C'$$

| 3 | ) |

|---|---|

| 9 |   |

1)

| Inputs |   |   | Output |                         |

|--------|---|---|--------|-------------------------|

| Α      | В | С | F      |                         |

| 0      | 0 | 0 | 1      | M <sub>0</sub>          |

| 0      | 0 | 1 | 0      | A+B+C' M <sub>1</sub>   |

| 0      | 1 | 0 | 1      | M <sub>2</sub>          |

| 0      | 1 | 1 | 0      | A+B'+C' M <sub>3</sub>  |

| 1      | 0 | 0 | 1      | $M_4$                   |

| 1      | 0 | 1 | 0      | A'+B+C' M <sub>5</sub>  |

| 1      | 1 | 0 | 1      | M <sub>6</sub>          |

| 1      | 1 | 1 | 0      | A'+B'+C' M <sub>7</sub> |

$F=(A+B+C')(A+B'+C')(A'+B+C')(A'+B'+C')=M_1M_3M_5M_7=\prod(1,3,5,7)$

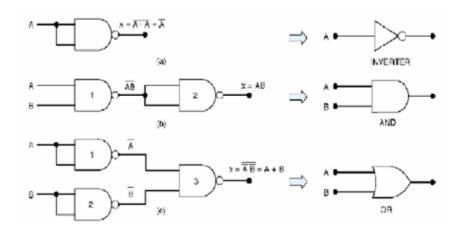

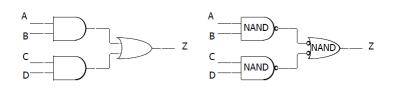

#### **NAND and NOR Gates**

#### The NAND Gate

- <sup>°</sup> This is a NAND gate. It is a combination of an AND gate followed by an inverter. Its truth table shows this...

- ° NAND gates have several interesting properties...

- NAND(a,a)=(aa)' = a' = NOT(a)

- NAND'(a,b)=(ab)'' = ab = AND(a,b)

- NAND(a',b')=(a'b')' = a+b = OR(a,b)

| А | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

#### The NAND Gate

- •These three properties show that a NAND gate with both of its inputs driven by the same signal is equivalent to a NOT gate

- •A NAND gate whose output is complemented is equivalent to an AND gate, and a NAND gate with complemented inputs acts as an OR gate.

- •Therefore, we can use a NAND gate to implement all three of the *elementary operators* (AND,OR,NOT).

- •Therefore, ANY switching function can be constructed using only NAND gates. Such a gate is said to be *primitive* or *functionally complete*.

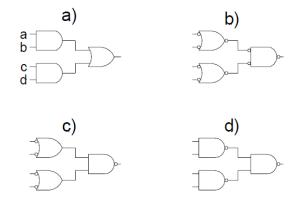

#### Universality of NAND gates

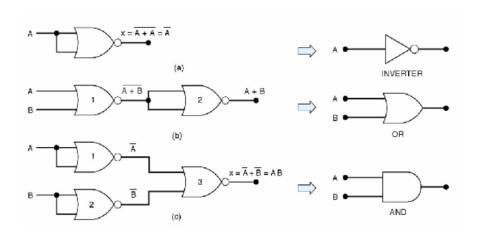

#### The NOR Gate

- <sup>°</sup> This is a NOR gate. It is a combination of an OR gate followed by an inverter. It's truth table shows this...

- <sup>o</sup> NOR gates also have several

interesting properties...

- NOR(a,a)=(a+a)' = a' = NOT(a)

- NOR'(a,b)=(a+b)'' = a+b = OR(a,b)

- NOR(a',b')=(a'+b')' = ab = AND(a,b)

| A | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

#### **Functionally Complete Gates**

- •Just like the NAND gate, the NOR gate is functionally complete...any logic function can be implemented using just NOR gates.

- •Both NAND and NOR gates are very valuable as any design can be realized using either one.

- •It is easier to build an IC chip using all NAND or NOR gates than to combine AND,OR, and NOT gates.

- •NAND/NOR gates are typically faster at switching and cheaper to produce.

#### Universality of NOR gate

## Example

#### NAND and XOR Implementations Combinational Design Procedure NAND-NAND & NOR-NOR Networks

**DeMorgan's Law:**

push bubbles or introduce in pairs or remove pairs.

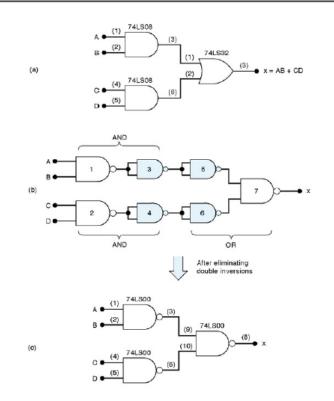

#### NAND-NAND Networks

#### ° Mapping from AND/OR to NAND/NAND

#### **Conversion Between Forms**

#### <sup>°</sup> Convert from networks of ANDs and ORs to networks of NANDs and NORs

Introduce appropriate inversions ("bubbles")

# <sup>°</sup> Each introduced "bubble" must be matched by a corresponding "bubble"

- · Conservation of inversions

- · Do not alter logic function

Example: AND/OR to NAND/NAND

A

B

C

NAND

A

B

NAND

NAND

NAND

**Conversion Between Forms (cont'd)**

#### ° Example: verify equivalence of two forms

$Z = [(A \cdot B)' \cdot (C \cdot D)']'$ = [(A' + B') \cdot (C' + D')]' = [(A' + B')' + (C' + D')'] = (A \cdot B) + (C \cdot D) \sqcot Ζ

Q) Convert to NAND gate only then to NOR gate only

$$=(B + C)(A + D)$$

$$=\overline{(B + C)} \overline{(A + D)}$$

$$=\overline{(\overline{B} \ \overline{C})} \overline{(\overline{A} \ \overline{D})}$$

$$=\overline{(\overline{BB} \ \overline{CC})} \overline{(\overline{AA} \ \overline{DD})}$$

X=(B+C)(A+D)

$$=\overline{(B+C)(A+D)}$$

$$=\overline{(B+C)}+\overline{(A+D)}$$

2)

$$F = (\overline{AB}) + (\overline{C}D)$$

$= \overline{(\overline{AB}) + (\overline{C}D)}$

$= \overline{(\overline{AB})} \overline{(\overline{C}D)}$

$= \overline{(\overline{AB})} \overline{(\overline{C}D)}$

$$F = (\overline{AB}) + (\overline{C}D)$$

$$= \overline{(\overline{AB}) + (\overline{C}D)}$$

$$=\overline{\overline{(\overline{A}B)}} + \overline{\overline{(\overline{C}D)}}$$

$$=\overline{\overline{(\overline{\overline{A}} + \overline{B})} + \overline{(\overline{\overline{C}} + \overline{D})}}$$

$$\overline{\overline{(\overline{A} + \overline{B} + \overline{B})} + \overline{(C + \overline{D} + \overline{D})}}$$

#### 3) K=(AB)+(C+D)

$$=\overline{(AB) + (C + D)}$$

$$=\overline{(AB)(C + D)}$$

$$=\overline{(AB)(C + D)}$$

$$=\overline{(AB)(\overline{C} \ \overline{D})}$$

$$=\overline{(AB)(\overline{\overline{C} \ \overline{D}})}$$

K=(AB)+(C+D)

| $=\overline{(AB) + (C+D)}$                                                       |

|----------------------------------------------------------------------------------|

| $=\overline{\overline{(AB)}} + \overline{\overline{(C+D)}}$                      |

| $=\overline{(\overline{\overline{A}}+\overline{\overline{B}}+\overline{(C+D)})}$ |

| $=\overline{\overline{(\overline{A+A}+\overline{B+B}+\overline{(C+D)})}}$        |

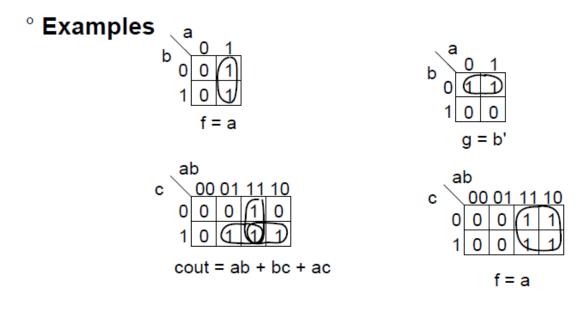

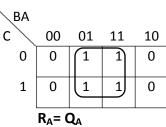

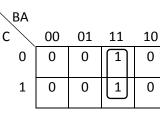

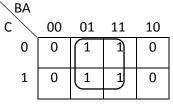

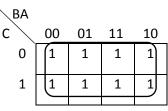

# **Minimization with Karnaugh Maps**

## Karnaugh maps

- Alternate way of representing Boolean function

- •All rows of truth table represented with a square

- •Each square represents a minterm

- Easy to convert between truth table, K-map, and SOP

- •Unoptimized form: number of 1's in K-map equal number of minterms (products) in SOP

- •Optimized form: reduced number of minterms

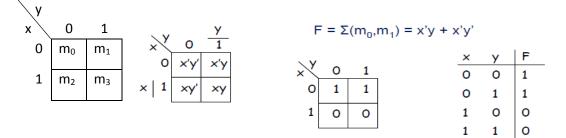

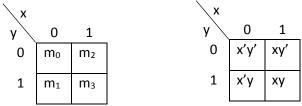

#### Two variable maps

It can be represented as follow:

Or represented as follow:

•A Karnaugh map is a graphical tool for assisting in the general simplification procedure.

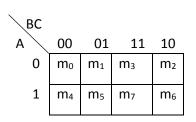

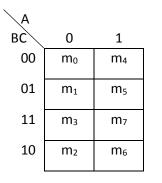

# Three variable maps It can be represented as follow:

| BC |        |       |      |       |

|----|--------|-------|------|-------|

| A  | 00     | 01    | 11   | 10    |

| 0  | A'B'C' | A'B'C | A'BC | A'BC' |

| 1  | AB'C'  | AB'C  | ABC  | ABC'  |

Or represented as follow:

| A  |        |       |

|----|--------|-------|

| ВС | 0      | 1     |

| 00 | A'B'C' | AB'C' |

| 01 | A'B'C  | AB'C  |

| 11 | A'BC   | ABC   |

| 10 | A'BC'  | ABC'  |

|               | A | в | С | F |

|---------------|---|---|---|---|

|               | 0 | 0 | 0 | 0 |

|               | 0 | 0 | 1 | 1 |

| BC            | 0 | 1 | 0 | 1 |

| A 00 01 11 10 | 0 | 1 | 1 | 0 |

|               | 1 | 0 | 0 | 1 |

|               | 1 | 0 | 1 | 1 |

| 1 1 1 1 1     | 1 | 1 | 0 | 1 |

|               | 1 | 1 | 1 | 1 |

|               |   |   |   |   |

F=AB'C'+AB'C+ABC+ABC'+A'B'C+A'BC'

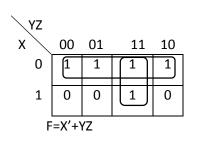

## **Rules for K-Maps**

- We can reduce functions by circling 1's in the K-map

- Each circle represents minterm reduction

- Following circling, we can deduce minimized and-or form.

#### **Rules to consider**

- Every cell containing a 1 must be included at least once.

- The largest possible "power of 2 rectangle must be enclosed.

- The 1's must be enclosed in the smallest possible number of rectangles.

A Karnaugh map is a graphical tool for assisting in the general simplification procedure.

## ° Two variable maps.

° Three variable maps.

$$\begin{array}{c} BC \\ A & 00 & 01 & 11 & 10 \\ 0 & 0 & 1 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 \end{array} \quad F = A + B'C + BC'$$

F=AB'C'+AB'C+ABC+ABC'+A'B'C+A'BC'

10

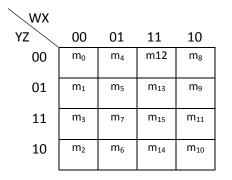

#### Karnaugh Maps for Four Input Functions

- Represent functions of 4 inputs with 16 minterms

- Use same rules developed for 3-input functions

- Note bracketed sections shown in example.

| $m_0$                  | $m_1$                  | <i>m</i> <sub>3</sub>  | <i>m</i> <sub>2</sub> |

|------------------------|------------------------|------------------------|-----------------------|

| $m_4$                  | $m_5$                  | $m_7$                  | $m_6$                 |

| <i>m</i> <sub>12</sub> | <i>m</i> <sub>13</sub> | <i>m</i> <sub>15</sub> | $m_{14}$              |

| $m_8$                  | $m_9$                  | $m_{11}$               | $m_{10}$              |

'or represented as follow:

#### Karnaugh map: 4-variable example

$F(A,B,C,D) = \Sigma m(0,2,3,5,6,7,8,10,11,14,15)$

| <u>, (73</u> | $^{\mathrm{J},\mathrm{C},\mathrm{D}}$ | ) 41 | $\Pi(0, 2)$ | , 5, 5, 0, 0, 0 |

|--------------|---------------------------------------|------|-------------|-----------------|

|              | Inp                                   | uts  |             | F               |

| Α            | В                                     | С    | D           |                 |

| 0            | 0                                     | 0    | 0           | 1               |

| 0            | 0                                     | 0    | 1           | 0               |

| 0            | 0                                     | 1    | 0           | 1               |

| 0            | 0                                     | 1    | 1           | 1               |

| 0            | 1                                     | 0    | 0           | 0               |

| 0            | 1                                     | 0    | 1           | 1               |

| 0            | 1                                     | 1    | 0           | 1               |

| 0            | 1                                     | 1    | 1           | 1               |

| 1            | 0                                     | 0    | 0           | 1               |

| 1            | 0                                     | 0    | 1           | 0               |

| 1            | 0                                     | 1    | 0           | 1               |

| 1            | 0                                     | 1    | 1           | 1               |

| 1            | 1                                     | 0    | 0           | 0               |

| 1            | 1                                     | 0    | 1           | 0               |

| 1            | 1                                     | 1    | 0           | 1               |

| 1            | 1                                     | 1    | 1           | 1               |

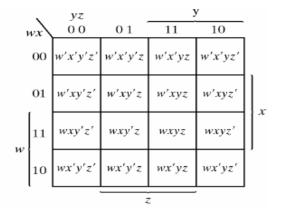

| 00 | W'X'Y'Z' | W'XY'Z' | WXY'Z' | WX'Y'Z' |

|----|----------|---------|--------|---------|

| 01 | W'X'Y'Z  | W'XY'Z  | WXY'Z  | WX'Y'Z  |

| 11 | W'X'YZ   | W'XYZ   | WXYZ   | WX'YZ   |

| 10 | W'X'YZ'  | W'XYZ'  | WXYZ'  | WX'YZ'  |

|    |          |         |        |         |

01

11

WX

YΖ

00

F=C+A'BD+B'D'

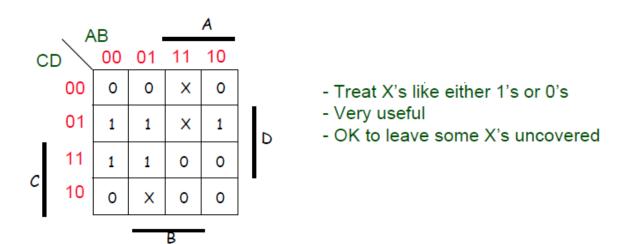

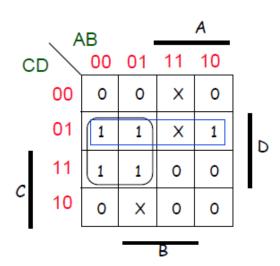

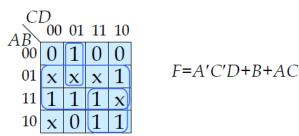

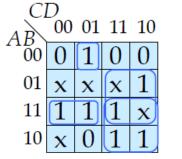

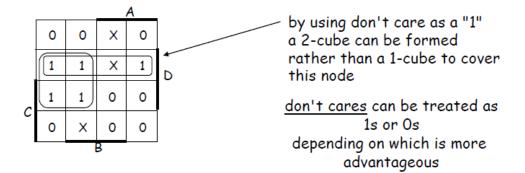

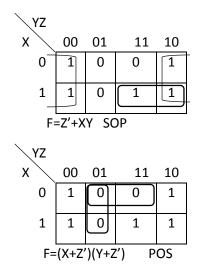

## Karnaugh maps: Don't cares

- In some cases, outputs are undefined

- We "don't care" if the logic produces a 0 or a 1

- This knowledge can be used to simplify functions.

°  $f(A,B,C,D) = \Sigma m(1,3,5,7,9) + d(6,12,13)$

without don't cares

- f=

| Α                          | в | С  | D                          | f                                                        |

|----------------------------|---|----|----------------------------|----------------------------------------------------------|

| 0                          | 0 | 0  | 0                          | 0                                                        |

| 0                          | 0 | 0  | 1                          | 1                                                        |

| 0<br>0<br>0<br>0<br>0<br>0 | 0 | 1  | 1<br>0<br>1<br>0<br>1<br>0 | 0                                                        |

| 0                          | 0 | 1  | 1                          | 1                                                        |

| 0                          | 1 | 0  | 0                          | 0                                                        |

| 0                          | 1 | 0  | 1                          | 1                                                        |

| 0                          | 1 | -1 | 0                          | X                                                        |

| 0                          | 1 | 1  | 1                          | 1                                                        |

| 1                          | 0 | 0  | 0                          | 0                                                        |

| 1                          | 0 | 0  | 1                          | 1                                                        |

| 1                          | 0 | 1  | 0                          | 0<br>1<br>0<br>1<br>0<br>1<br>X<br>1<br>0<br>1<br>0<br>0 |

| 1                          | 0 | 1  | 1                          | 0                                                        |

| 1                          | 1 | 0  | 0                          | X                                                        |

| 1                          | 1 | 0  | 1                          | X                                                        |

| 1                          | 1 | 1  | 0                          | X<br>X<br>0<br>0                                         |

| 1                          | 1 | 1  | 1                          | 0                                                        |

# **Don't Care Conditions**

- In some situations, we don't care about the value of a function for certain combinations of the variables.

- •these combinations may be impossible in certain contexts

- •or the value of the function may not matter in when the combinations occur

- In such situations we say the function is *incompletely specified* and there are multiple (completely specified) logic functions that can be used in the design.

•so we can select a function that gives the simplest circuit

- When constructing the terms in the simplification procedure, we can choose to either cover or not cover the don't care conditions.

## Map Simplification with Don't Cares

### •Alternative covering.

F=A'B'C'D+ABC'+BC+AC

$f(A,B,C,D) = \Sigma m(1,3,5,7,9) + d(6,12,13)$ 0 f = A'D + B'C'D f =

A'D + C'D

without don't cares with don't cares

### More KarnaughMap Examples

- 1. Circle the largest groups possible.

- 2. Group dimensions must be a power of 2.

- 3. Remember what circling means!

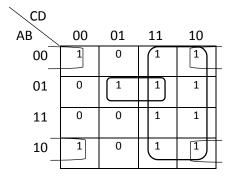

$F(A,B,C,D) = \sum (0,2,4,5,6,7,8,10,13,15)$

|   | Inp | uts |   | F | CD |              |             |      |            |

|---|-----|-----|---|---|----|--------------|-------------|------|------------|

| Α | В   | С   | D |   | AB | 00           | 01          | 11   | 10         |

| 0 | 0   | 0   | 0 | 1 | 00 | 1            | 0           | 0    | 1          |

| 0 | 0   | 0   | 1 | 0 | —  |              |             |      |            |

| 0 | 0   | 1   | 0 | 1 | 01 | 1            | $\int 1$    | 1)   | 1          |

| 0 | 0   | 1   | 1 | 0 |    |              |             |      |            |

| 0 | 1   | 0   | 0 | 1 | 11 | 0            | $\lfloor 1$ |      | 0          |

| 0 | 1   | 0   | 1 | 1 | 10 | 1            | -           | 0    |            |

| 0 | 1   | 1   | 0 | 1 | 10 | 1            | 0           | 0    | 1          |

| 0 | 1   | 1   | 1 | 1 |    | <u>Б</u> — А | A'B+I       |      | יחי        |

| 1 | 0   | 0   | 0 | 1 |    | $\Gamma = P$ | A D±I       | שדעכ | ענ         |

| 1 | 0   | 0   | 1 | 0 |    | _ ^          | 'D+(        | рог  | <b>)</b> ) |

| 1 | 0   | 1   | 0 | 1 |    | -A           | .'B+(       | вюг  | )          |

| 1 | 0   | 1   | 1 | 0 |    |              |             |      |            |

| 1 | 1   | 0   | 0 | 0 |    |              |             |      |            |

| 1 | 1   | 0   | 1 | 1 |    |              |             |      |            |

| 1 | 1   | 1   | 0 | 0 |    |              |             |      |            |

| 1 | 1   | 1   | 1 | 1 | ]  |              |             |      |            |

Q) Use a Karnaugh map to reduce the expression to a minimum SOP form

$F(A,B,C,D) = \sum (1,3,4,5,10-15)$

|   | Inputs |   |   |   |  |  |  |  |

|---|--------|---|---|---|--|--|--|--|

| Α | В      | С | D |   |  |  |  |  |

| 0 | 0      | 0 | 0 | 0 |  |  |  |  |

| 0 | 0      | 0 | 1 | 1 |  |  |  |  |

| 0 | 0      | 1 | 0 | 0 |  |  |  |  |

| 0 | 0      | 1 | 1 | 1 |  |  |  |  |

| 0 | 1      | 0 | 0 | 1 |  |  |  |  |

| 0 | 1      | 0 | 1 | 1 |  |  |  |  |

| 0 | 1      | 1 | 0 | 0 |  |  |  |  |

| 0 | 1      | 1 | 1 | 0 |  |  |  |  |

| 1 | 0      | 0 | 0 | 0 |  |  |  |  |

| 1 | 0      | 0 | 1 | 0 |  |  |  |  |

| 1 | 0      | 1 | 0 | 1 |  |  |  |  |

| 1 | 0      | 1 | 1 | 1 |  |  |  |  |

| 1 | 1      | 0 | 0 | 1 |  |  |  |  |

| 1 | 1      | 0 | 1 | 1 |  |  |  |  |

| 1 | 1      | 1 | 0 | 1 |  |  |  |  |

| 1 | 1      | 1 | 1 | 1 |  |  |  |  |

| CD |           |       |      |      |

|----|-----------|-------|------|------|

| AB | 00        | 01    | 11   | 10   |

| 00 | 0         | [1    | 1    | 0    |

| 01 | 1         | 1     | 0    | 0    |

| 11 | <u>_1</u> | _1    | 1    | 1    |

| 10 | 0         | 0     | 1    | 1    |

|    | F=B       | SC'+/ | AC+A | 'B'D |

$F(A,B,C,D) = \prod (1,3,9,11,12,14)$

|   | Inp | uts |   | F | CD  |                     |               |      |          |

|---|-----|-----|---|---|-----|---------------------|---------------|------|----------|

| Α | В   | С   | D |   | AB  | 00                  | 01            | 11   | 10       |

| 0 | 0   | 0   | 0 | 1 | 00  | 1                   | 0             | 0    | 1        |

| 0 | 0   | 0   | 1 | 0 | —   |                     |               |      |          |

| 0 | 0   | 1   | 0 | 1 | 01  | 1                   | $\int 1$      | 1)   | 1        |

| 0 | 0   | 1   | 1 | 0 |     |                     |               |      |          |

| 0 | 1   | 0   | 0 | 1 | 11  | 0                   | $\lfloor 1$   |      | 0        |

| 0 | 1   | 0   | 1 | 1 | 10  | 4                   | 0             | 0    | 1        |

| 0 | 1   | 1   | 0 | 1 | 10_ | 1                   | 0             | 0    | 1        |

| 0 | 1   | 1   | 1 | 1 |     | <u>Б</u> — <b>Л</b> | 'D⊥I          | BD+E | יחי      |

| 1 | 0   | 0   | 0 | 1 |     | $\Gamma = P$        | 1 D⊤I         | 2D+D |          |

| 1 | 0   | 0   | 1 | 0 |     | — <b>^</b>          | <b>'D</b> ⊥(  | рог  | •        |

| 1 | 0   | 1   | 0 | 1 |     | -A                  | л <b>D</b> ∓( | B⊙Ľ  | <b>)</b> |

| 1 | 0   | 1   | 1 | 0 |     |                     |               |      |          |

| 1 | 1   | 0   | 0 | 0 |     |                     |               |      |          |

| 1 | 1   | 0   | 1 | 1 |     |                     |               |      |          |

| 1 | 1   | 1   | 0 | 0 |     |                     |               |      |          |

| 1 | 1   | 1   | 1 | 1 |     |                     |               |      |          |

Q) Use a Karnaugh map to reduce the expression to a minimum SOP form

#### $F(A,B,C,D) = \prod(0,2,6-9)$

|   | Inp | uts |   | F |    |             |       |             |      |

|---|-----|-----|---|---|----|-------------|-------|-------------|------|

| Α | В   | С   | D |   |    |             |       |             |      |

| 0 | 0   | 0   | 0 | 0 |    |             |       |             |      |

| 0 | 0   | 0   | 1 | 1 |    |             |       |             |      |

| 0 | 0   | 1   | 0 | 0 |    |             |       |             |      |

| 0 | 0   | 1   | 1 | 1 | CD |             |       |             |      |

| 0 | 1   | 0   | 0 | 1 | AB | 00          | 01    | 11          | 10   |

| 0 | 1   | 0   | 1 | 1 | 00 | 0           | 1     | 1           | 0    |

| 0 | 1   | 1   | 0 | 0 |    | Ū           |       |             | Ũ    |

| 0 | 1   | 1   | 1 | 0 | 01 | 1           | 1     | 0           | 0    |

| 1 | 0   | 0   | 0 | 0 |    |             |       |             |      |

| 1 | 0   | 0   | 1 | 0 | 11 | $\lfloor 1$ |       | 1           | 1)   |

| 1 | 0   | 1   | 0 | 1 |    | _           |       |             |      |

| 1 | 0   | 1   | 1 | 1 | 10 | 0           | 0     | $\lfloor 1$ |      |

| 1 | 1   | 0   | 0 | 1 |    | ГГ          |       |             | ,D,D |

| 1 | 1   | 0   | 1 | 1 |    | F=F         | sc +7 | AC+A        | 'B'D |

| 1 | 1   | 1   | 0 | 1 |    |             |       |             |      |

| 1 | 1   | 1   | 1 | 1 |    |             |       |             |      |

F(X,Y,Z)=X'Y'+YZ+X'YZ'

|   | Inputs |   | Output |

|---|--------|---|--------|

| Х | Y      | Z | F      |

| 0 | 0      | 0 | 1      |

| 0 | 0      | 1 | 1      |

| 0 | 1      | 0 | 1      |

| 0 | 1      | 1 | 1      |

| 1 | 0      | 0 | 0      |

| 1 | 0      | 1 | 0      |

| 1 | 1      | 0 | 0      |

| 1 | 1      | 1 | 1      |

Q) Use a Karnaugh map to reduce the expression to a minimum SOP form  $F(W,X,Y,Z) = WXY + X^2 + W^2XZ$

|   | Inputs |   |   |   |  |  |  |  |

|---|--------|---|---|---|--|--|--|--|

| W | Х      | Y | Z |   |  |  |  |  |

| 0 | 0      | 0 | 0 | 1 |  |  |  |  |

| 0 | 0      | 0 | 1 | 0 |  |  |  |  |

| 0 | 0      | 1 | 0 | 1 |  |  |  |  |

| 0 | 0      | 1 | 1 | 0 |  |  |  |  |

| 0 | 1      | 0 | 0 | 0 |  |  |  |  |

| 0 | 1      | 0 | 1 | 1 |  |  |  |  |

| 0 | 1      | 1 | 0 | 0 |  |  |  |  |

| 0 | 1      | 1 | 1 | 1 |  |  |  |  |

| 1 | 0      | 0 | 0 | 1 |  |  |  |  |

| 1 | 0      | 0 | 1 | 0 |  |  |  |  |

| 1 | 0      | 1 | 0 | 1 |  |  |  |  |

| 1 | 0      | 1 | 1 | 0 |  |  |  |  |

| 1 | 1      | 0 | 0 | 0 |  |  |  |  |

| 1 | 1      | 0 | 1 | 0 |  |  |  |  |

| 1 | 1      | 1 | 0 | 1 |  |  |  |  |

| 1 | 1      | 1 | 1 | 1 |  |  |  |  |

| YZ  |     |       |     |      |    |

|-----|-----|-------|-----|------|----|

| wx  | 00  | 01    | 11  | 10   |    |

| 00  | 1   | 0     | 0   | 1    | _  |

| 01  | 0   | [1    | 1   | 0    |    |

| 11  | 0   | 0     | 1   | 1    |    |

| 10_ | 1   | 0     | 0   | 1    | -  |

|     | F=X | C'Z'+ | W'X | Z+W2 | XY |

Q) Use a Karnaugh map to reduce the expression to a minimum SOP and minimum POS form F(X,Y,Z) = X'Z'+Y'Z'+YZ'+XY

|   | Inputs | Output |   |

|---|--------|--------|---|

| Χ | Y      | Z      | F |

| 0 | 0      | 0      | 1 |

| 0 | 0      | 1      | 0 |

| 0 | 1      | 0      | 1 |

| 0 | 1      | 1      | 0 |

| 1 | 0      | 0      | 1 |

| 1 | 0      | 1      | 0 |

| 1 | 1      | 0      | 1 |

| 1 | 1      | 1      | 1 |

|   |        |        |   |

Q) Use a Karnaugh map to reduce the expression to a minimum SOP and minimum POS form, then draw both logic circuit

$F(A,B,C,D) = \sum (0,2,5,6,7,8,10)$

|   | Inp | uts |   | F | CD   |        |          |                                   |       |       |     |

|---|-----|-----|---|---|------|--------|----------|-----------------------------------|-------|-------|-----|

| Α | В   | С   | D |   | AB   | 00     | 01       | 11                                | 10    |       |     |

| 0 | 0   | 0   | 0 | 1 | 00 - | 1      | 0        | 0                                 | 1     | -     |     |

| 0 | 0   | 0   | 1 | 0 | -    |        |          |                                   |       | -     |     |

| 0 | 0   | 1   | 0 | 1 | 01   | 0      | 1        | $\begin{bmatrix} 1 \end{bmatrix}$ | 1     |       |     |

| 0 | 0   | 1   | 1 | 0 |      |        |          |                                   |       |       |     |

| 0 | 1   | 0   | 0 | 0 | 11   | 0      | 0        | 0                                 | 0     |       |     |

| 0 | 1   | 0   | 1 | 1 | 40   |        | 0        | 0                                 |       | -     |     |

| 0 | 1   | 1   | 0 | 1 | 10 _ | 1      | 0        | 0                                 | 1     |       |     |

| 0 | 1   | 1   | 1 | 1 | Б    | - ^ 'D |          | 'DC                               | B'D   | , SOF | )   |

| 1 | 0   | 0   | 0 | 1 | Г    | -A D   | $D^{+}A$ |                                   |       | 301   |     |

| 1 | 0   | 0   | 1 | 0 | CD   |        |          |                                   |       |       |     |

| 1 | 0   | 1   | 0 | 1 | AB   | 00     | 01       | 11                                | 10    |       |     |

| 1 | 0   | 1   | 1 | 0 |      |        |          |                                   | 1     | 1     |     |

| 1 | 1   | 0   | 0 | 0 | 00   | 1      | 0        | 0                                 | 1     |       |     |

| 1 | 1   | 0   | 1 | 0 | 01   | ര      | 1        | 1                                 | 1     |       |     |

| 1 | 1   | 1   | 0 | 0 | 01   |        | Т        | T                                 | T     |       |     |

| 1 | 1   | 1   | 1 | 0 | 11   | 0      | 0        | 0                                 | 0     |       |     |

|   |     |     |   |   |      | Ľ      |          |                                   | Ľ     |       |     |

|   |     |     |   |   | 10   | 1      | 0        | 0                                 | 1     |       |     |

|   |     |     |   |   | F=   | (A'+   | B')(E    | ₿'+CЧ                             | -D)(E | 8+D') | POS |

$F(X,Y,Z) = \sum m(0,1,2,4,5) + d(3,6,7)$

|   | Inputs | Output |   |

|---|--------|--------|---|

| Х | Y      | Z      | F |

| 0 | 0      | 0      | 1 |

| 0 | 0      | 1      | 1 |

| 0 | 1      | 0      | 1 |

| 0 | 1      | 1      | Х |

| 1 | 0      | 0      | 1 |

| 1 | 0      | 1      | 1 |

| 1 | 1      | 0      | Х |

| 1 | 1      | 1      | Х |

Q) Use a Karnaugh map to reduce the expression to a minimum SOP and minimum POS form, then draw both logic circuit

$F(A,B,C,D) = \sum m(0,1,2,3,7,8,10) + d(5,6,11,15)$

|   | Inp | uts |   | F | CD   |      |                    |       |     |

|---|-----|-----|---|---|------|------|--------------------|-------|-----|

| Α | В   | С   | D |   | AB   | 00   | 01                 | 11    | 10  |

| 0 | 0   | 0   | 0 | 1 | 00   | 1    | $\left( 1 \right)$ | 1)    | 1   |

| 0 | 0   | 0   | 1 | 1 | -    |      |                    |       |     |

| 0 | 0   | 1   | 0 | 1 | 01   | 0    | (X                 |       | Х   |

| 0 | 0   | 1   | 1 | 1 |      |      |                    |       |     |

| 0 | 1   | 0   | 0 | 0 | 11   | 0    | 0                  | Х     | 0   |

| 0 | 1   | 0   | 1 | Х | 10 - | 1    | 0                  | V     |     |

| 0 | 1   | 1   | 0 | Х | 10   | 1    | 0                  | Х     | 1   |

| 0 | 1   | 1   | 1 | 1 |      |      | Λ'Ω                | B'D   | SOP |

| 1 | 0   | 0   | 0 | 1 |      | Г-   | $A D^{\gamma}$     | ъυ    | SOP |

| 1 | 0   | 0   | 1 | 0 | CD   |      |                    |       |     |

| 1 | 0   | 1   | 0 | 1 |      | 00   | 01                 | 11    | 10  |

| 1 | 0   | 1   | 1 | Х | AB   | 00   | 01                 | 11    |     |

| 1 | 1   | 0   | 0 | 0 | 00   | 1    | 1                  | 1     | 1   |

| 1 | 1   | 0   | 1 | 0 | 01   | 0    | Х                  | 1     | X   |

| 1 | 1   | 1   | 0 | 0 | 01   | 0    | ^                  | T     | ^   |

| 1 | 1   | 1   | 1 | Х | 11   | 0    | $\overline{(0)}$   | X     | 0   |

|   |     |     |   |   |      | U    | l                  |       |     |

|   |     |     |   |   | 10   | 1    | 0                  | X     | 1   |

|   |     |     |   |   | F=   | (A'+ | D')(E              | 3'+D) | POS |

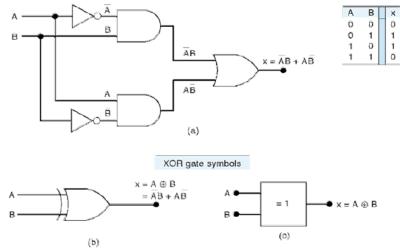

## **Exclusive-OR and Exclusive-NOR Circuits**

Exclusive-OR (XOR) produces a HIGH output whenever the two inputs are at opposite levels.

#### **Controlled Inverter:**

The XOR gate can be used as a "NOT" gate by connecting one of the inputs to the logic (1), for this reason it can be used to complement the 1<sup>st</sup> input by using the 2<sup>nd</sup> input as control line, when control signal is logic (0) then, X = A. When control signal is logic (1) then, X = A?

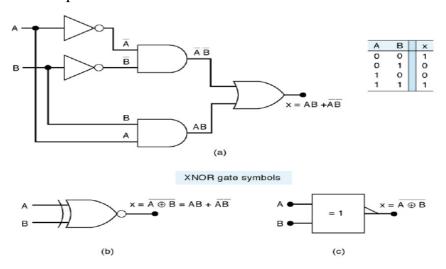

Exclusive-NOR (XNOR): Exclusive-NOR (XNOR) produces a HIGH output whenever the two inputs are at the same level.

# **Exclusive-NOR Circuits**

XNOR gate may be used to simplify circuit implementation.

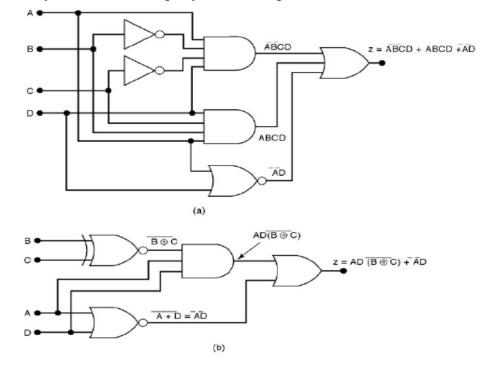

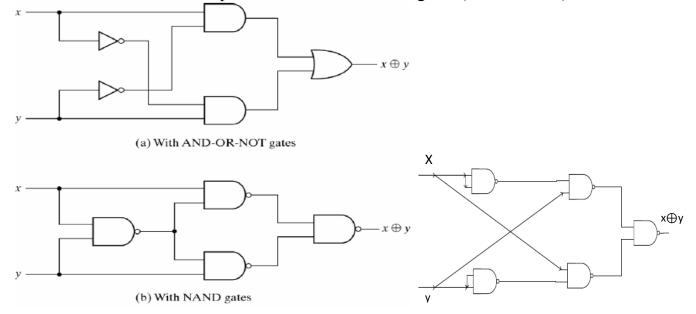

## **XOR Function**

XOR function can also be implemented with AND/OR gates (also NANDs).

## **XOR Function**

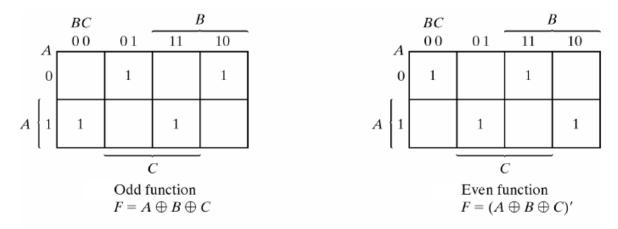

- Even function even number of inputs are 1, the output will be 1.

- Odd function –odd number of inputs are 1, the output will be 1.

| Α | В | С | Even<br>Function | Odd<br>Function |

|---|---|---|------------------|-----------------|

| 0 | 0 | 0 | 1                | 0               |

| 0 | 0 | 1 | 0                | 1               |

| 0 | 1 | 0 | 0                | 1               |

| 0 | 1 | 1 | 1                | 0               |

| 1 | 0 | 0 | 0                | 1               |

| 1 | 0 | 1 | 1                | 0               |

| 1 | 1 | 0 | 1                | 0               |

| 1 | 1 | 1 | 0                | 1               |

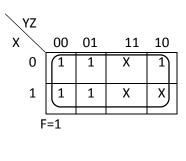

Map for a Three-variable Exclusive-OR Function

#### Odd Function:

F=A'B'C+A'BC'+AB'C'+ABC

=C(A'B'+AB)+C'(A'B+AB')

$$=C(A \oplus B)'+C'(A \oplus B)$$

=А⊕В⊕С

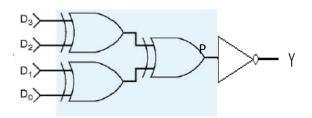

Q) Design even and odd parity

- Even parity even number of inputs are 1, the output will be 0.

- Odd parity –odd number of inputs are 1, the output will be 0.

| <b>D</b> <sub>3</sub> | D <sub>2</sub> | <b>D</b> <sub>1</sub> | D <sub>0</sub> | Even<br>parity P | Odd<br>parity Y |

|-----------------------|----------------|-----------------------|----------------|------------------|-----------------|

| 0                     | 0              | 0                     | 0              | 0                | 1               |

| 0                     | 0              | 0                     | 1              | 1                | 0               |

| 0                     | 0              | 1                     | 0              | 1                | 0               |

| 0                     | 0              | 1                     | 1              | 0                | 1               |

| 0                     | 1              | 0                     | 0              | 1                | 0               |

| 0                     | 1              | 0                     | 1              | 0                | 1               |

| 0                     | 1              | 1                     | 0              | 0                | 1               |

| 0                     | 1              | 1                     | 1              | 1                | 0               |

| 1                     | 0              | 0                     | 0              | 1                | 0               |

| 1                     | 0              | 0                     | 1              | 0                | 1               |

| 1                     | 0              | 1                     | 0              | 0                | 1               |

| 1                     | 0              | 1                     | 1              | 1                | 0               |

| 1                     | 1              | 0                     | 0              | 0                | 1               |

| 1                     | 1              | 0                     | 1              | 1                | 0               |

| 1                     | 1              | 1                     | 0              | 1                | 0               |

| 1                     | 1              | 1                     | 1              | 0                | 1               |

$P = \mathsf{D'_3D'_2D'_1D_0} + \mathsf{D'_3D'_2D_1D'_0} + \mathsf{D'_3D_2D'_1D'_0} + \mathsf{D'_3D_2D_1D_0} + \mathsf{D_3D_2D'_1D_0} + \mathsf{D_3D_2D_1D'_0} + \mathsf{D_3D'_2D'_1D'_0} + \mathsf{D_3D'_2$

$= (D_3 \bigoplus D_2) \bigoplus (D_1 \bigoplus D_0)$

Y=P'

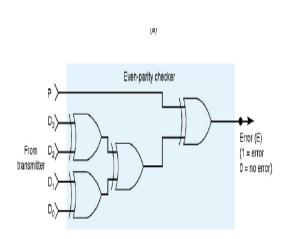

| D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Even<br>parity<br>P | Even<br>Parity<br>Checker E |

|----------------|----------------|----------------|----------------|---------------------|-----------------------------|

| 0              | 0              | 0              | 0              | 0                   | 0                           |

| 0              | 0              | 0              | 1              | 1                   | 0                           |

| 0              | 0              | 1              | 0              | 1                   | 0                           |

| 0              | 0              | 1              | 1              | 0                   | 0                           |

| 0              | 1              | 0              | 0              | 1                   | 0                           |

| 0              | 1              | 0              | 1              | 0                   | 0                           |

| 0              | 1              | 1              | 0              | 0                   | 0                           |

| 0              | 1              | 1              | 1              | 1                   | 0                           |

| 1              | 0              | 0              | 0              | 1                   | 0                           |

| 1              | 0              | 0              | 1              | 0                   | 0                           |

| 1              | 0              | 1              | 0              | 0                   | 0                           |

| 1              | 0              | 1              | 1              | 1                   | 0                           |

| 1              | 1              | 0              | 0              | 0                   | 0                           |

| 1              | 1              | 0              | 1              | 1                   | 0                           |

| 1              | 1              | 1              | 0              | 1                   | 0                           |

| 1              | 1              | 1              | 1              | 0                   | 0                           |

$E=P\oplus((D_3\oplus D_2)\oplus(D_1\oplus D_0))$

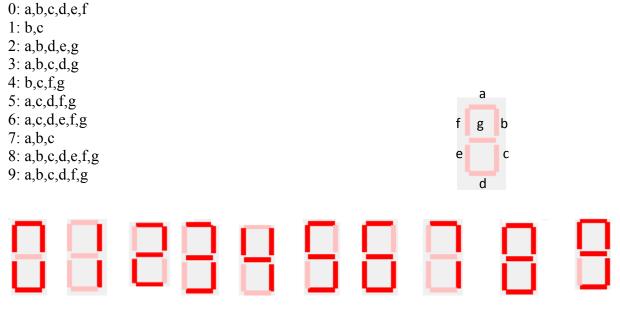

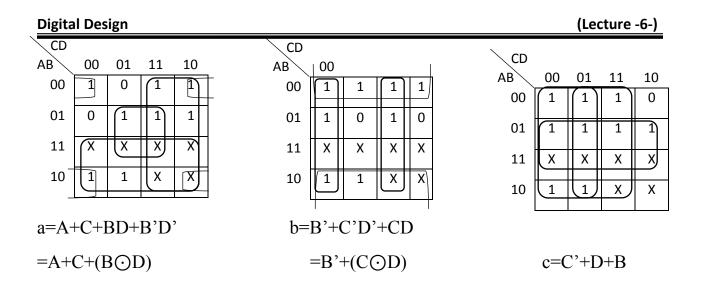

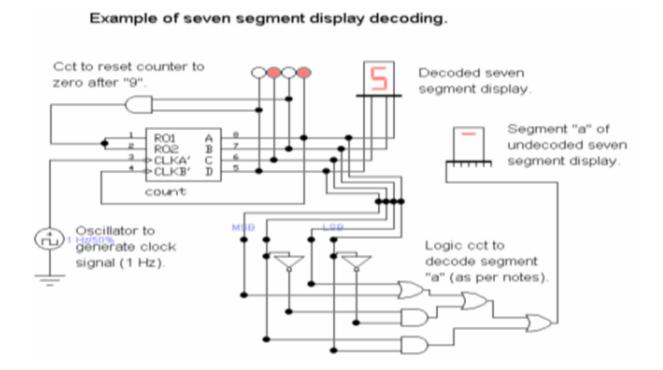

## **BCD to Seven Segment**

- Used to display binary coded decimal (BCD) numbers using seven illuminated segments.

- BCD uses 0's and 1's to represent decimal digits 0 -9. Need four bits to represent required 10 digits.

- Binary coded decimal (BCD) represents each decimal digit with four bits

List the segments that should be illuminated for each digit.

• Derive the truth table for the circuit. Each output column in one circuit.

| No. | Α | В | С | D | а | b | С | d | е | f | g |

|-----|---|---|---|---|---|---|---|---|---|---|---|

| 0   | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1   | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2   | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3   | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4   | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5   | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6   | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7   | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8   | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9   | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

• Find minimal sum-of-products representation for each output

For segment "a":

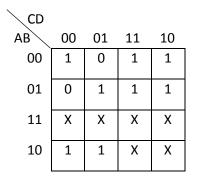

| CD |    |    |    |    |  |

|----|----|----|----|----|--|

| AB | 00 | 01 | 11 | 10 |  |

| 00 | 1  | 0  | 1  | 1  |  |

| 01 | 0  | 1  | 1  | 1  |  |

| 11 |    |    |    |    |  |

| 10 | 1  | 1  |    |    |  |

Note: Have only filled in ten squares, corresponding to the ten numerical digits we wish to represent.

Fill in don't cares for undefined outputs. Leads to a reduced implementation

Note that these combinations of inputs should never happen.

Put in "X" (don't care), and interpret as either 1 or 0 as desired ....

- Circle biggest group of 1's and Don't Cares. Leads to a reduced implementation. All 1's should be covered by at least one implicant

- Put all the terms together

- Generate the circuit

#### **Homework**

Design circuits for segments d, e, f, and g of seven segments to display BCD numbers

## **Binary Addition and Subtraction**

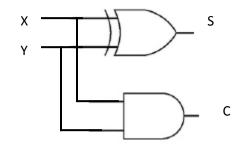

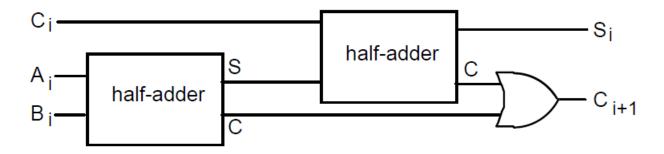

#### Half adder

Add two binary numbers

X,Y: single bit inputs

S: single bit sum, C: carry out

| Х | Y | C | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

$S = X'Y + XY' = (X \bigoplus Y)$

C: XY

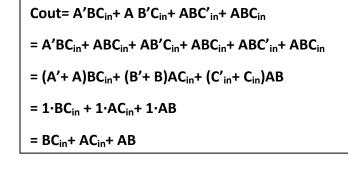

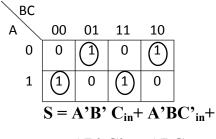

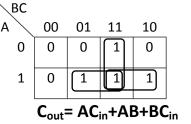

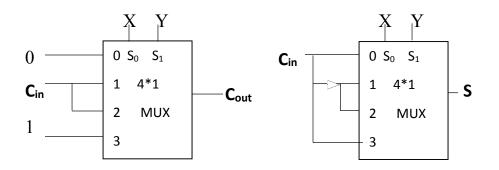

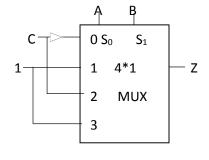

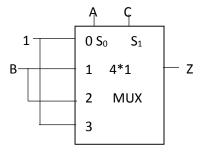

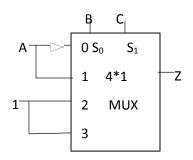

## <u>Full adder</u>

Full adder includes carry in Cin

| A | В | C <sub>in</sub> | Cout | S |

|---|---|-----------------|------|---|

| 0 | 0 | 0               | 0    | 0 |

| 0 | 0 | 1               | 0    | 1 |

| 0 | 1 | 0               | 0    | 1 |

| 0 | 1 | 1               | 1    | 0 |

| 1 | 0 | 0               | 0    | 1 |

| 1 | 0 | 1               | 1    | 0 |

| 1 | 1 | 0               | 1    | 0 |

| 1 | 1 | 1               | 1    | 1 |

AB' C'<sub>in</sub>+ ABC<sub>in</sub>

$$= C_{in}(A'B'+AB)+C'_{in}(A'B+AB')$$

$$= C_{in}(A \oplus B)'+C'_{in}(A \oplus B)$$

$= C_{in} \bigoplus A \bigoplus B$

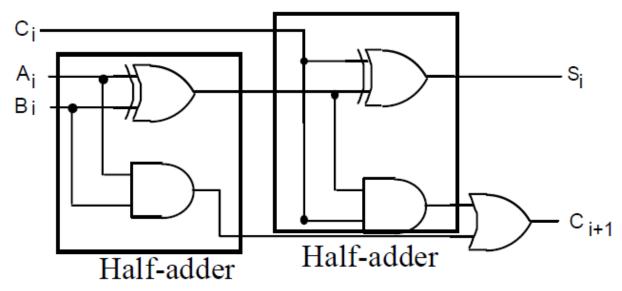

• Full adder made of several half adders

• Hardware repetition simplifies hardware design

A full adder can be made from two half adders (plus an OR gate).

- Putting it all together

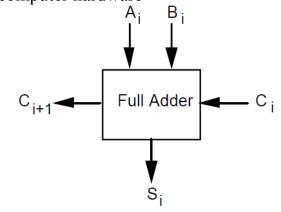

- •Single-bit full adder

•Common piece of computer hardware

Block Diagram

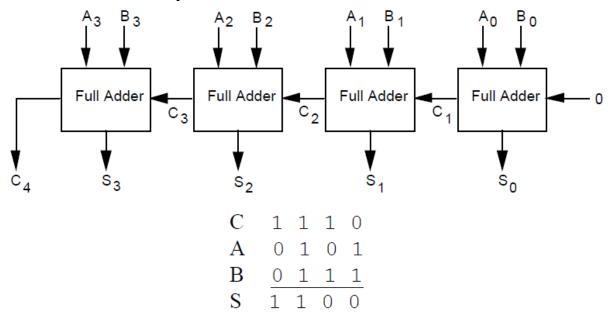

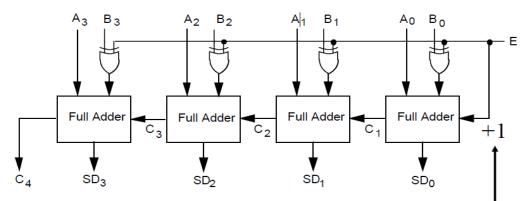

## **<u>4-Bit Adder</u>**

Chain single-bit adders together. What does this do to delay?

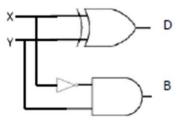

#### **Half Subtractor**

Subtract two binary numbers

X,Y: single bit inputs, D: single bit difference, B: barrow

| Х | Y | D | В |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

$D = X'Y + XY' = (X \bigoplus Y)$

B: X'Y

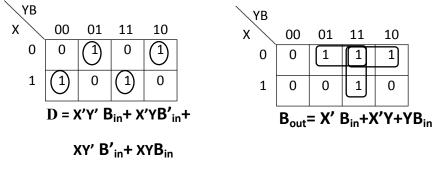

#### **Full subtractor**

Full subtractor include barrow: Bin

| X | Y | B <sub>in</sub> | D | B <sub>out</sub> |

|---|---|-----------------|---|------------------|

| 0 | 0 | 0               | 0 | 0                |

| 0 | 0 | 1               | 1 | 1                |

| 0 | 1 | 0               | 1 | 1                |

| 0 | 1 | 1               | 0 | 1                |

| 1 | 0 | 0               | 1 | 0                |

| 1 | 0 | 1               | 0 | 0                |

| 1 | 1 | 0               | 0 | 0                |

| 1 | 1 | 1               | 1 | 1                |

$$= B_{in}(X'Y'+XY) + B'_{in}(X'Y+XY')$$

$$= \mathbf{B}_{in}(\mathbf{X} \oplus \mathbf{Y})' + \mathbf{B'}_{in}(\mathbf{X} \oplus \mathbf{Y})$$

= B<sub>in</sub>⊕x⊕y

## Negative Numbers -2's Complement.

Subtracting a number is the same as:

- 1. Perform 2's complement

- 2. Perform addition

°If we can augment adder with 2's complement hardware?

$$1_{10} = 01_{16} = 00000001$$

$$-1_{10} = FF_{16} = 11111111$$

## 4-bit Subtractor: E = 1

Add  ${\bf A}$  to  ${\bf B'}$  (one's complement) plus 1

That is, add **A** to two's complement of **B D** = **A** - **B**

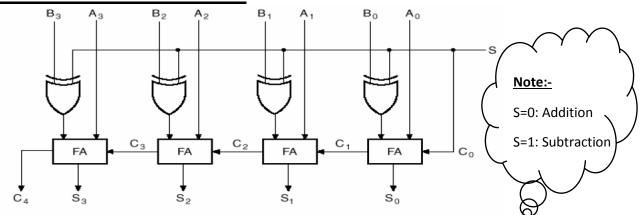

## **Adder-Subtractor Circuit**

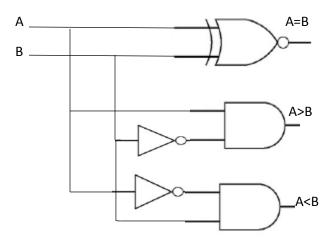

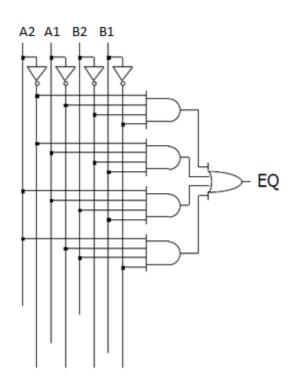

## **Digital Comparator**

Q) Compare two numbers each number has 1 bit

| Α | В | A=B | A>B | A <b< th=""></b<> |

|---|---|-----|-----|-------------------|

| 0 | 0 | 1   | 0   | 0                 |

| 0 | 1 | 0   | 0   | 1                 |

| 1 | 0 | 0   | 1   | 0                 |

| 1 | 1 | 1   | 0   | 0                 |

$A=B: A'B'+AB=(A \oplus B)'=A \odot B$

A>B: AB'

A<B: A'B

| <b>A</b> <sub>2</sub> | <b>A</b> <sub>1</sub> | B <sub>2</sub> | <b>B</b> <sub>1</sub> | A=B | A>B | A <b< th=""></b<> |

|-----------------------|-----------------------|----------------|-----------------------|-----|-----|-------------------|

| 0                     | 0                     | 0              | 0                     | 1   | 0   | 0                 |

| 0                     | 0                     | 0              | 1                     | 0   | 0   | 1                 |

| 0                     | 0                     | 1              | 0                     | 0   | 0   | 1                 |

| 0                     | 0                     | 1              | 1                     | 0   | 0   | 1                 |

| 0                     | 1                     | 0              | 0                     | 0   | 1   | 0                 |

| 0                     | 1                     | 0              | 1                     | 1   | 0   | 0                 |

| 0                     | 1                     | 1              | 0                     | 0   | 0   | 1                 |

| 0                     | 1                     | 1              | 1                     | 0   | 0   | 1                 |

| 1                     | 0                     | 0              | 0                     | 0   | 1   | 0                 |

| 1                     | 0                     | 0              | 1                     | 0   | 1   | 0                 |

| 1                     | 0                     | 1              | 0                     | 1   | 0   | 0                 |

| 1                     | 0                     | 1              | 1                     | 0   | 0   | 1                 |

| 1                     | 1                     | 0              | 0                     | 0   | 1   | 0                 |

| 1                     | 1                     | 0              | 1                     | 0   | 1   | 0                 |

| 1                     | 1                     | 1              | 0                     | 0   | 1   | 0                 |

| 1                     | 1                     | 1              | 1                     | 1   | 0   | 0                 |

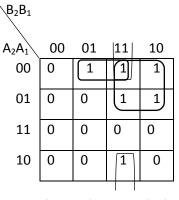

Q) Compare two numbers each number has 2 bits

$A=A_2A_1$ ,  $B=B_2B_1$

A=B:

$$(A_2=B_2)$$

and  $(A_1=B_1) = (A_2 \odot B_2).(A_1 \odot B_1)$

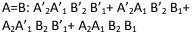

A>B:  $(A_2 > B_2)$  or  $((A_2 = B_2)$  and  $(A_1 > B_1)) = (A_2B'_2) + ((A_2 \bigcirc B_2).(A_1B'_1))$

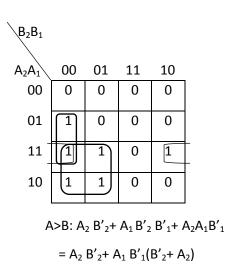

A<B:  $(A_2 < B_2)$  or  $((A_2 = B_2)$  and  $(A_1 < B_1)) = (A'_2B_2) + ((A_2 \bigcirc B_2).(A'_1B_1))$

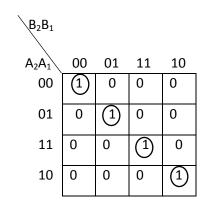

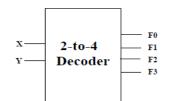

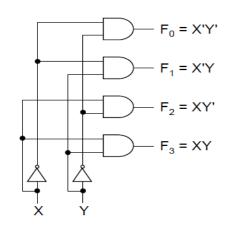

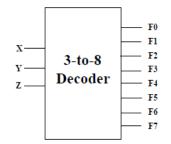

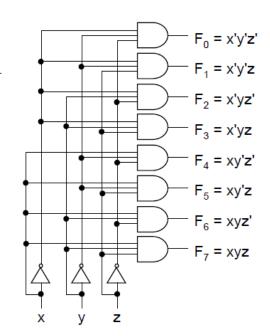

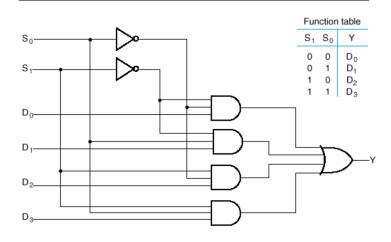

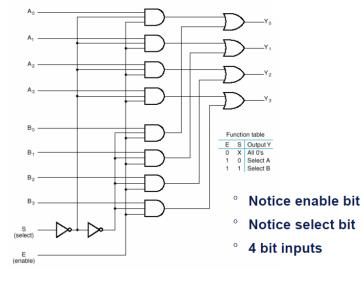

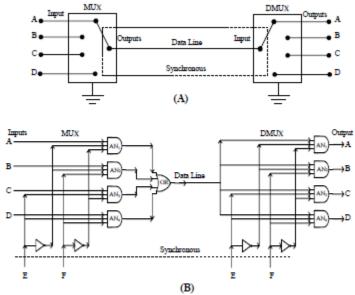

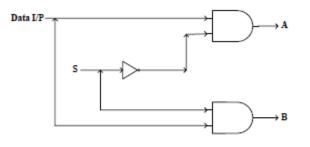

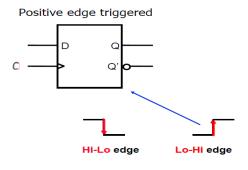

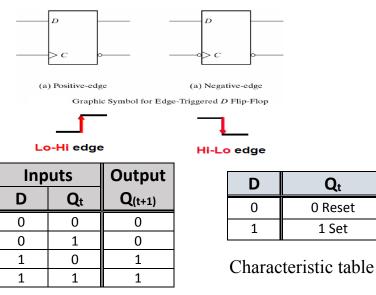

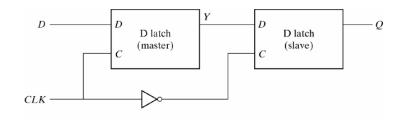

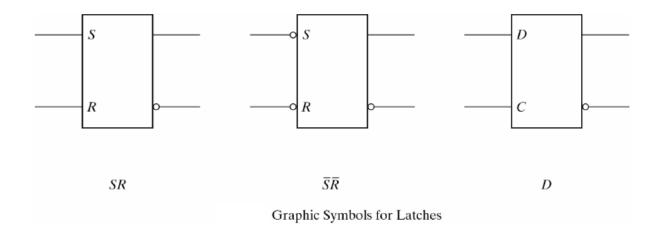

A=B: A'<sub>2</sub>A'<sub>1</sub> B'<sub>2</sub> B'<sub>1</sub>+ A'<sub>2</sub>A<sub>1</sub> B'<sub>2</sub> B<sub>1</sub>+ A<sub>2</sub>A'<sub>1</sub> B<sub>2</sub> B'<sub>1</sub>+ A<sub>2</sub>A<sub>1</sub> B<sub>2</sub> B<sub>1</sub>  $= A'2B'2(A'1B'1+A_1B_1)+A_2B_2(A'_1B'_1+A_1B_1)$  $= A'_{2}B'_{2}(A_{1} \odot B_{1}) + A_{2}B_{2}(A_{1} \odot B_{1}) = (A_{1} \odot B_{1})(A'_{2}B'_{2} + A_{2}B_{2}) = (A_{1} \odot B_{1})(A_{2} \odot B_{2})$