#### University of Technology Laser & Optoelectronics Engineering Department

#### DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 1: Digital Concepts: 2023-Sep-30

## Lecture Outline

- 1. Aim of the course

- 2. Number System (Decimal VS Binary)

- 3. Counting in Binary

- 4. Conversions

- 5. HW

#### **Aim of the Course**

Study the following general topics

- 1. Number Systems

- 2. Arithmetic Operations

- 3. Logic Gates

- 4. Boolean Algebra

- 5. Logic Simplification

- 6. Combinational Logic Analysis

- 7. Function of combinational logic

- 8. Latches, Filp-Flops, Timers

- 9. Counters

- 10. Shift Registers

- 11. Memory

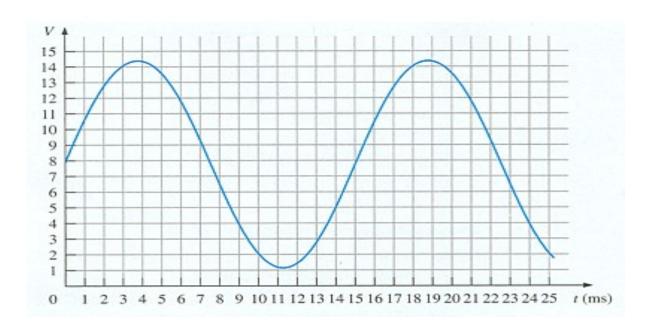

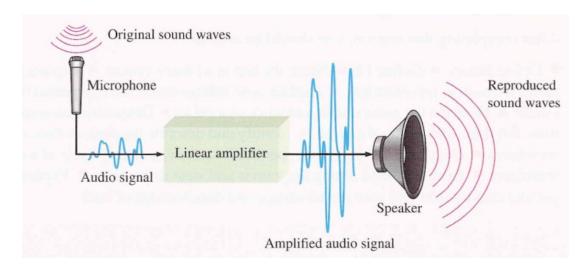

#### Analog Vs Digital Signal

Analog quantities have continuous values

Digital quantities have discrete sets of values

#### Types of electronic devices or instruments:

- Analog

- Digital

- Combination analog and digital

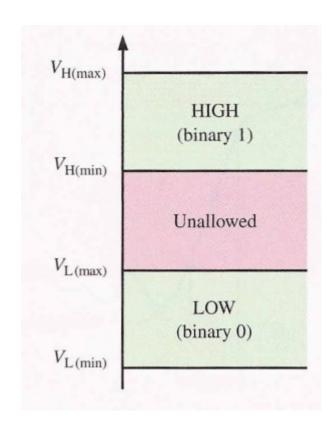

- A. The conventional numbering system uses ten digits: 0,1,2,3,4,5,6,7,8, and 9.

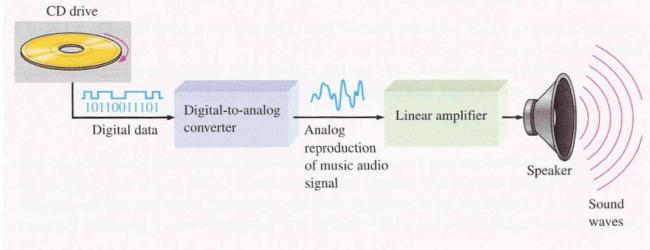

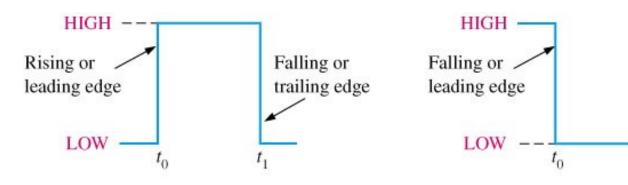

- B. The binary numbering system uses just two digits: 0 and 1.

- C. The two binary digits are designated **0** and **1**

- D. They can also be called LOW and HIGH, where LOW = 0 and HIGH = 1

(a) Positive-going pulse

(b) Negative-going pulse

Rising or

trailing edge

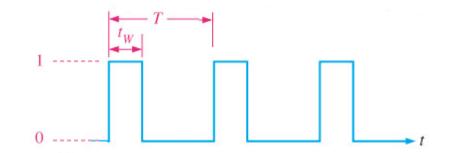

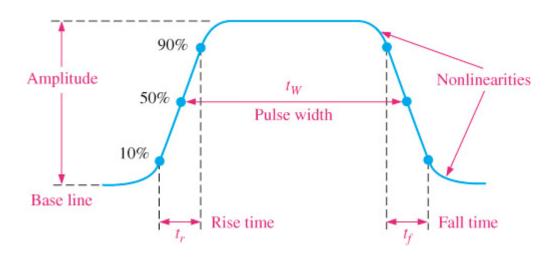

#### Digital Pulse

#### Major parts of a digital pulse

- 1. Base line

- 2. Amplitude

- 3. Rise time (t<sub>r</sub>)

- 4. Pulse width (t<sub>w</sub>)

- 5. Fall time (t<sub>f</sub>)

$$f = \frac{1}{T}$$

Duty cycle =  $\left(\frac{t_w}{T}\right)$ 100%

t<sub>w</sub> = pulse widthT = period of the waveformf = frequency of the waveform

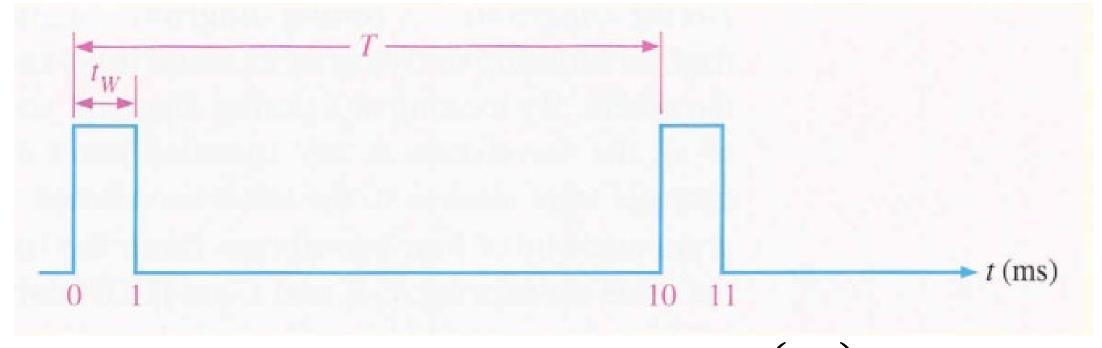

## Example 1

$$T=10 mS$$

$$f=\frac{1}{T}=100~Hz$$

Duty cycle =

$$\left(\frac{t_{w}}{T}\right)100\%$$

Duty cycle =

$$\left(\frac{1 ms}{10 ms}\right) 100\% = 10\%$$

#### **Logic Gates**

#### There are only three basic logic operations:

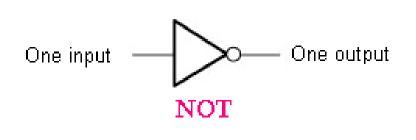

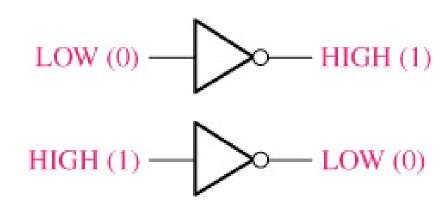

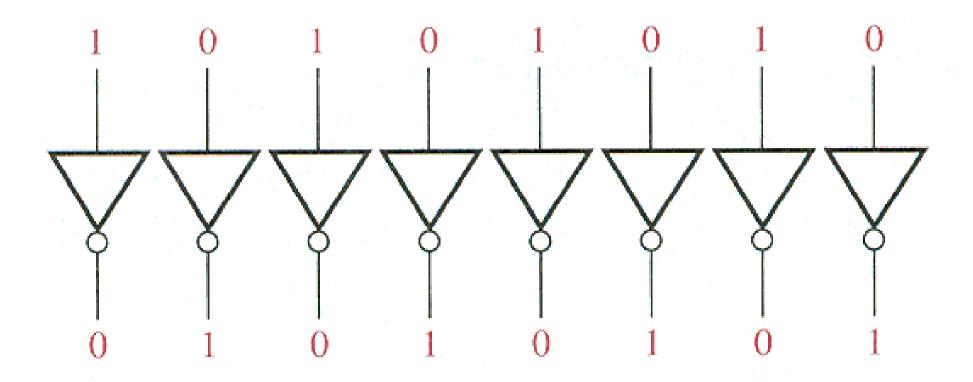

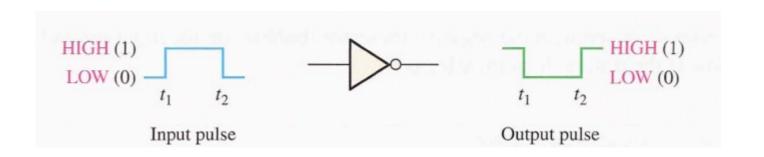

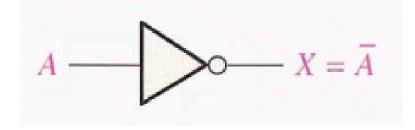

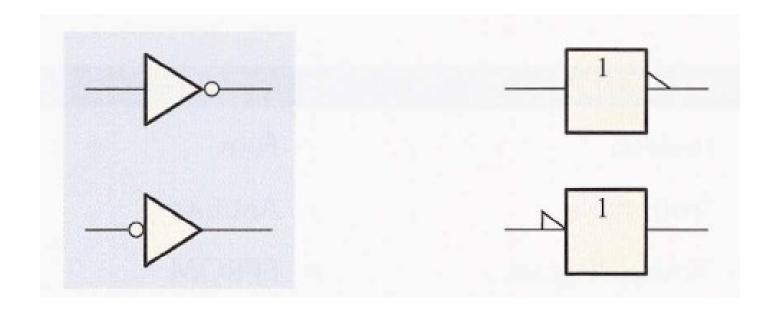

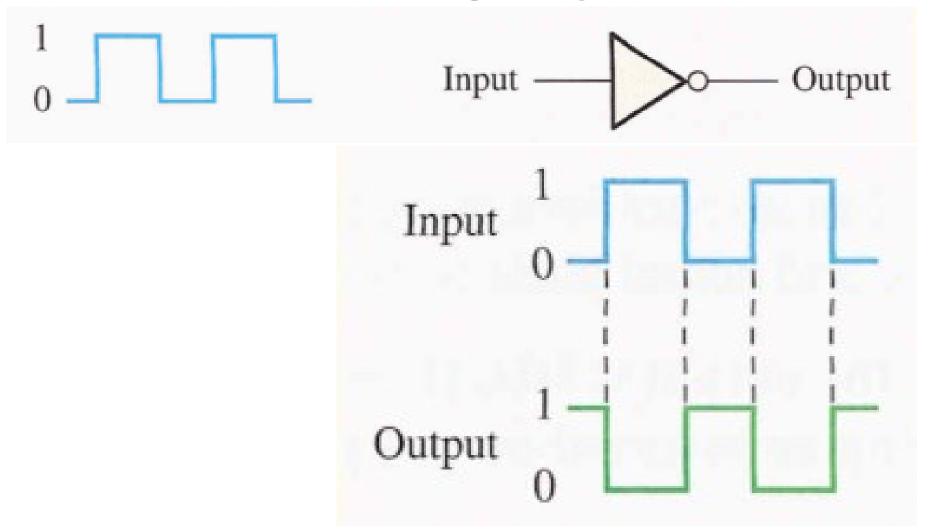

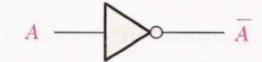

#### **NOT Gate Operation**

input is LOW, output is HIGH input is HIGH, output is LOW

The output logic level is always opposite the input logic level.

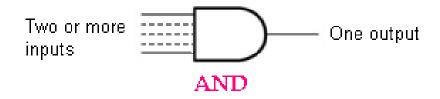

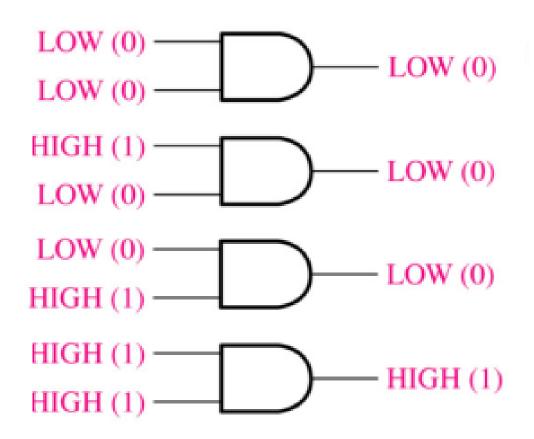

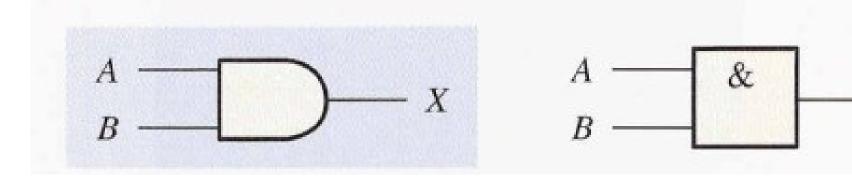

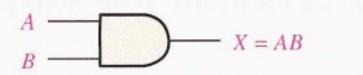

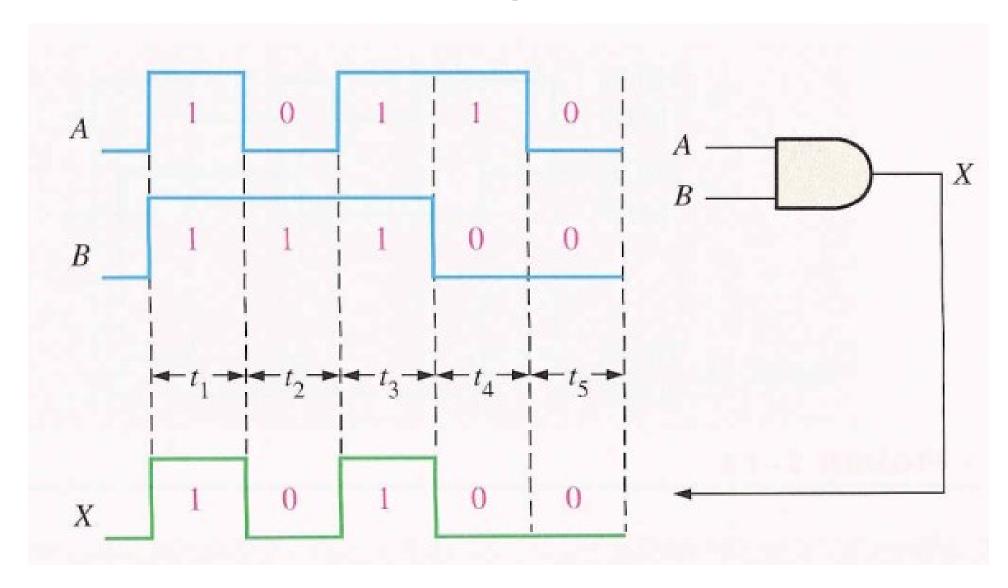

#### **AND Gate Operation**

When any input is LOW, the output is LOW

When both inputs are

HIGH, the output is HIGH

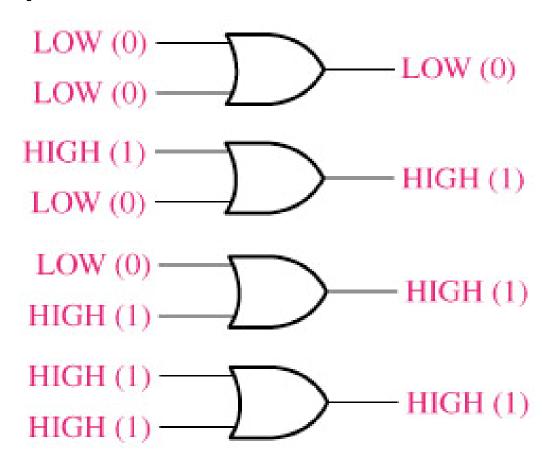

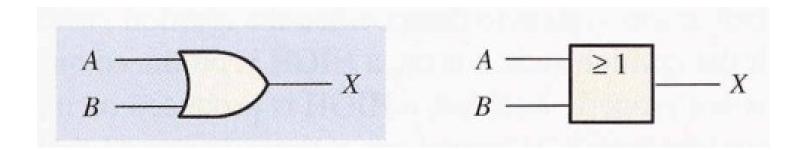

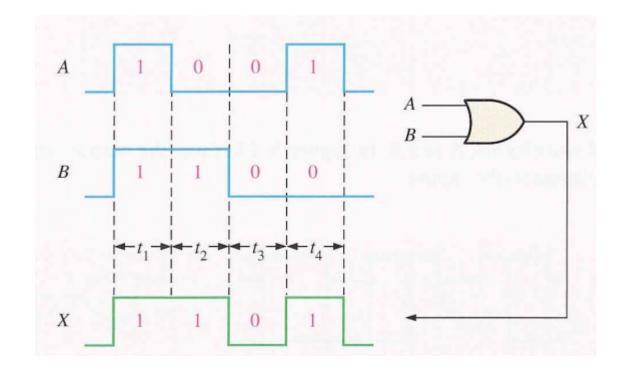

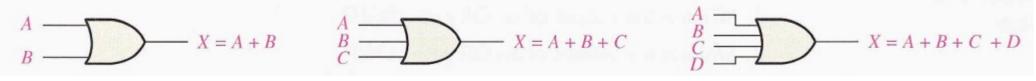

## OR Gate Operation

When any input is HIGH, the output is HIGH When both inputs are LOW, the output is LOW

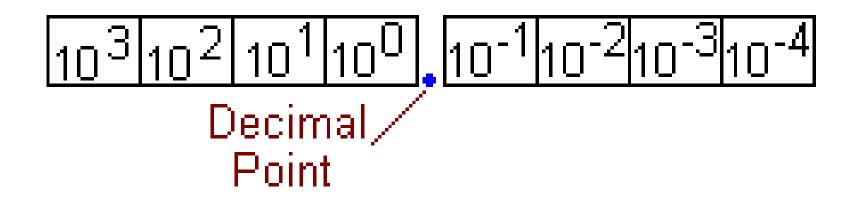

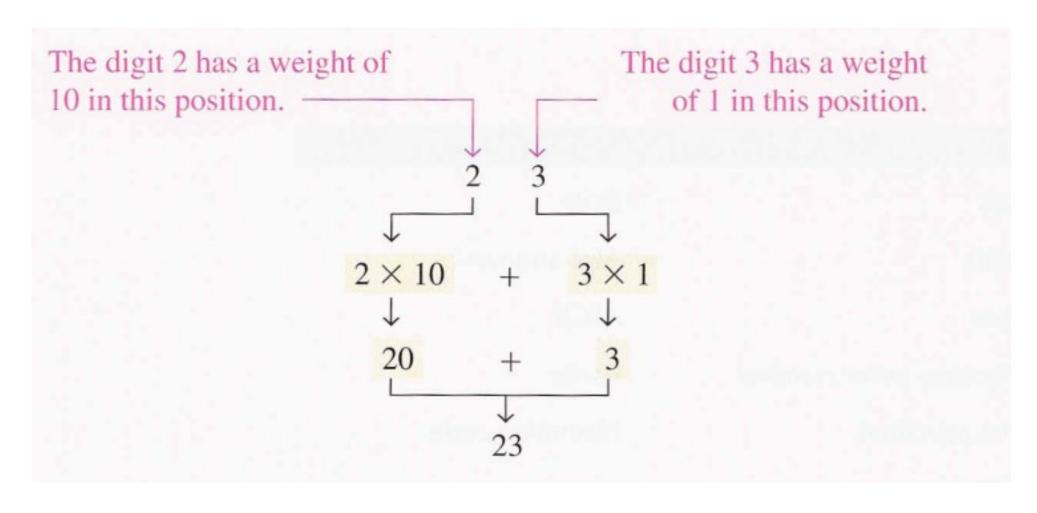

### **Decimal Numbers**

The decimal number system has ten digits:

0, 1, 2, 3, 4, 5, 6, 7, 8, and 9

The decimal numbering system has a base of 10 with each position weighted by a factor of 10:

## **Binary Numbers**

The binary number system has two digits: 0 and 1

The binary numbering system has a base of 2 with each position weighted by a factor of 2:

| POSITIVE POWERS OF TWO (WHOLE NUMBERS) |                       |                |                       | NEGATIVE POWERS OF TWO  (FRACTIONAL NUMBER) |                |                       |                       |                       |                 |                 |                 |                 |                 |                 |

|----------------------------------------|-----------------------|----------------|-----------------------|---------------------------------------------|----------------|-----------------------|-----------------------|-----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 2 <sup>8</sup>                         | <b>2</b> <sup>7</sup> | 2 <sup>6</sup> | <b>2</b> <sup>5</sup> | <b>2</b> <sup>4</sup>                       | 2 <sup>3</sup> | <b>2</b> <sup>2</sup> | <b>2</b> <sup>1</sup> | <b>2</b> <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> |

| 256                                    | 128                   | 64             | 32                    | 16                                          | 8              | 4                     | 2                     | 1                     | 1/2             | 1/4             | 1/8             | 1/16            | 1/32            | 1/64            |

|                                        |                       |                |                       |                                             |                |                       |                       |                       | 0.5             | 0.25            | 0.125           | 0.0625          | 0.03125         | 0.015625        |

## Sum of Weight

### Conversions

Convert the binary whole number 1101101 to decimal.

Determine the weight of each bit that is a 1, and then find the sum of the weights to get the decimal number.

Weight:

$$2^6 \ 2^5 \ 2^4 \ 2^3 \ 2^2 \ 2^1 \ 2^0$$

Binary number:  $1 \ 1 \ 0 \ 1 \ 1 \ 0 \ 1$

$1101101 = 2^6 + 2^5 + 2^3 + 2^2 + 2^0$

$= 64 + 32 + 8 + 4 + 1 = 109$

### Conversions

Convert the fractional binary number 0.1011 to decimal.

Determine the weight of each bit that is a 1, and then sum the weights to get the decimal fraction.

Weight:

$$2^{-1}$$

$2^{-2}$   $2^{-3}$   $2^{-4}$

Binary number:  $0.1$   $0$   $1$   $1$

$0.1011 = 2^{-1} + 2^{-3} + 2^{-4}$

$= 0.5 + 0.125 + 0.0625 = 0.6875$

## Conversions

Convert the following decimal numbers to binary:

(a)

$$12 = 8 + 4 = 2^3 + 2^2 \longrightarrow 1100$$

**(b)**

$$25 = 16 + 8 + 1 = 2^4 + 2^3 + 2^0 \longrightarrow 11001$$

(c)

$$58 = 32 + 16 + 8 + 2 = 2^5 + 2^4 + 2^3 + 2^1 \longrightarrow 111010$$

(d)

$$82 = 64 + 16 + 2 = 2^6 + 2^4 + 2^1 \longrightarrow 1010010$$

## Addition in Binary Rules

| Α | 0 + 0 = 0  | Sum of 0 with a carry of 0 |

|---|------------|----------------------------|

| В | 0 + 1 = 1  | Sum of 1 with a carry of 0 |

| C | 1 + 0 = 1  | Sum of 1 with a carry of 0 |

| D | 1 + 1 = 10 | Sum of 0 with a carry of 1 |

| Ε | 1+1+1 = 11 | Sum of 1 with a carry of 1 |

## Addition in Binary Examples

Add the following binary numbers:

(a)

$$11 + 11$$

**(b)**

$$100 + 10$$

(c)

$$111 + 11$$

(a)

$$11 + 11$$

(b)  $100 + 10$  (c)  $111 + 11$  (d)  $110 + 100$

The equivalent decimal addition is also shown for reference.

(a)

$$11 3 +11 +3 6$$

$$\frac{4}{+2}$$

b)

$$100$$

4 (c)  $111$   $+10$   $+2$   $+11$   $1010$

$$\frac{7}{+3}$$

(d)

$$110$$

6  $+100$   $+4$   $10$  10

## Subtraction in Binary Rules

$$0 - 0 = 0$$

$1 - 1 = 0$

$1 - 0 = 1$

$10 - 1 = 1$   $0 - 1$  with a borrow of 1

## Subtraction in Binary Example

Perform the following binary subtractions:

(a)

$$11 - 01$$

(b)  $11 - 10$

(a)  $11$  3 (b)  $11$  3  $-01$   $-1$   $-10$   $-2$   $-10$   $-2$   $01$  1

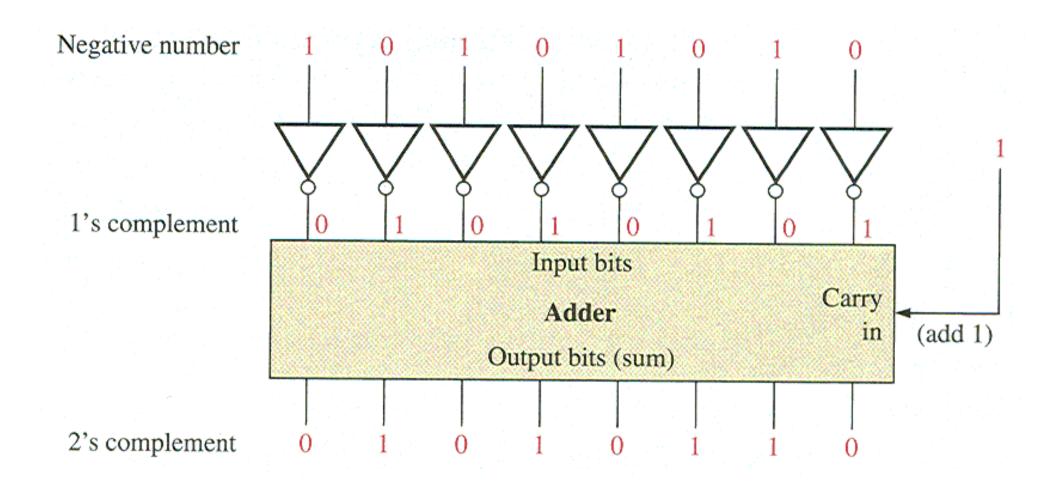

## 1's complement

## 2's complement

### References

Ref 1

Ref 2

## Home Work (Due date 08-10-2023)

- 1. Prepare a report on Digital gates applications in Laser Engineering (3 Pages)

- 2. Solve the following questions

- A. Convert the number 110011.10011 to decimal

- B. Convert the number 111 to binary

- C. Add  $100_2 + 100_{10}$  and write the result both in binary and decimal

- D. Subtract  $10110_2 10_{10}$  and write the result both in binary and decimal

Note: Home works are to be uploaded via the below google form <a href="https://forms.gle/XuMw9LzCuZnnxGiZ7">https://forms.gle/XuMw9LzCuZnnxGiZ7</a>

## Telegram Group

## UNIVERSITY OF TECHNOLOGY LASER & OPTOELECTRONICS ENGINEERING DEPARTMENT

#### DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 2: Number System Arithmetic: 2023-Oct-15

#### **Lecture Outline**

- 1. Decimal to binary conversion methods

- 2. Binary Multiplication and Division

- 3. Signed Binary Numbers

- 4. Hexadecimal Numbers: Conversion and Arithmetic

- 5. Octal Numbers

- 6. HW

# Decimal and Binary Representation

| DECIMAL<br>NUMBER |   | BINARY N | NUMBE | R |

|-------------------|---|----------|-------|---|

| 0                 | 0 | 0        | 0     | 0 |

| 1                 | 0 | 0        | 0     | 1 |

| 2                 | 0 | 0        | 1     | 0 |

| 3                 | 0 | 0        | 1     | 1 |

| 4                 | 0 | 1        | 0     | 0 |

| 5                 | 0 | 1        | 0     | 1 |

| 6                 | 0 | 1        | 1     | 0 |

| 7                 | 0 | 1        | 1     | 1 |

| 8                 | 1 | 0        | 0     | 0 |

| 9                 | 1 | 0        | 0     | 1 |

| 10                | 1 | 0        | 1     | 0 |

| 11                | 1 | 0        | 1     | 1 |

| 12                | 1 | 1        | 0     | 0 |

| 13                | 1 | 1        | 0     | 1 |

| 14                | 1 | 1        | 1     | 0 |

| 15                | 1 | 1        | 1     | 1 |

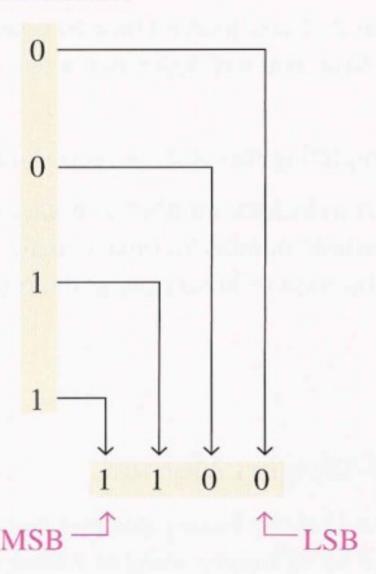

#### Repeated Division-by-2 Method

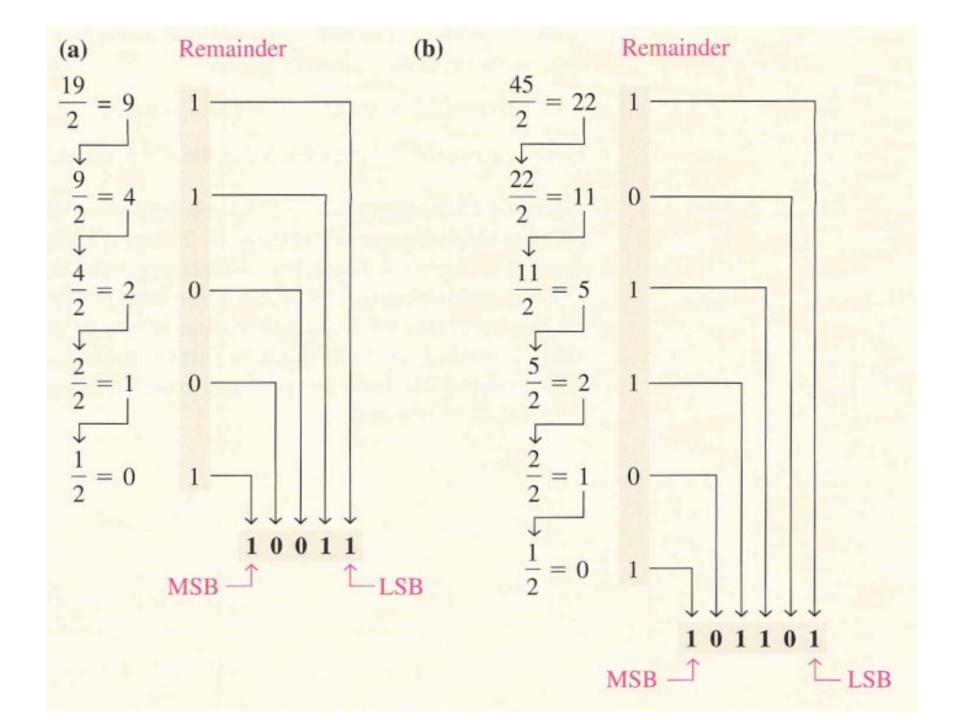

A systematic method of converting whole numbers from decimal to binary is the *repeated division-by-2* process. For example, to convert the decimal number 12 to binary, begin by dividing 12 by 2. Then divide each resulting quotient by 2 until there is a 0 whole-number quotient. The **remainders** generated by each division form the binary number. The first remainder to be produced is the LSB (least significant bit) in the binary number, and the last remainder to be produced is the MSB (most significant bit). This procedure is shown in the following steps for converting the decimal number 12 to binary.

#### Convert the following decimal numbers to binary:

(a) 19 (b) 45

#### Remainder

$$\frac{12}{2} = 6$$

$$\frac{6}{2} = 3$$

$$\frac{3}{2} = 1$$

$$\frac{1}{2} = 0$$

Stop when the whole-number quotient is 0.

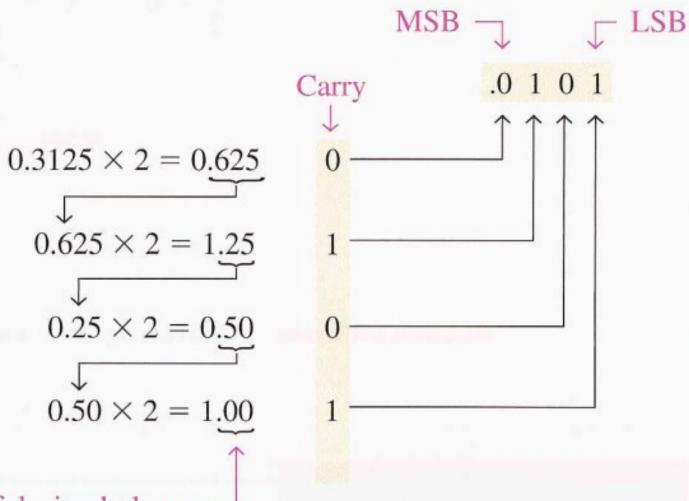

Repeated Multiplication by 2 As you have seen, decimal whole numbers can be converted to binary by repeated division by 2. Decimal fractions can be converted to binary by repeated multiplication by 2. For example, to convert the decimal fraction 0.3125 to binary, begin by multiplying 0.3125 by 2 and then multiplying each resulting fractional part of the product by 2 until the fractional product is zero or until the desired number of decimal places is reached. The carry digits, or carries, generated by the multiplications produce the binary number. The first carry produced is the MSB, and the last carry is the LSB. This procedure is illustrated as follows:

Continue to the desired number of decimal places—or stop when the fractional part is all zeros.

# Binary Multiplication and Division

$$0 \times 0 = 0$$

$1 \times 0 = 0$

$0 \times 1 = 0$   $1 \times 1 = 1$

Perform the following binary multiplications:

(a)

$$11 \times 11$$

(b)  $101 \times 111$

(a) 11 3 (b) 111 7

$$\times 11$$

$\times 3$  Partial 11 9 Partial products  $+11$  products  $000$   $+111$   $10001$

Perform the following binary divisions:

(a)

$$110 \div 11$$

(b)  $110 \div 10$

# Signed Binary Numbers

Digital systems, such as the computer, must be able to handle both positive and negative numbers. A signed binary number consists of both sign and magnitude information. The sign indicates whether a number is positive or negative, and the magnitude is the value of the number. There are three forms in which signed integer (whole) numbers can be represented in binary: sign-magnitude, 1's complement, and 2's complement. Of these, the 2's complement is the most important and the sign-magnitude is the least used. Noninteger and very large or small numbers can be expressed in floating-point format.

The decimal number -25 is expressed as

10011001

Sign Bit

Magnitude Bit

1 0

-ve +ve

Single-Precision Floating-Point Binary Numbers In the standard format for a single-precision binary number, the sign bit (S) is the left-most bit, the exponent (E) includes the next eight bits, and the mantissa or fractional part (F) includes the remaining 23 bits, as shown next.

Number =

$$(-1)^{S}(1 + F)(2^{E-127})$$

Convert the decimal number  $3.248 \times 10^4$  to a single-precision floating-point binary number.

Convert the decimal number to binary.

$$3.248 \times 10^4 = 32480 = 11111110111100000_2 = 1.11111101111000000 \times 2^{14}$$

The MSB will not occupy a bit position because it is always a 1. Therefore, the mantissa is the fractional 23-bit binary number 1111110111000000000000000 and the biased exponent is

$$14 + 127 = 141 = 10001101_2$$

The complete floating-point number is

10001101

11111011110000000000000000

# Hexadecimal Numbers

| $16^{3}$ | $16^{2}$ | $16^{1}$ | $16^{0}$ |

|----------|----------|----------|----------|

| 4096     | 256      | 16       | 1        |

| DECIMAL | BINARY | HEXADECIMAL |

|---------|--------|-------------|

| 0       | 0000   | 0           |

| 1       | 0001   | 1           |

| 2       | 0010   | 2           |

| 3       | 0011   | 3           |

| 4       | 0100   | 4           |

| 5       | 0101   | 5           |

| 6       | 0110   | 6           |

| 7       | 0111   | 7           |

| 8       | 1000   | 8           |

| 9       | 1001   | 9           |

| 10      | 1010   | A           |

| 11      | 1011   | В           |

| 12      | 1100   | C           |

| 13      | 1101   | D           |

| 14      | 1110   | Е           |

| 15      | 1111   | F           |

|         |        |             |

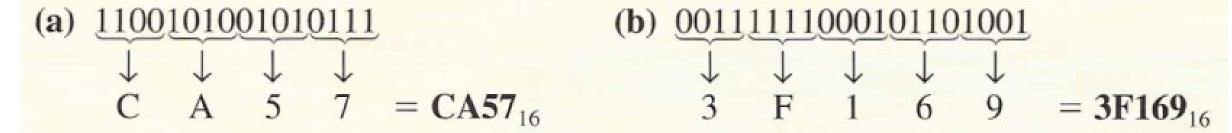

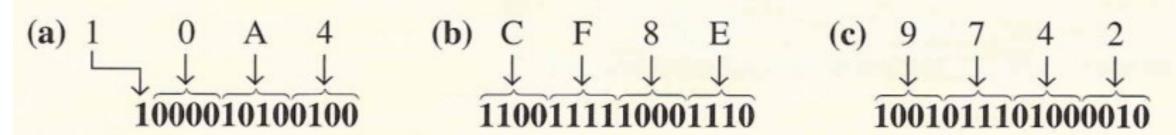

Convert the following binary numbers to hexadecimal:

(a) 11001010010101111 (b) 1111111000101101001

Two zeros have been added in part (b) to complete a 4-bit group at the left.

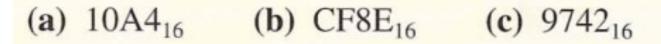

Determine the binary numbers for the following hexadecimal numbers:

In part (a), the MSB is understood to have three zeros preceding it, thus forming a 4-bit group.

Convert the following hexadecimal numbers to decimal:

(a)

$$1C_{16}$$

(b)  $A85_{16}$

Remember, convert the hexadecimal number to binary first, then to decimal.

(a)

$$1 \quad C$$

$00011100 = 2^4 + 2^3 + 2^2 = 16 + 8 + 4 = 28_{10}$

Convert the following hexadecimal numbers to decimal:

(a)

$$E5_{16}$$

(b)  $B2F8_{16}$

Recall from Table 2–3 that letters A through F represent decimal numbers 10 through 15, respectively.

(a)

$$E5_{16} = (E \times 16) + (5 \times 1) = (14 \times 16) + (5 \times 1) = 224 + 5 = 229_{10}$$

Convert the decimal number 650 to hexadecimal by repeated division by 16.

## Hexadecimal remainder

$$\frac{650}{16} = 40.625 \rightarrow 0.625 \times 16 = 10 = A$$

$$\frac{40}{16} = 2.5 \longrightarrow 0.5 \times 16 = 8 = 8$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

$$\frac{2}{16} = 0.125 \longrightarrow 0.125 \times 16 = 2 = 2$$

Add the following hexadecimal numbers:

(a)

$$23_{16} + 16_{16}$$

(b)  $58_{16} + 22_{16}$  (c)  $2B_{16} + 84_{16}$  (d)  $DF_{16} + AC_{16}$

(a)

$$23_{16}$$

right column:  $3_{16} + 6_{16} = 3_{10} + 6_{10} = 9_{10} = 9_{16}$

$+16_{16}$  left column:  $2_{16} + 1_{16} = 2_{10} + 1_{10} = 3_{10} = 3_{16}$

(b)

$$58_{16}$$

right column:  $8_{16} + 2_{16} = 8_{10} + 2_{10} = 10_{10} = A_{16}$

$+ 22_{16}$  left column:  $5_{16} + 2_{16} = 5_{10} + 2_{10} = 7_{10} = 7_{16}$

(c)

$$2B_{16}$$

right column:  $B_{16} + 4_{16} = 11_{10} + 4_{10} = 15_{10} = F_{16}$

$+ 84_{16}$  left column:  $2_{16} + 8_{16} = 2_{10} + 8_{10} = 10_{10} = A_{16}$

(d) DF<sub>16</sub> right column:

$$F_{16} + C_{16} = 15_{10} + 12_{10} = 27_{10}$$

$+ AC_{16}$   $27_{10} - 16_{10} = 11_{10} = B_{16}$  with a 1 carry left column:  $D_{16} + A_{16} + 1_{16} = 13_{10} + 10_{10} + 1_{10} = 24_{10}$

$24_{10} - 16_{10} = 8_{10} = 8_{16}$  with a 1 carry

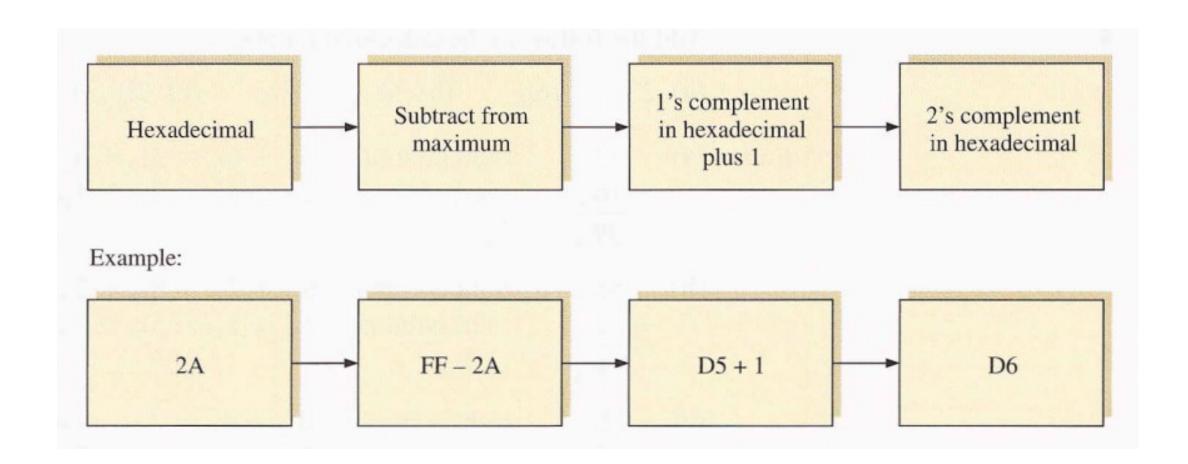

Subtract the following hexadecimal numbers:

(a)

$$84_{16} - 2A_{16}$$

(b)  $C3_{16} - 0B_{16}$

(a)  $2A_{16} = 00101010$

2's complement of  $2A_{16} = 11010110 = D6_{16}$  (using Method 1)

$$84_{16}$$

$+ D6_{16}$

Add

$15A_{16}$

Drop carry, as in 2's complement addition

The difference is  $5A_{16}$ .

**(b)**

$$0B_{16} = 00001011$$

2's complement of  $0B_{16} = 11110101 = F5_{16}$  (using Method 1)

$$C3_{16}$$

+  $F5_{16}$

Add

$B8_{16}$

Drop carry

The difference is  $\mathbf{B8}_{16}$ .

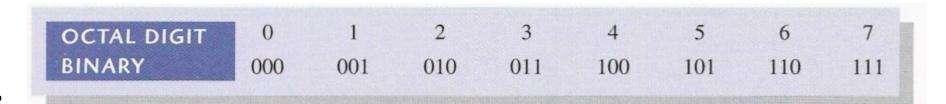

# Octal Numbers

Convert each of the following octal numbers to binary:

(a) 13<sub>8</sub>

- **(b)** 25<sub>8</sub>

- (c)  $140_8$

- (d) 7526<sub>8</sub>

(a)  $1 \ 3$   $\downarrow \ \downarrow$  001011

(b)  $\begin{array}{ccc} 2 & 5 \\ \downarrow & \downarrow \\ \hline 010101 \\ \end{array}$

- (c)  $1 \ 4 \ 0$   $\downarrow \ \downarrow \ \downarrow$ 001100000

- (d) 7 5 2 6  $\downarrow \downarrow \downarrow \downarrow \downarrow \downarrow$  111101010110

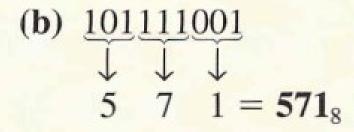

Convert each of the following binary numbers to octal:

- (a) 110101

- **(b)** 1011111001

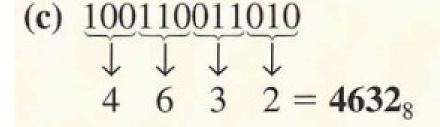

- (c) 100110011010

- (d) 11010000100

(a)

$$110101$$

$6$   $5 = 65_8$

(d)

$$011010000100$$

$\downarrow \qquad \downarrow \qquad \downarrow \qquad \downarrow$

$3 \quad 2 \quad 0 \quad 4 = 3204_8$

```

Convert each hexadecimal number to binary:

(a) 38_{16} (b) 59_{16} (c) A14_{16} (d) 5C8_{16}

(e) 4100_{16} (f) FB17_{16} (g) 8A9D_{16}

Convert each binary number to hexadecimal:

(b) 10 (c) 10111

(a) 1110

(d) 10100110 (e) 11111110000 (f) 100110000010

Convert each hexadecimal number to decimal:

(a) 23_{16} (b) 92_{16} (c) 1A_{16} (d) 8D_{16}

(e) F3_{16} (f) EB_{16} (g) 5C2_{16}

(h) 700<sub>16</sub>

Convert each decimal number to hexadecimal:

(a) 8 (b) 14 (c) 33

(d) 52

(g) 4019

(e) 284 (f) 2890

(h) 6500

Perform the following additions:

(a) 37_{16} + 29_{16} (b) A0_{16} + 6B_{16} (c) FF_{16} + BB_{16}

Perform the following subtractions:

(a) 51_{16} - 40_{16} (b) C8_{16} - 3A_{16} (c) FD_{16} - 88_{16}

```

# Home Work (Due date 20-10-2023)

Note: Home works are to be uploaded via the below google form

https://forms.gle/7a 6PJtNdTZdEZDUBA

#### University of Technology Laser & Optoelectronics Engineering Department

#### DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 3: Logic Gates and their Applications: 2023-Oct-22

### Lecture Outline

- 1. NOT GATE

- 2. AND GATE

- 3. OR GATE

- 4. NAND GATE

- 5. NOR GATE

- 6. XOR GATE

- 7. XNOR GATE

- 8. Writing Boolean Expression

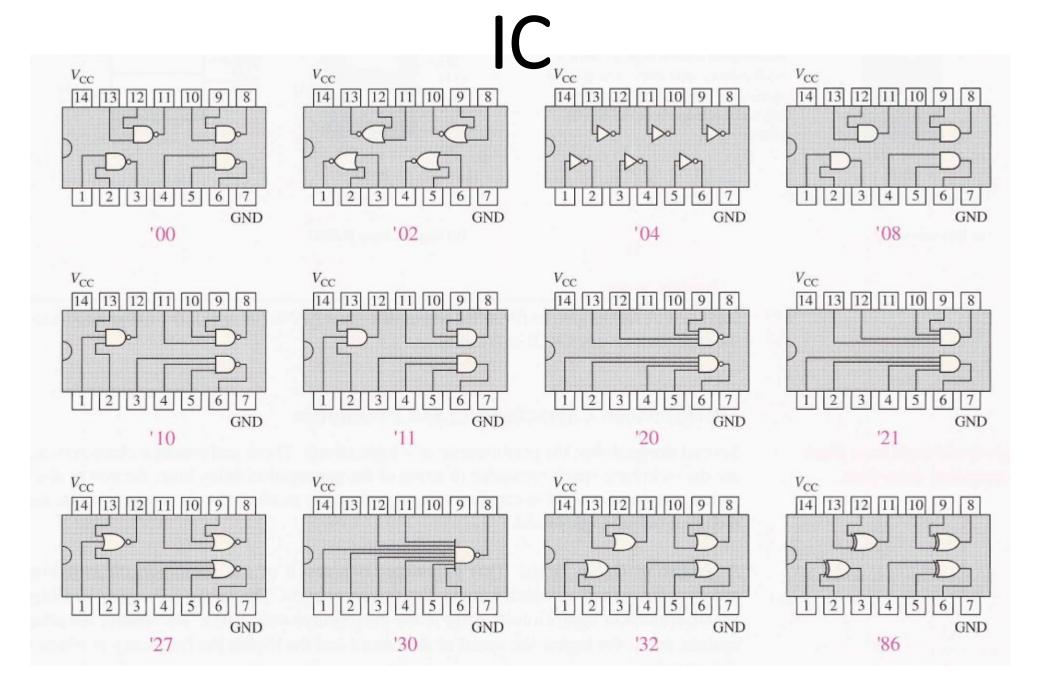

- 9. IC

- 10.Datasheet

- **11.HW**

## NOT GATE

| INPUT    | OUTPUT   |

|----------|----------|

| LOW (0)  | HIGH (1) |

| HIGH (1) | LOW (0)  |

## NOT GATE

## AND GATE

| 0.0         | = | 0 |

|-------------|---|---|

| $0 \cdot 1$ | = | 0 |

| 1.0         | = | 0 |

| 1 · 1       | = | 1 |

| INPUTS |   | OUTPUT |

|--------|---|--------|

| Α      | В | X      |

| 0      | 0 | 0      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 1      |

$$X = AB$$

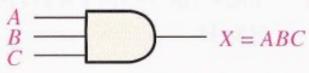

For two input variables:  $N = 2^2 = 4$  combinations

For three input variables:  $N = 2^3 = 8$  combinations

For four input variables:  $N = 2^4 = 16$  combinations

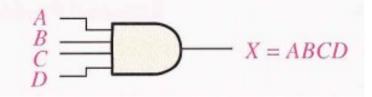

## AND GATE

|   | INPUTS |   | OUTPUT |

|---|--------|---|--------|

| Α | В      | С | X      |

| 0 | 0      | 0 | 0      |

| 0 | 0      | 1 | 0      |

| 0 | 1      | 0 | 0      |

| 0 | 1      | 1 | 0      |

| 1 | 0      | 0 | 0      |

| 1 | 0      | 1 | 0      |

| 1 | 1      | 0 | 0      |

| 1 | 1      | 1 | 1      |

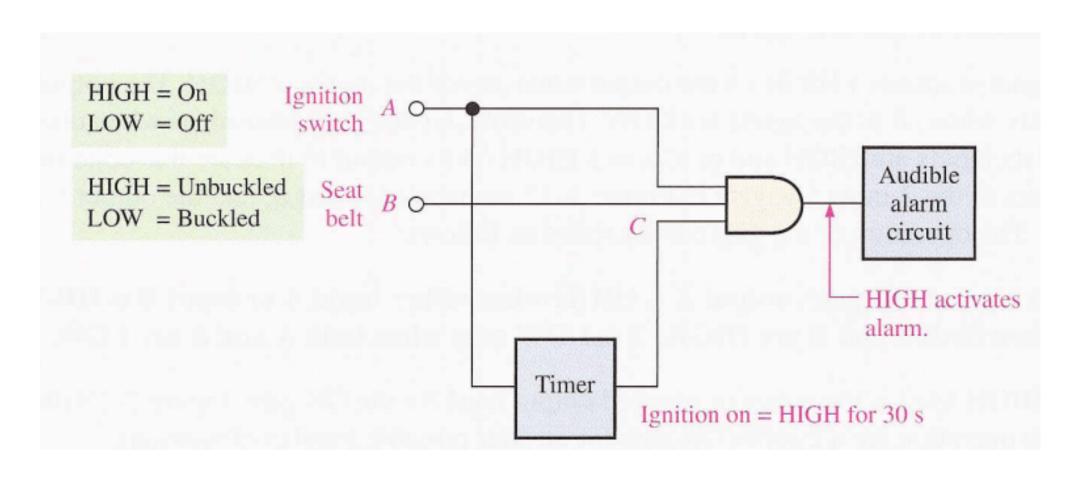

## AND GATE

#### A simple seat belt alarm circuit using an AND gate.

## OR GATE

| INP | UTS | OUTPUT |

|-----|-----|--------|

| Α   | В   | X      |

| 0   | 0   | 0      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 1      |

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 0 = 1$

$1 + 1 = 1$

$$X = A + B$$

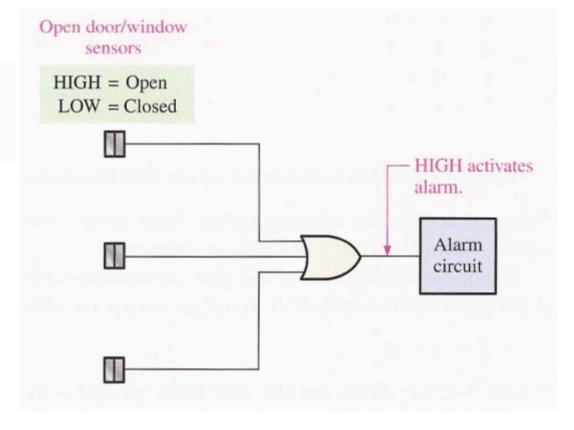

## OR GATE

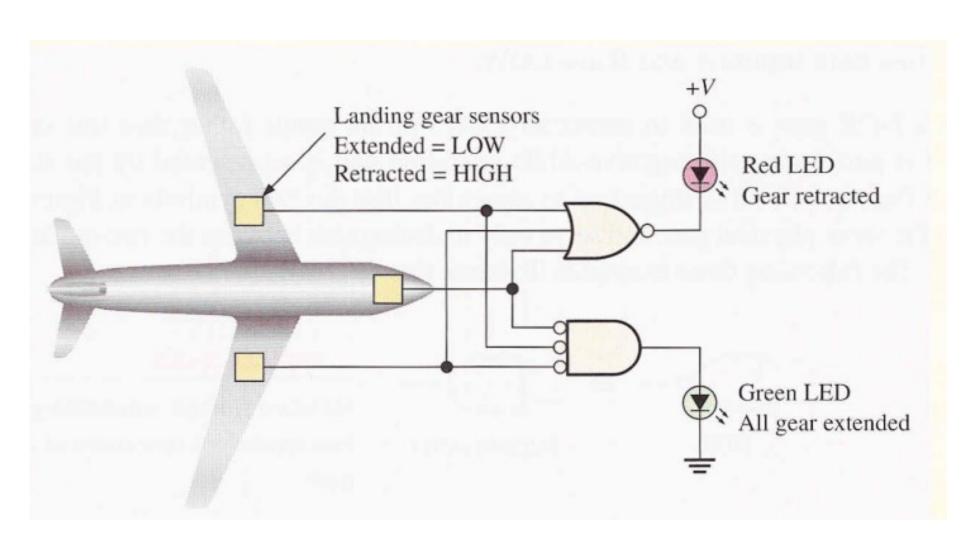

A simplified intrusion detection system using an OR gate.

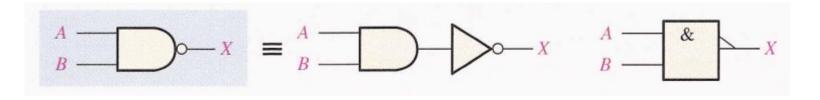

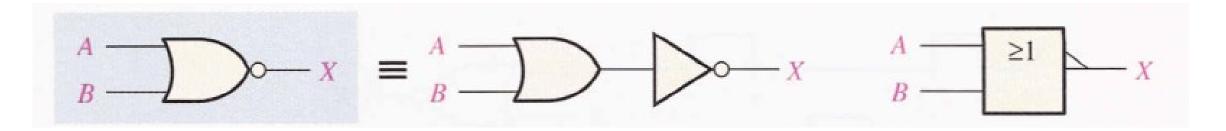

## NAND GATE

| INPUTS |   | OUTPUT |

|--------|---|--------|

| Α      | В | X      |

| 0      | 0 | 1      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

$$X = \overline{AB}$$

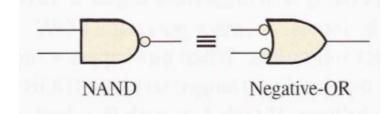

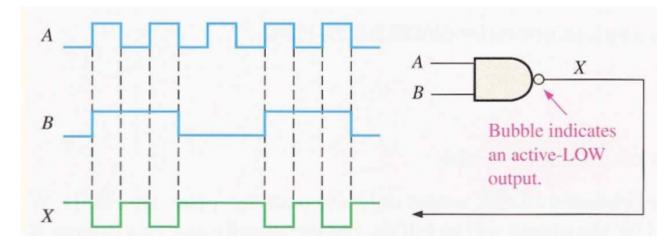

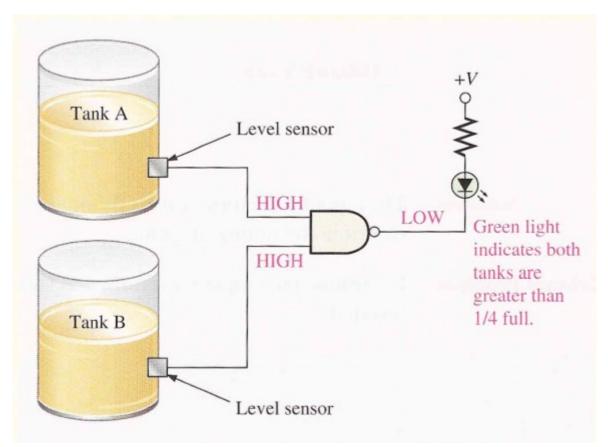

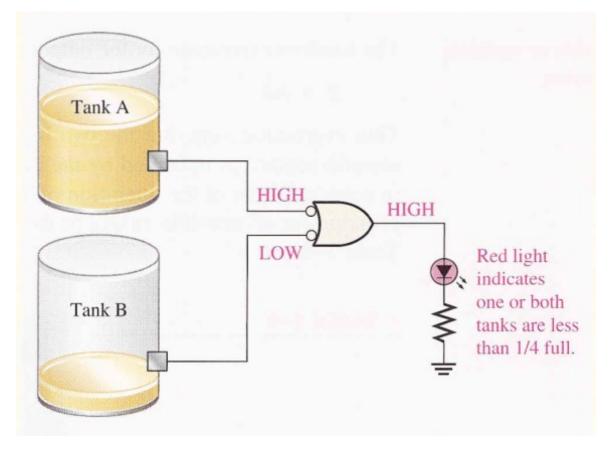

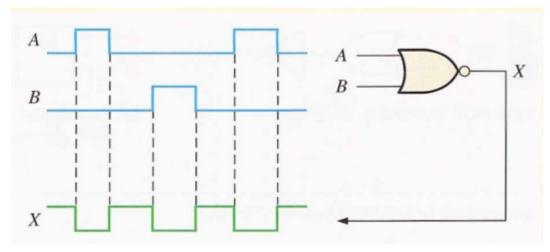

## NAND GATE

## NOR GATE

| INPUTS |   | OUTPUT |

|--------|---|--------|

| Α      | В | X      |

| 0      | 0 | 1      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 0      |

$$X = A + B$$

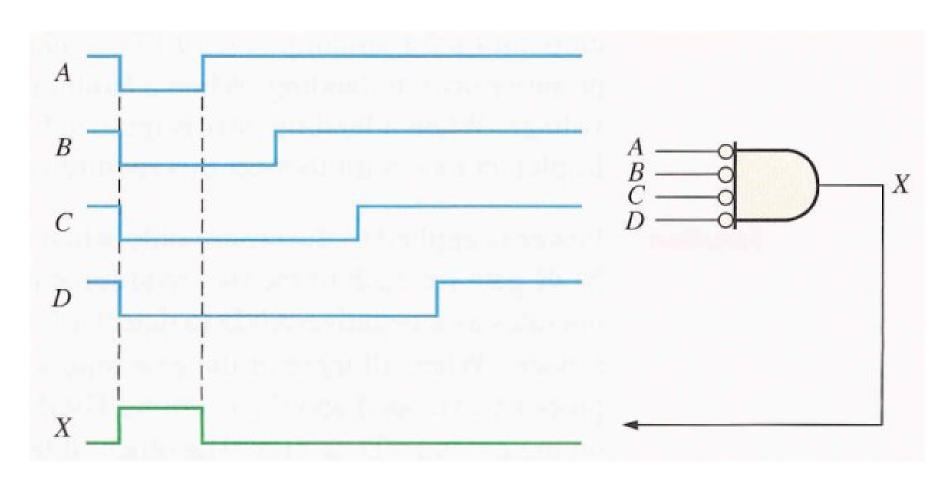

## NOR GATE

## NOR GATE

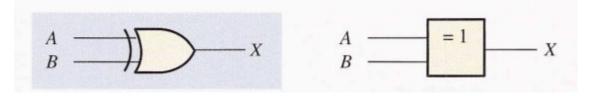

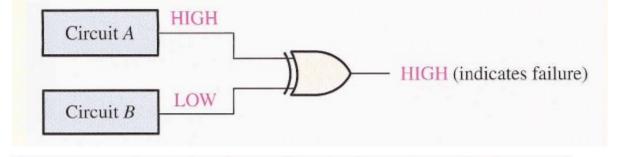

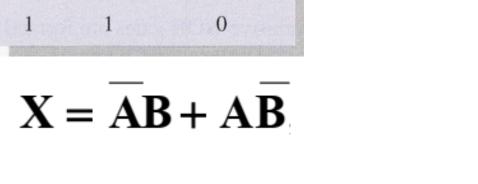

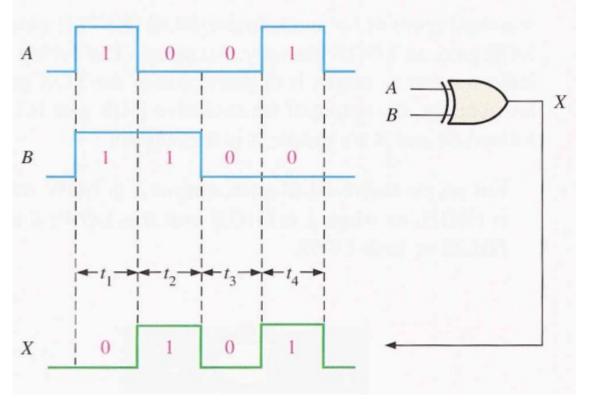

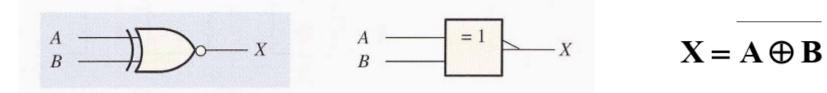

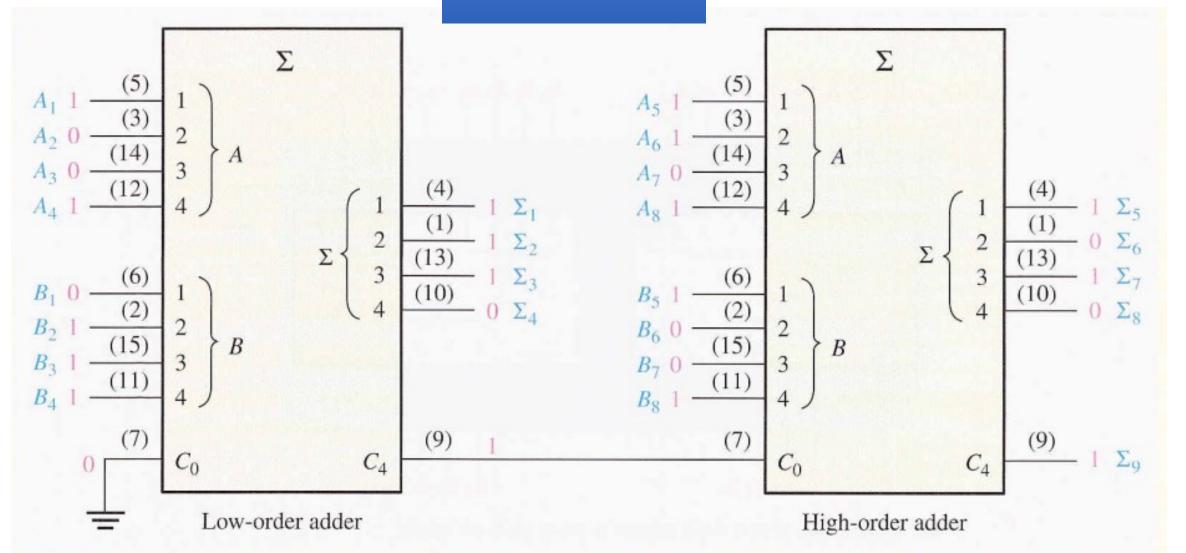

## XOR GATE

| INPUTS |   | ОИТРИТ |

|--------|---|--------|

| Α      | В | X      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

|        |   |        |

$$X = A \oplus B$$

### **XNOR GATE**

$$X = A \oplus B$$

| INPUTS |   | OUTPUT |  |

|--------|---|--------|--|

| A      | В | X      |  |

| 0      | 0 | 1      |  |

| 0      | 1 | 0      |  |

| 1      | 0 | 0      |  |

| 1      | 1 | 1      |  |

$$X = (\overline{A \oplus B}) = (A.B + \overline{A}.\overline{B})$$

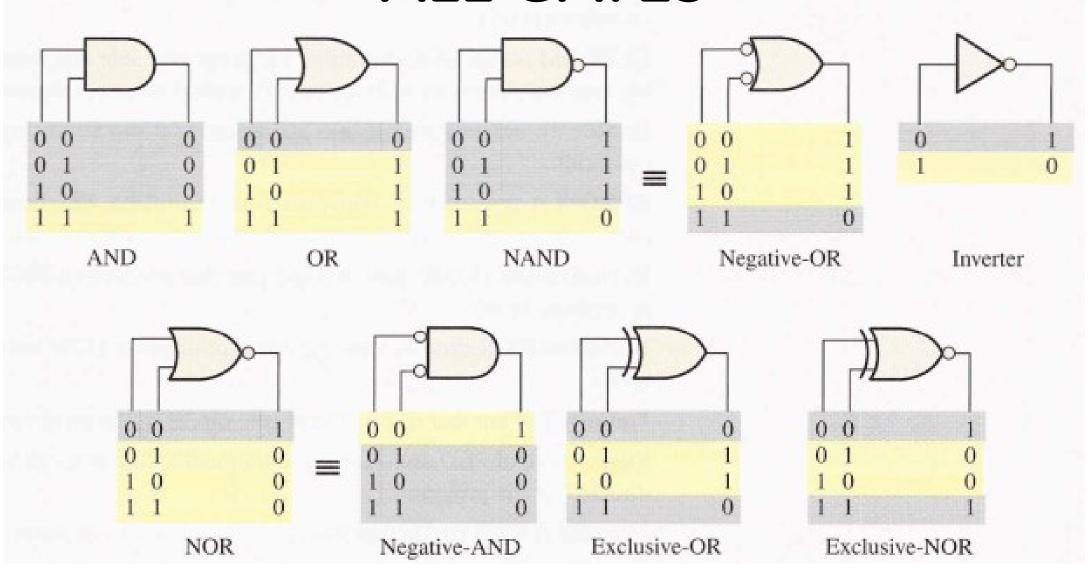

## **ALL GATES**

# Writing Boolean Expression

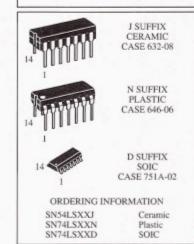

# DATASHEET

#### QUAD 2-INPUT NAND GATE

ESD > 3500 Volts

#### SN54/74LS00

#### QUAD 2-INPUT NAND GATE LOW POWER SCHOTTKY

#### SN54/74LS00

#### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|                 |                                            |        |     | Limits |      |      | Test Conditions                                                              |                        |

|-----------------|--------------------------------------------|--------|-----|--------|------|------|------------------------------------------------------------------------------|------------------------|

| Symbol          | Parameter                                  |        | Min | Тур    | Max  | Unit |                                                                              |                        |

| V <sub>IH</sub> | Input HIGH Voltage                         |        | 2.0 |        |      | V    | Guaranteed In                                                                | put HIGH Voltage for   |

| VIL             | Input LOW Voltage                          | 54     |     |        | 0.7  | v    | Guaranteed Input LOW Voltage for<br>All Inputs                               |                        |

| . 11.           | Imput 2011 Totalge                         | 74     |     |        | 0.8  |      |                                                                              |                        |

| $V_{IK}$        | Input Clamp Diode Voltage                  | 1100   |     | -0.65  | -1.5 | V    | $V_{CC} = MIN$ , $I_{IN} = -18 \text{ mA}$                                   |                        |

| V <sub>OH</sub> | Ouput HIGH Voltage                         | 54     | 2.5 | 3.5    |      | V    | $V_{CC} = MIN, I_{OH} = MAX, V_{IN} = V_{IH}$<br>or $V_{JL}$ per Truth Table |                        |

| * OH            | Ouput riion voitage                        | 74     | 2.7 | 3.5    |      | V    |                                                                              |                        |

| Vol.            | Ouput LOW Voltage                          | 54, 74 |     | 0.25   | 0.4  | V    | $I_{OL} = 4.0 \text{ mA}$ $V_{CC} = V_{CC} \text{ MIN}, V_{IN} =$            |                        |

| · OL            | Ouput DOW Younge                           | 74     |     | 0.35   | 0.5  | V    | $I_{OL} = 8.0 \text{ mA}$                                                    | or VIH per Truth Table |

| L               | Input HIGH Current                         |        |     |        | 20   | μΑ   | $V_{CC} = MAX$ , $V_{IN} = 2.7 V$                                            |                        |

| IIII            | Input mon cunent                           |        |     |        | 0.1  | mA   | $V_{CC} = MAX$ , $V_{IN} = 7.0 V$                                            |                        |

| I <sub>IL</sub> | Input LOW Current                          |        |     |        | -0.4 | mA   | V <sub>CC</sub> = MAX, I <sub>N</sub> = 0.4 V                                |                        |

| Ios             | Short Circuit Current (Note                | 1)     | -20 |        | -100 | mA   | V <sub>CC</sub> = MAX                                                        |                        |

| Icc             | Power Supply Current<br>Total, Output HIGH |        |     |        | 1.6  | mA   | V <sub>CC</sub> = MAX                                                        |                        |

|                 | Total, Output LOW                          |        |     |        | 4.4  |      |                                                                              |                        |

NOTE 1: Not more than one output should be shorted at a time, nor for more than 1 second.

#### AC CHARACTERISTICS (TA = 25°C)

|        |                                 |     | Limits |     |      |                         |

|--------|---------------------------------|-----|--------|-----|------|-------------------------|

| Symbol | Parameter                       | Min | Тур    | Max | Unit | Test Conditions         |

| tplH   | Turn-Off Delay, Input to Output |     | 9.0    | 15  | ns   | V <sub>CC</sub> = 5.0 V |

| tpHL   | Turn-On Delay, Input to Output  |     | 10     | 15  | ns   | $C_L = 15 \text{ pF}$   |

#### GUARANTEED OPERATING RANGES

| Symbol          | Parameter                              |          | Min         | Тур        | Max         | Unit |

|-----------------|----------------------------------------|----------|-------------|------------|-------------|------|

| V <sub>CC</sub> | Supply Voltage                         | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | V    |

| TA              | Operating Ambient<br>Temperature Range | 54<br>74 | -55<br>0    | 25<br>25   | 125<br>70   | °C   |

| $I_{OH}$        | Output Current — High                  | 54, 74   |             |            | -0.4        | mA   |

| I <sub>OL</sub> | Output Current — Low                   | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

**DIAGRAM**

Note: Home works are to be uploaded via the below google form <a href="https://forms.gle/tknEbbPN3mskkSmH6">https://forms.gle/tknEbbPN3mskkSmH6</a>

2

## University of Technology Laser & Optoelectronics Engineering Department

## DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 4: Boolean Algebra and Logic Simplification: 2023-Oct-29

# Lecture Outline

- 1. Boolean Algebra

- 2. DeMorgan's Theorems

- 3. SOP & POS & Truth Table

- 4. K-Map

- 5. HW

## Simple properties

$$A+B=B+A$$

$$A + (B + C) = (A + B) + C$$

$$AB = BA$$

$$A(BC) = (AB)C$$

### **Boolean Rules**

$$1.A + 0 = A$$

$$2.A + 1 = 1$$

$$3. A \cdot 0 = 0$$

**4.**

$$A \cdot 1 = A$$

$$5.A + A = A$$

$$6.A + \overline{A} = 1$$

$$7.A \cdot A = A$$

$$8.A \cdot \overline{A} = 0$$

$$9. \bar{A} = A$$

**10.**

$$A + AB = A$$

$$11.A + AB = A + B$$

12.

$$(A + B)(A + C) = A + BC$$

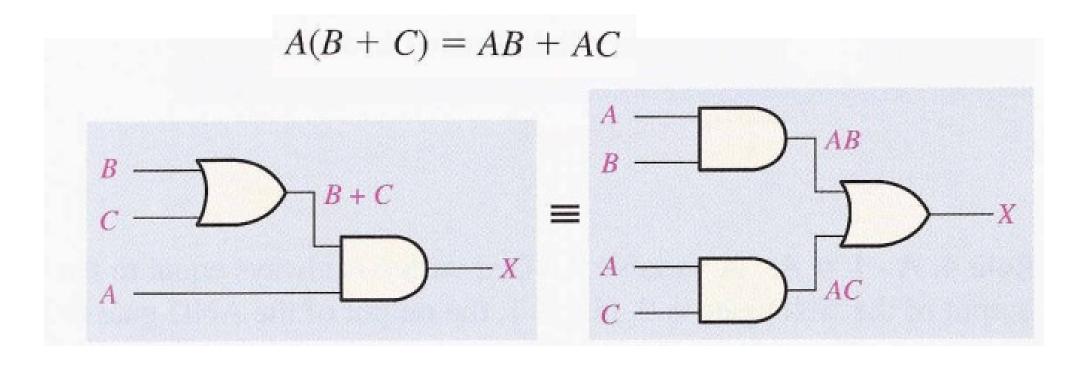

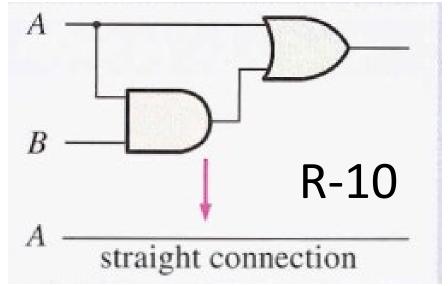

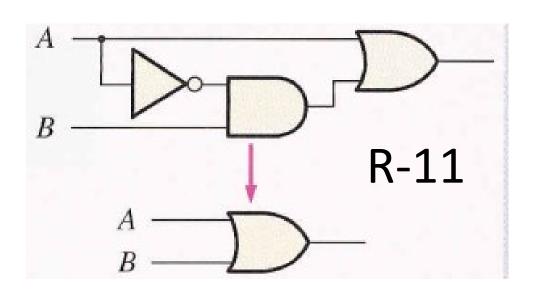

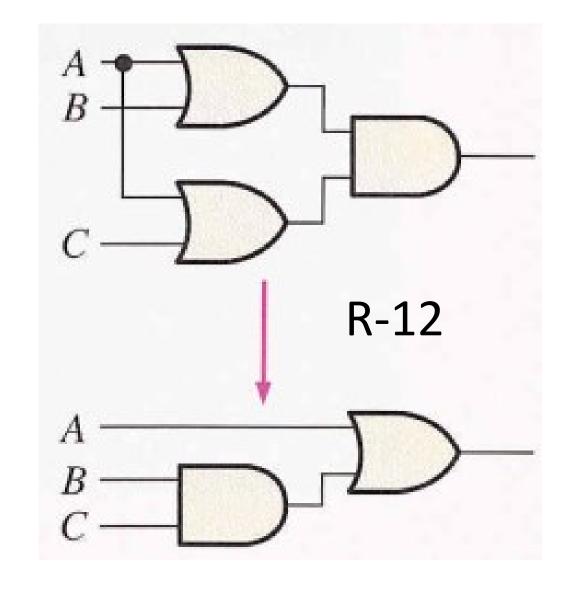

## Rules Simplify Logic

## De Morgan's Theorems

$$\overline{XY} = \overline{X} + \overline{Y}$$

$$\overline{X+Y}=\overline{X}\overline{Y}$$

Augustus De Morgan

# **Applications of De Morgan's Theorems**

Apply DeMorgan's theorems to the expressions XYZ and X + Y + Z.

**EX-1**

ANS

$$\overline{XYZ} = \overline{X} + \overline{Y} + \overline{Z}$$

$$\overline{X + Y + Z} = \overline{X}\overline{Y}\overline{Z}$$

### **EX-2**

Apply DeMorgan's theorems to each of the following expressions:

(a)

$$\overline{(A+B+C)D}$$

(b)

$$\overline{ABC + DEF}$$

(c)

$$\overline{AB} + \overline{CD} + EF$$

# ANS

(a) Let

$$A + B + C = X$$

and  $D = Y$ . The expression  $\overline{(A + B + C)D}$  is of the form  $\overline{XY} = \overline{X} + \overline{Y}$  and can be rewritten as

$$\overline{(A+B+C)D} = \overline{A+B+C} + \overline{D}$$

Next, apply DeMorgan's theorem to the term  $\overline{A + B + C}$ .

$$\overline{A + B + C} + \overline{D} = \overline{A}\overline{B}\overline{C} + \overline{D}$$

(b) Let ABC = X and DEF = Y. The expression  $\overline{ABC + DEF}$  is of the form  $\overline{X + Y} = \overline{X}\overline{Y}$  and can be rewritten as

$$\overline{ABC + DEF} = (\overline{ABC})(\overline{DEF})$$

Next, apply DeMorgan's theorem to each of the terms  $\overline{ABC}$  and  $\overline{DEF}$ .

$$(\overline{ABC})(\overline{DEF}) = (\overline{A} + \overline{B} + \overline{C})(\overline{D} + \overline{E} + \overline{F})$$

(c) Let  $A\overline{B} = X$ ,  $\overline{CD} = Y$ , and EF = Z. The expression  $\overline{AB} + \overline{CD} + EF$  is of the form  $\overline{X} + \overline{Y} + \overline{Z} = \overline{X}\overline{Y}\overline{Z}$  and can be rewritten as

$$\overline{AB} + \overline{CD} + EF = (\overline{AB})(\overline{CD})(\overline{EF})$$

Next, apply DeMorgan's theorem to each of the terms  $A\overline{B}$ ,  $\overline{C}D$ , and  $\overline{EF}$ .

$$(\overline{A}\overline{B})(\overline{\overline{C}D})(\overline{EF}) = (\overline{A} + B)(C + \overline{D})(\overline{E} + \overline{F})$$

#### Using Boolean algebra techniques, simplify this expression:

## **EX-3**

$$AB + A(B + C) + B(B + C)$$

Step 1: Apply the distributive law to the second and third terms in the expression, as follows:

AB + AB + AC + BB + BC

**Step 2:** Apply rule 7 (BB = B) to the fourth term.

$$AB + AB + AC + B + BC$$

**Step 3:** Apply rule 5(AB + AB = AB) to the first two terms.

$$AB + AC + B + BC$$

**Step 4:** Apply rule 10 (B + BC = B) to the last two terms.

$$AB + AC + B$$

**Step 5:** Apply rule 10 (AB + B = B) to the first and third terms.

$$B + AC$$

# Sum of Products (SOP)

$$AB + ABC$$

$ABC + CDE + \overline{B}C\overline{D}$

**EX-4**

Determine the binary values for which the following standard SOP expression is equal to 1:

$$ABCD + A\overline{B}\overline{C}D + \overline{A}\overline{B}\overline{C}\overline{D}$$

**ANS**

The term ABCD is equal to 1 when A = 1, B = 1, C = 1, and D = 1.

$$ABCD = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

The term  $A\overline{B}\overline{C}D$  is equal to 1 when A = 1, B = 0, C = 0, and D = 1.

$$A\overline{B}\overline{C}D = 1 \cdot \overline{0} \cdot \overline{0} \cdot 1 = 1 \cdot 1 \cdot 1 \cdot 1 = 1$$

The term  $\overline{A}\overline{B}\overline{C}\overline{D}$  is equal to 1 when A=0, B=0, C=0, and D=0.

$$\overline{A}\overline{B}\overline{C}\overline{D} = \overline{0}\cdot\overline{0}\cdot\overline{0}\cdot\overline{0} = 1\cdot1\cdot1\cdot1 = 1$$

The SOP expression equals 1 when any or all of the three product terms is 1.

## **Product of Sums (POS)**

$$(\overline{A} + B)(A + \overline{B} + C)$$

$$(\overline{A} + \overline{B} + \overline{C})(C + \overline{D} + E)(\overline{B} + C + D)$$

$$(A + B)(A + \overline{B} + C)(\overline{A} + C)$$

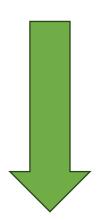

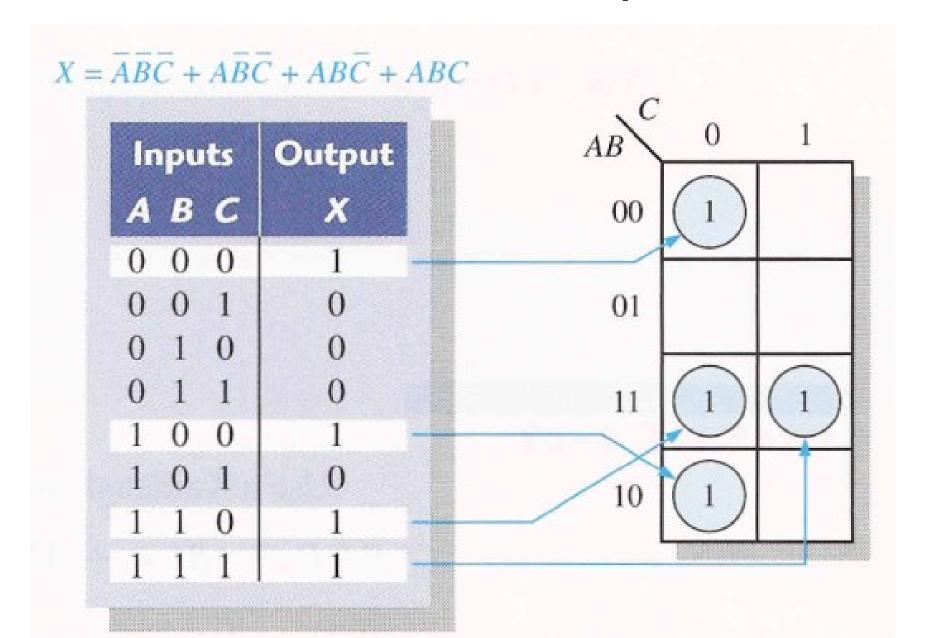

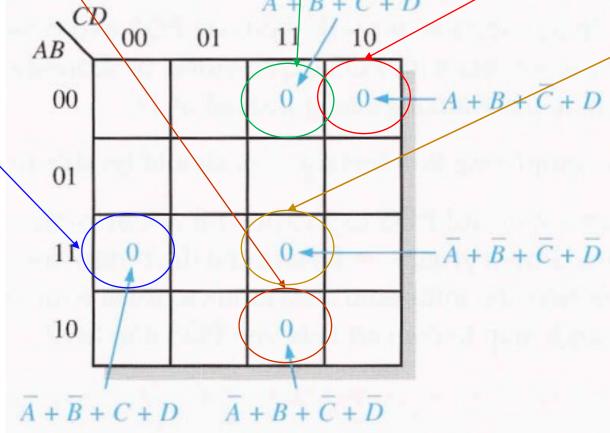

### **Truth Table Generation from SOP**

Develop a truth table for the standard SOP expression  $\overline{ABC} + \overline{ABC} + ABC$ .

| 11 | <b>IPUTS</b> | A A | OUTPUT |                             |

|----|--------------|-----|--------|-----------------------------|

| Α  | В            | C   | X      | PRODUCT TERM                |

| 0  | 0            | 0   | 0      |                             |

| 0  | 0            | 1   | 1      | $\overline{A}\overline{B}C$ |

| 0  | 1            | 0   | 0      |                             |

| 0  | 1            | 1   | 0      |                             |

| 1  | 0            | 0   | 1      | $A\overline{B}\overline{C}$ |

| 1  | 0            | 1   | 0      |                             |

| 1  | 1            | 0   | 0      |                             |

| 1  | 1            | 1   | 1      | ABC                         |

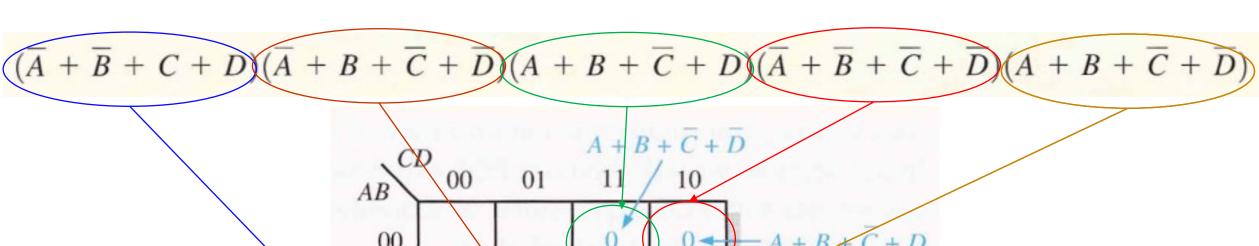

### **Truth Table Generation from POS**

Determine the truth table for the following standard POS expression:

$$(A + B + C)(A + \overline{B} + C)(A + \overline{B} + \overline{C})(\overline{A} + B + \overline{C})(\overline{A} + \overline{B} + C)$$

|   | INPUTS | 5 | OUTPUT |                                     |

|---|--------|---|--------|-------------------------------------|

| Α | В      | С | X      | SUM TERM                            |

| 0 | 0      | 0 | 0      | (A + B + C)                         |

| 0 | 0      | 1 | 1      | des years                           |

| 0 | 1      | 0 | 0      | $(A + \overline{B} + C)$            |

| 0 | 1      | 1 | 0      | $(A + \overline{B} + \overline{C})$ |

| 1 | 0      | 0 | 1      |                                     |

| 1 | 0      | 1 | 0      | $(\overline{A} + B + \overline{C})$ |

| 1 | 1      | 0 | 0      | $(\overline{A} + \overline{B} + C)$ |

| 1 | 1      | 1 | 1      |                                     |

### **SOP & POS Generation from Truth Table**

|   | INPUTS |   | OUTPUT |

|---|--------|---|--------|

| A | В      | С | X      |

| 0 | 0      | 0 | 0      |

| 0 | 0      | 1 | 0      |

| 0 | 1      | 0 | 0      |

| 0 | 1      | 1 | 1      |

| 1 | 0      | 0 | 1      |

| 1 | 0      | 1 | 0      |

| 1 | 1      | 0 | 1      |

| 1 | 1      | 1 | 1      |

$$000 \longrightarrow A + B + C$$

$$001 \longrightarrow A + B + \overline{C}$$

$$010 \longrightarrow A + \overline{B} + C$$

$$101 \longrightarrow \overline{A} + B + \overline{C}$$

POS

$$X = (A + B + C)(A + B + \overline{C})(A + \overline{B} + C)(\overline{A} + B + \overline{C})$$

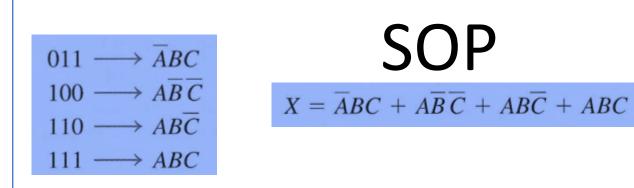

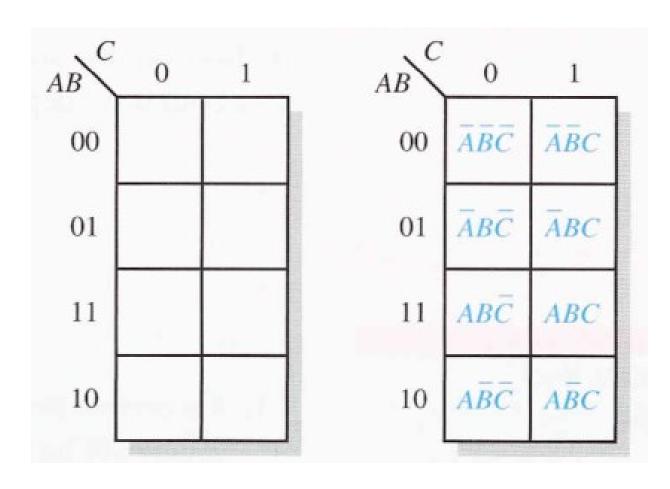

#### Karnaugh Map (K-Map)

**Maurice Karnaugh**

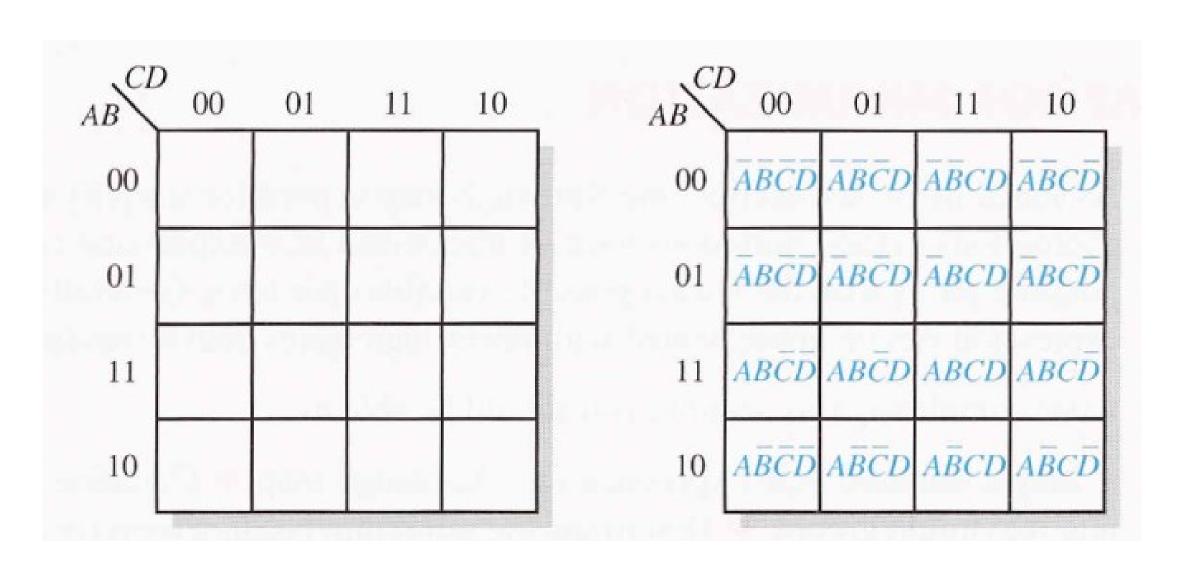

#### 4-Input K-Map

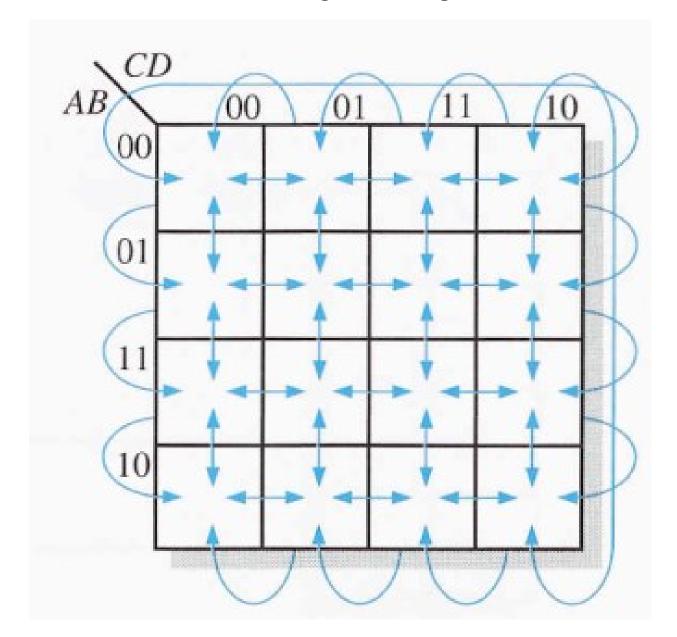

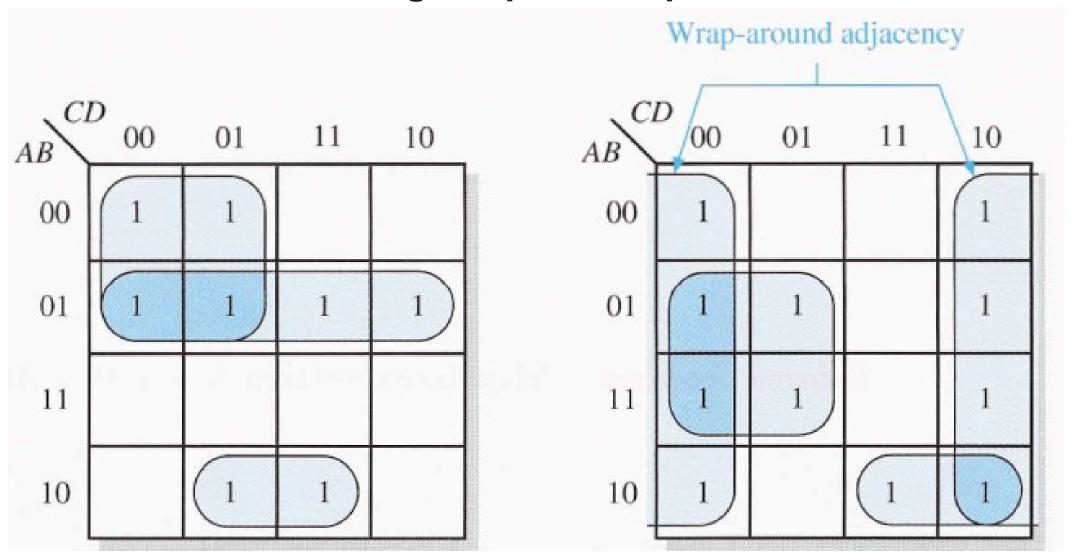

### **Cell Adjacency**

#### **Solving 3-Input K-Map**

Wrap-around adjacency

#### **Solving 4-Input K-Map**

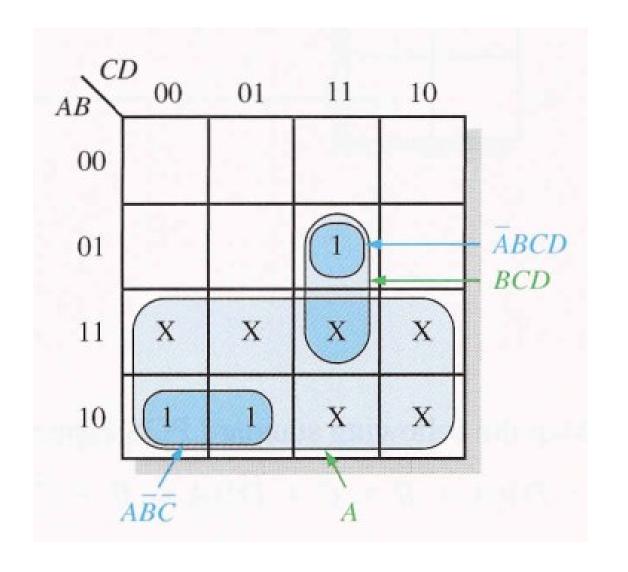

#### K-Map Rules for SOP

Determine the minimum product term for each group.

- **a.** For a 3-variable map:

- (1) A 1-cell group yields a 3-variable product term

- (2) A 2-cell group yields a 2-variable product term

- (3) A 4-cell group yields a 1-variable term

- (4) An 8-cell group yields a value of 1 for the expression

- **b.** For a 4-variable map:

- (1) A 1-cell group yields a 4-variable product term

- (2) A 2-cell group yields a 3-variable product term

- (3) A 4-cell group yields a 2-variable product term

- (4) An 8-cell group yields a 1-variable term

- (5) A 16-cell group yields a value of 1 for the expression

# CD

#### **SOP from K-Map**

$$B + \overline{AC} + \overline{ACD}$$

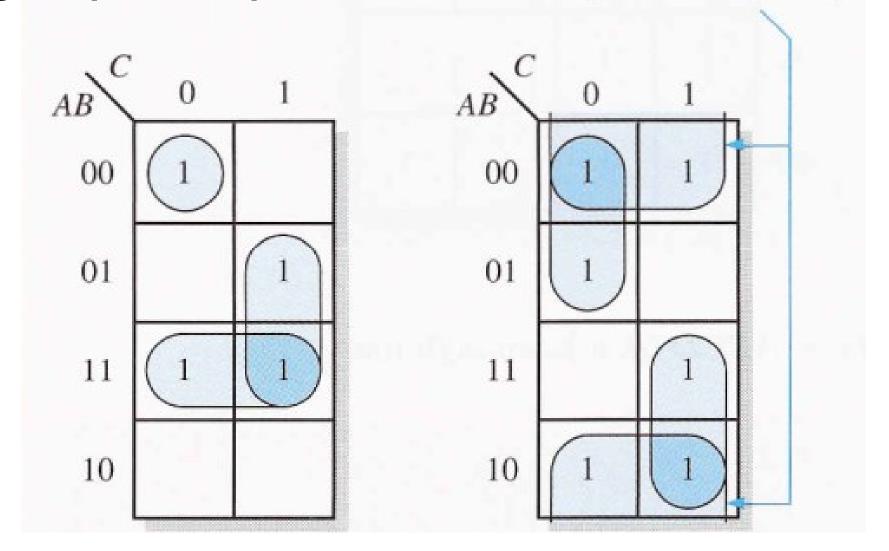

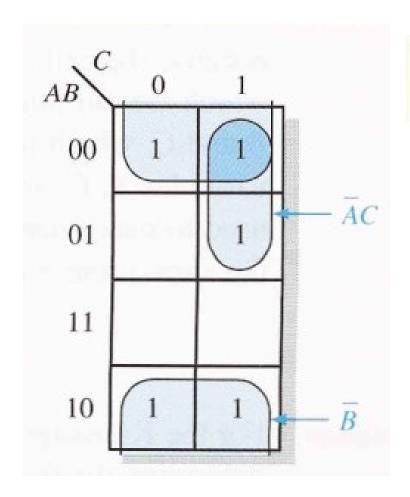

#### **SOP Minimization Using 3-Input K-Map**

Use a Karnaugh map to minimize the following standard SOP expression:

$$A\overline{B}C + \overline{A}BC + \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + A\overline{B}\overline{C}$$

$$\overline{B} + \overline{A}C$$

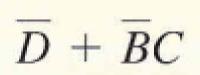

#### **SOP Minimization Using 4-Input K-Map**

Use a Karnaugh map to minimize the following SOP expression:

$$\overline{B}\overline{C}\overline{D} + \overline{A}B\overline{C}\overline{D} + AB\overline{C}\overline{D} + \overline{A}\overline{B}CD + A\overline{B}CD + \overline{A}\overline{B}C\overline{D} + \overline{A}BC\overline{D} + ABC\overline{D} + ABC\overline{D} + ABC\overline{D}$$

#### **Truth Table & K-Map**

#### "Don't Care" Condition

|            | Output | Inputs  |

|------------|--------|---------|

|            | Y      | ABCD    |

|            | 0      | 0000    |

|            | 0      | 0 0 0 1 |

|            | 0      | 0010    |

|            | 0      | 0 0 1 1 |

|            | 0      | 0100    |

|            | 0      | 0 1 0 1 |

|            | 0      | 0 1 1 0 |

|            | 1      | 0 1 1 1 |

|            | 1      | 1000    |

|            | 1      | 1001    |

|            | X      | 1010    |

|            | X      | 1011    |

| Don't care | X      | 1 1 0 0 |

| Don't care | X      | 1 1 0 1 |

|            | X      | 1110    |

|            | X      | 1 1 1 1 |

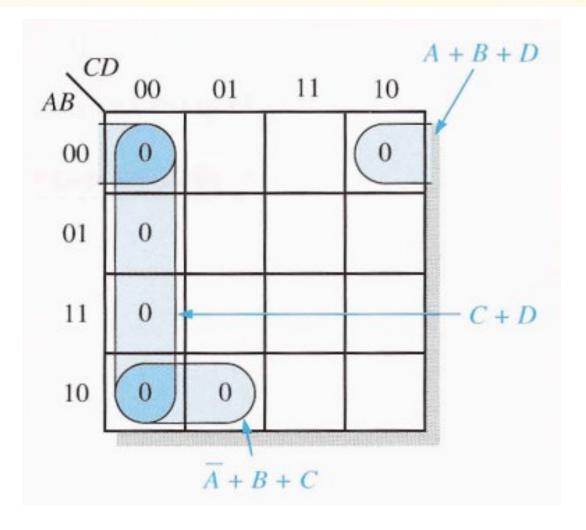

#### **POS Mapping Using K-Map**

#### **POS Simplification Using K-Map**

$$(B+C+D)(A+B+\overline{C}+D)(\overline{A}+B+C+\overline{D})(A+\overline{B}+C+D)(\overline{A}+\overline{B}+C+D)$$

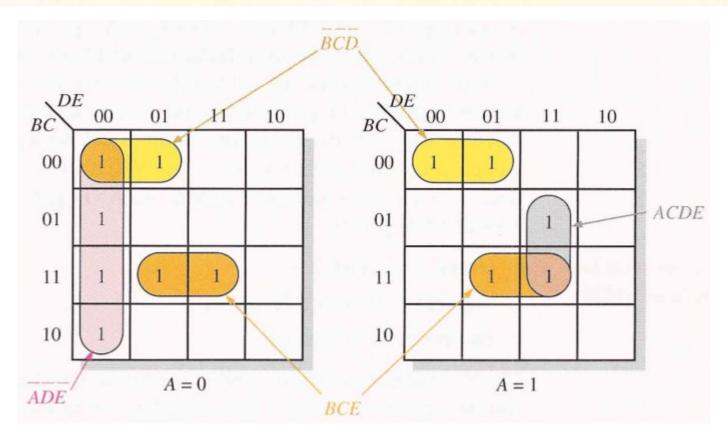

#### 5-Input K-Map

Use a Karnaugh map to minimize the following standard SOP 5-variable expression:

$$X = \overline{A}\overline{B}\overline{C}\overline{D}\overline{E} + \overline{A}\overline{B}C\overline{D}\overline{E} + \overline{A}BC\overline{D}\overline{E} + \overline{A}BC\overline{D}\overline{E} + \overline{A}B\overline{C}\overline{D}E + \overline{A}B\overline{C}\overline{D}E + \overline{A}BC\overline{D}E$$

$$+ \overline{A}BCDE + A\overline{B}\overline{C}\overline{D}\overline{E} + A\overline{B}\overline{C}\overline{D}E + ABC\overline{D}E + ABCDE + ABCDE$$

### Home Work (Due date 08-10-2023)

#### 1- Apply DeMorgan's theorems to the following

$$\overline{(\overline{A+B})(\overline{C+D})(\overline{E+F})(\overline{G+H})}$$

Determine the binary values of the variables for which the following standard POS expression is equal to 0:

$$(A + B + C + D)(A + \overline{B} + \overline{C} + D)(\overline{A} + \overline{B} + \overline{C} + \overline{D})$$

Note: Home works are to be uploaded via the below google form <a href="https://forms.gle/XuMw9LzCuZnnxGiZ7">https://forms.gle/XuMw9LzCuZnnxGiZ7</a>

#### 3- Which Circuits are Equivalent?

Develop a truth table for each of the SOP expressions:

(a)

$$\overline{AB} + AB\overline{C} + \overline{A}\overline{C} + A\overline{B}C$$

(b)  $\overline{X} + Y\overline{Z} + WZ + X\overline{Y}Z$

Use a Karnaugh map to reduce each expression to a minimum SOP form:

5 (b)

$$\overline{A}\overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}D + ABCD + ABC\overline{D}$$

(c)

$$\overline{AB}(\overline{CD} + \overline{CD}) + AB(\overline{CD} + \overline{CD}) + A\overline{B}\overline{CD}$$

Minimize the following SOP expression using a Karnaugh map:

$$X = \overline{A}B\overline{C}D\overline{E} + \overline{A}B\overline{C}DE + AB\overline{C}DE + AB\overline{C}DE + \overline{A}BCD\overline{E} + \overline{A}BCD\overline{E}$$

#### University of Technology Laser & Optoelectronics Engineering Department

#### DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 5: Combinational Logic Analysis: 2023-Nov-05

### Lecture Outline

- 1. Circuit Design

- 2. Circuit Minimization

- 3. Circuit from Expression

- 4. Circuit from Truth Table

- 5. Universal NAND Universal NOR

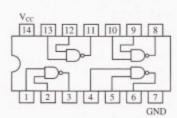

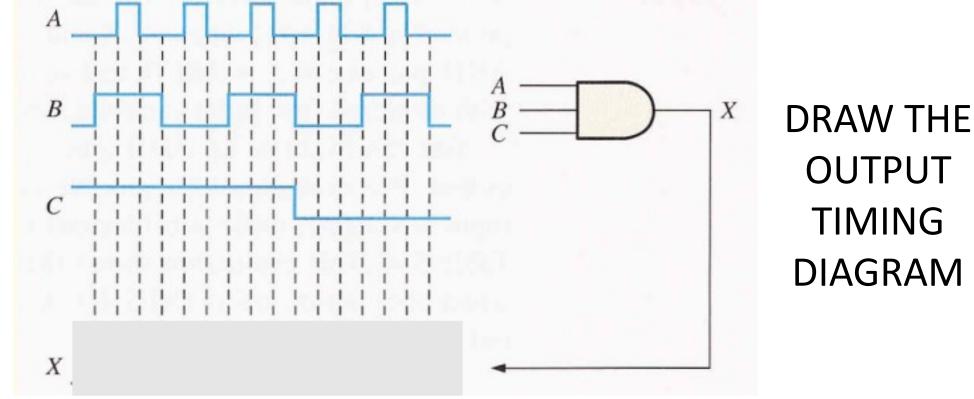

- 6. Multiple Input Timing Diagram

- **7.** HW

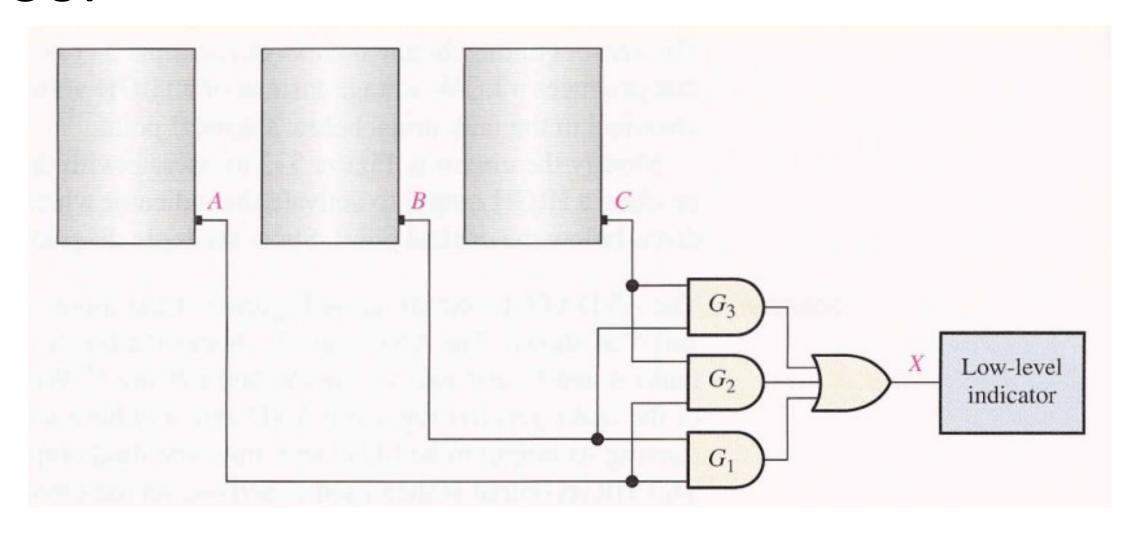

## Design Problems

#### **Ex-1**

In a certain chemical-processing plant, a liquid chemical is used in a manufacturing process. The chemical is stored in three different tanks. A level sensor in each tank produces a HIGH voltage when the level of chemical in the tank drops below a specified point.

Design a circuit that monitors the chemical level in each tank and indicates when the level in any two of the tanks drops below the specified point.

## Sol

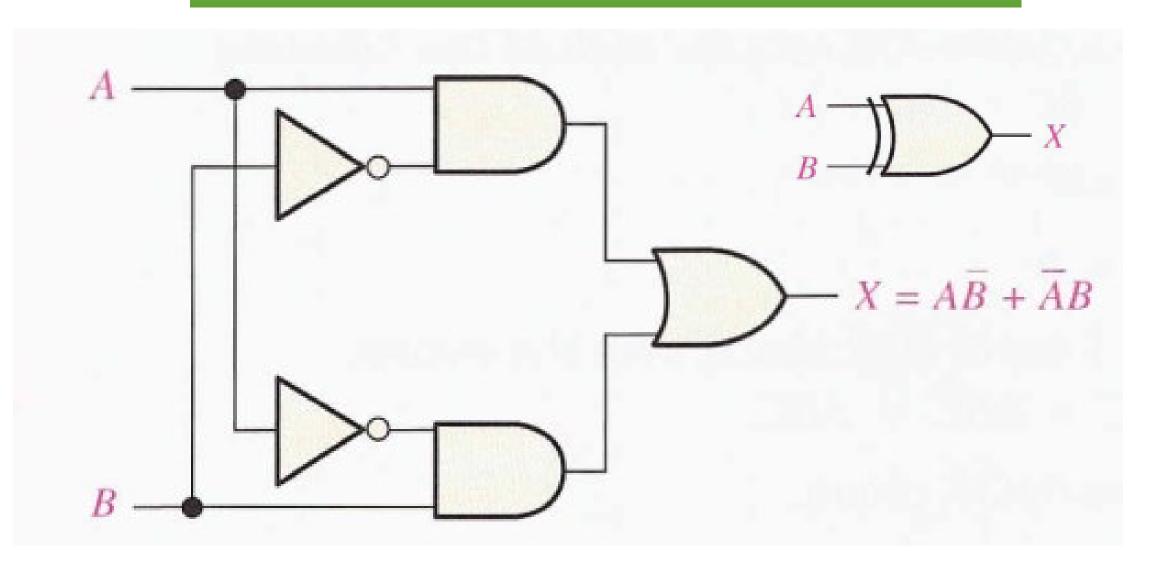

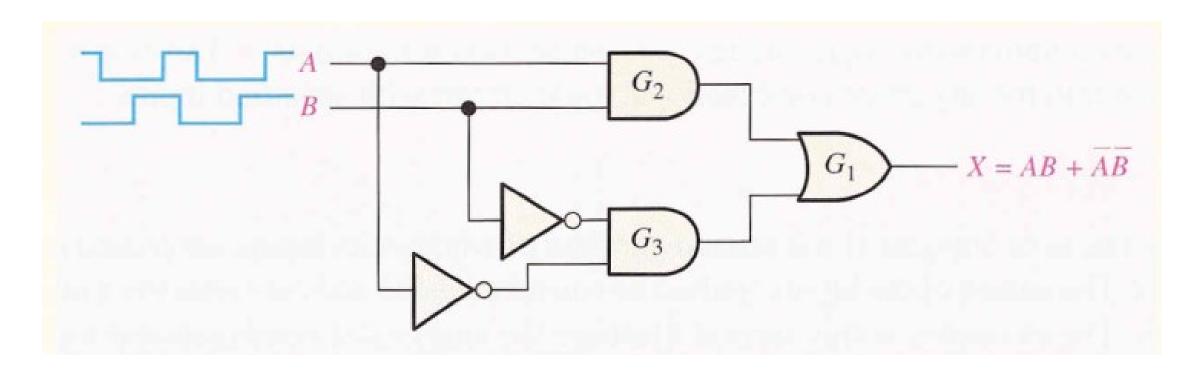

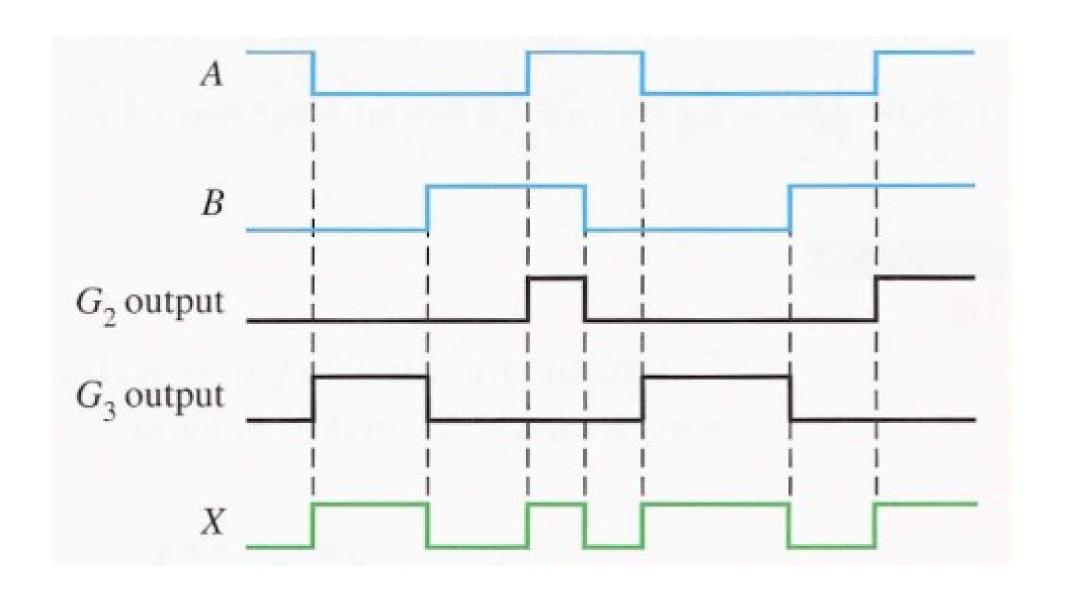

## XOR Gate Equivalent Circuit

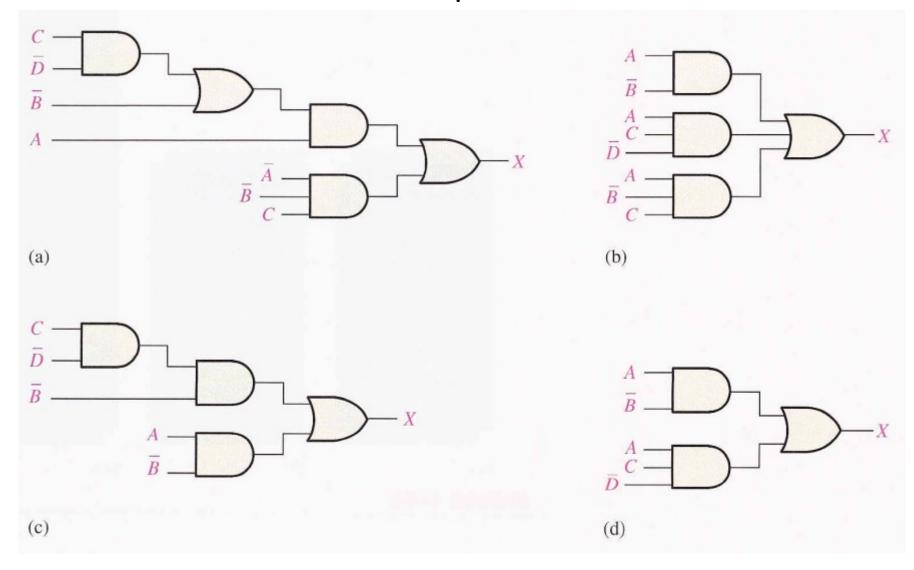

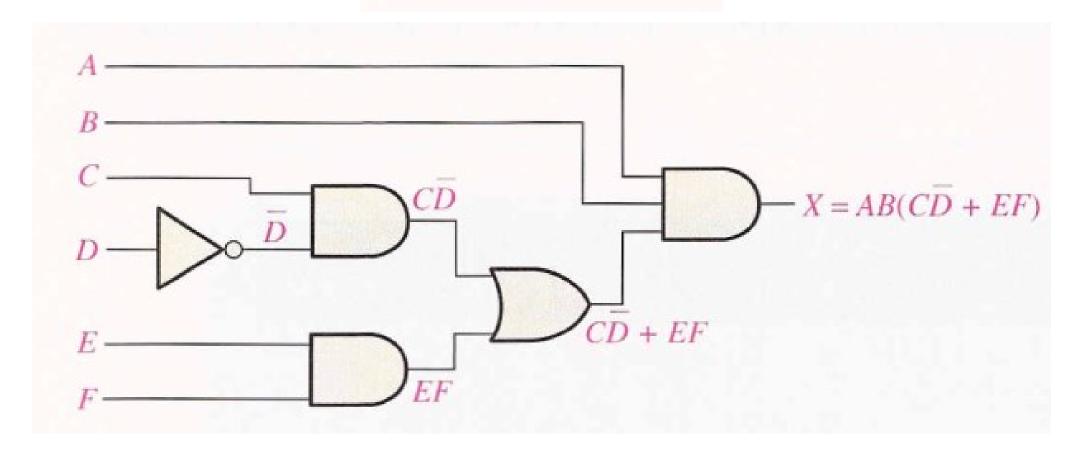

## Circuit from Expression

$$AB(C\overline{D} + EF)$$

Ex-3

### $ABC\overline{D} + ABEF$

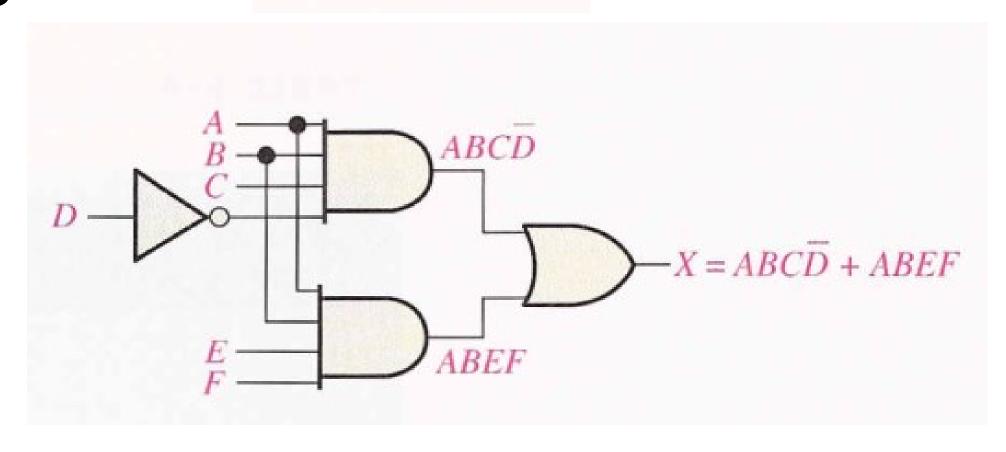

# Circuit from Expression

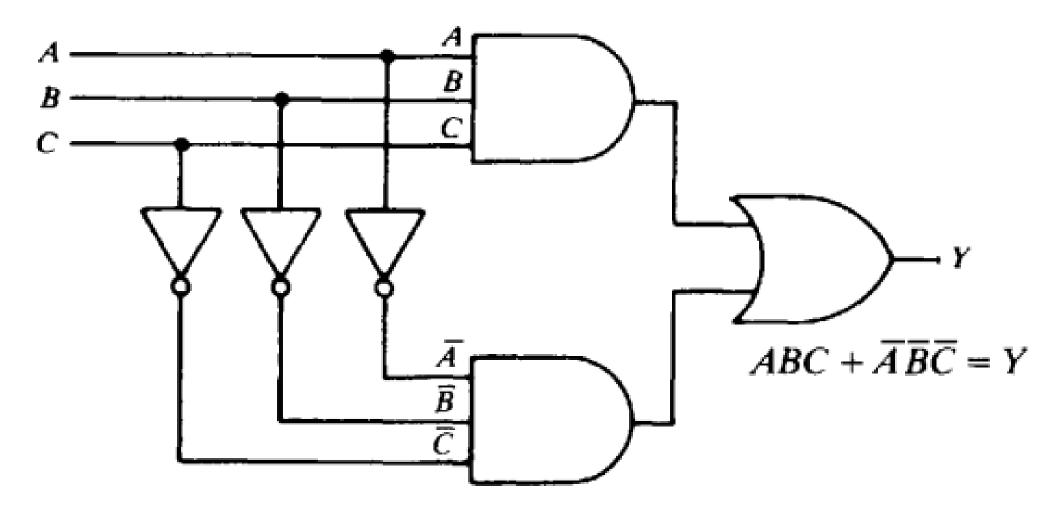

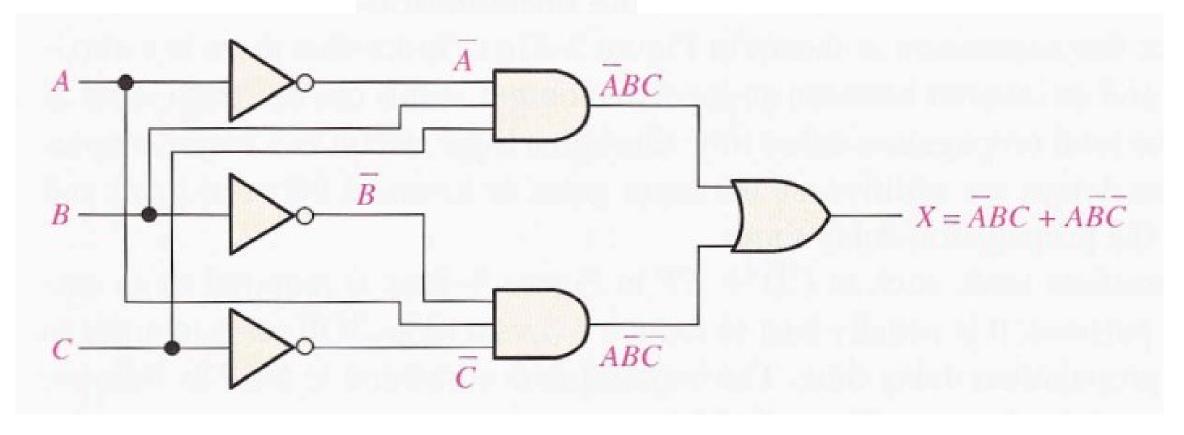

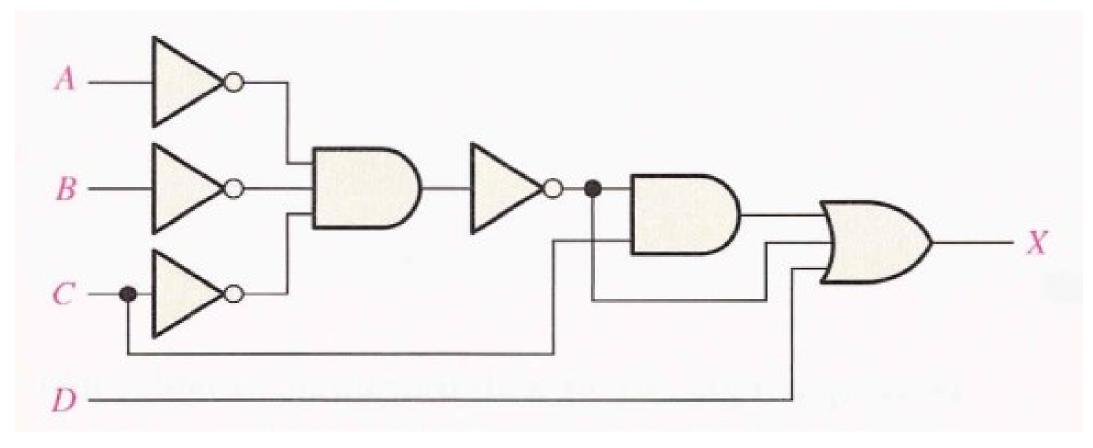

$$X = \overline{ABC} + A\overline{BC}$$

## Circuit from Truth Table

| DDGDUGT TEDU     | ОИТРИТ | INPUTS |   |   |  |

|------------------|--------|--------|---|---|--|

| PRODUCT TERM     | X      | С      | В | A |  |

|                  | 0      | 0      | 0 | 0 |  |

|                  | 0      | 1      | 0 | 0 |  |

|                  | 0      | 0      | 1 | 0 |  |

| $\overline{A}BC$ | 1      | 1      | 1 | 0 |  |

|                  | 0      | 0      | 0 | 1 |  |

| $A\overline{B}C$ | 1      | 1      | 0 | 1 |  |

| $AB\overline{C}$ | 1      | 0      | 1 | 1 |  |

|                  | 0      | 1      | 1 | 1 |  |

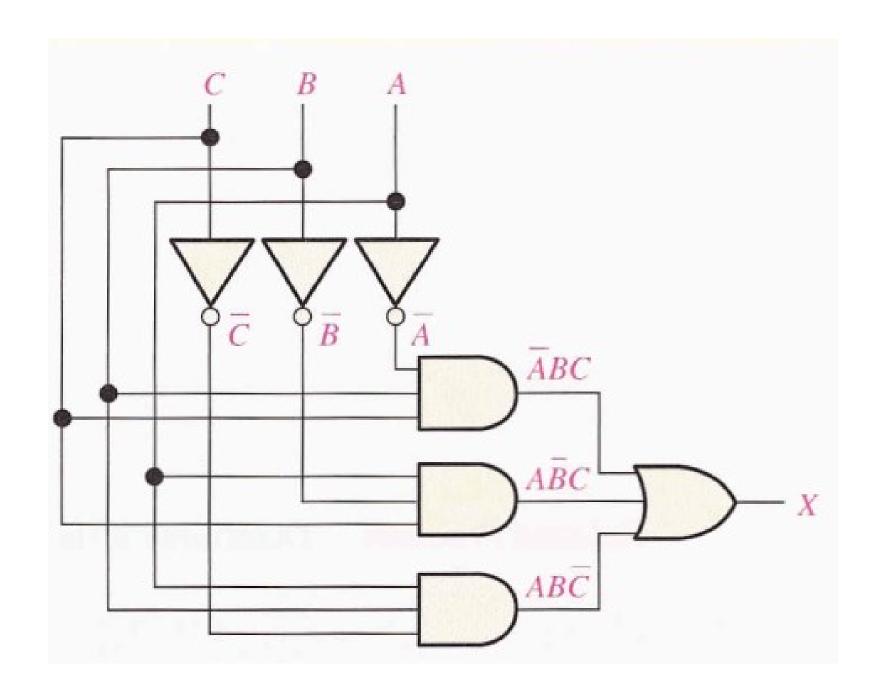

$$X = \overline{ABC} + A\overline{BC} + AB\overline{C}$$

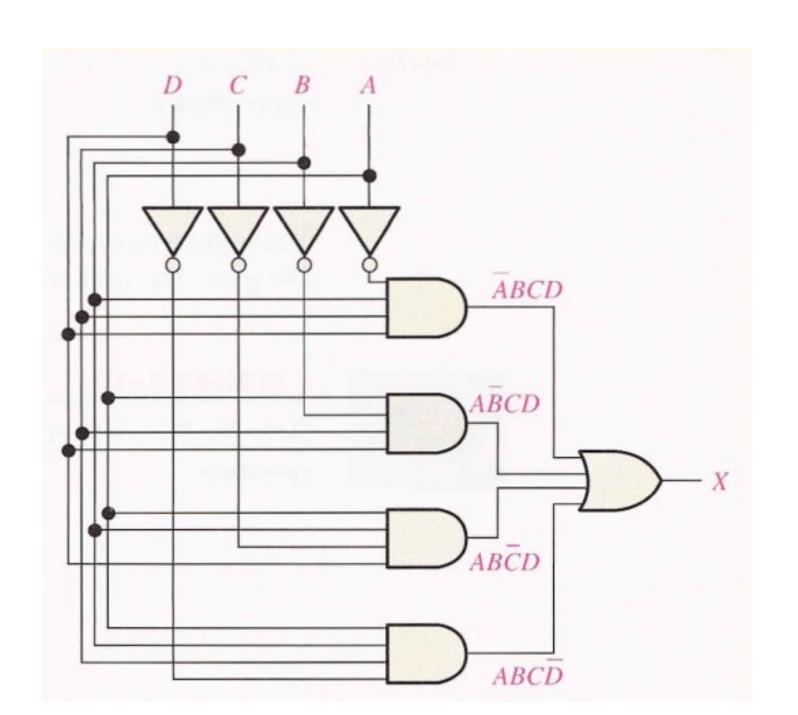

#### Ex-6

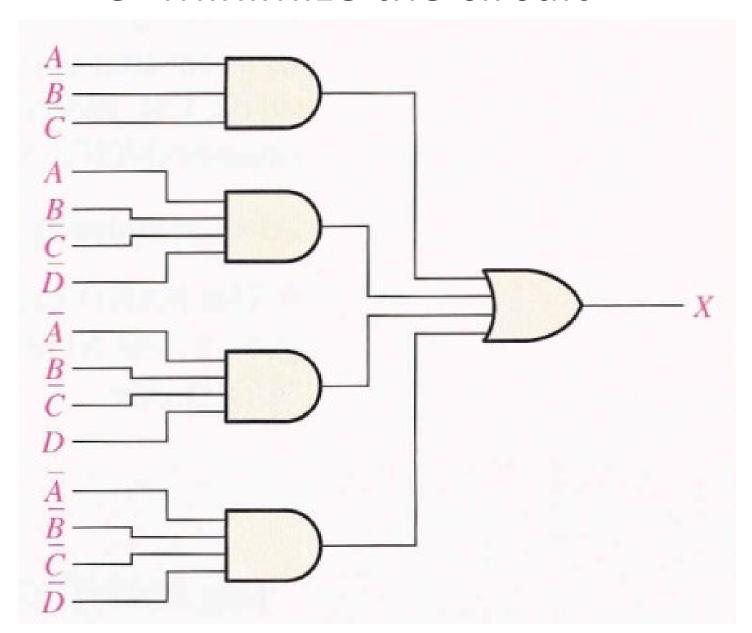

Develop a logic circuit with four input variables that will only produce a 1 output when exactly three input variables are 1s.

| Α | В | С | D | PRODUCT TERM      |

|---|---|---|---|-------------------|

| 0 | 1 | 1 | 1 | $\overline{A}BCD$ |

| 1 | 0 | 1 | 1 | $A\overline{B}CD$ |

| 1 | 1 | 0 | 1 | $AB\overline{C}D$ |

| 1 | 1 | 1 | 0 | $ABC\overline{D}$ |

$$X = \overline{A}BCD + A\overline{B}CD + AB\overline{C}D + ABC\overline{D}$$

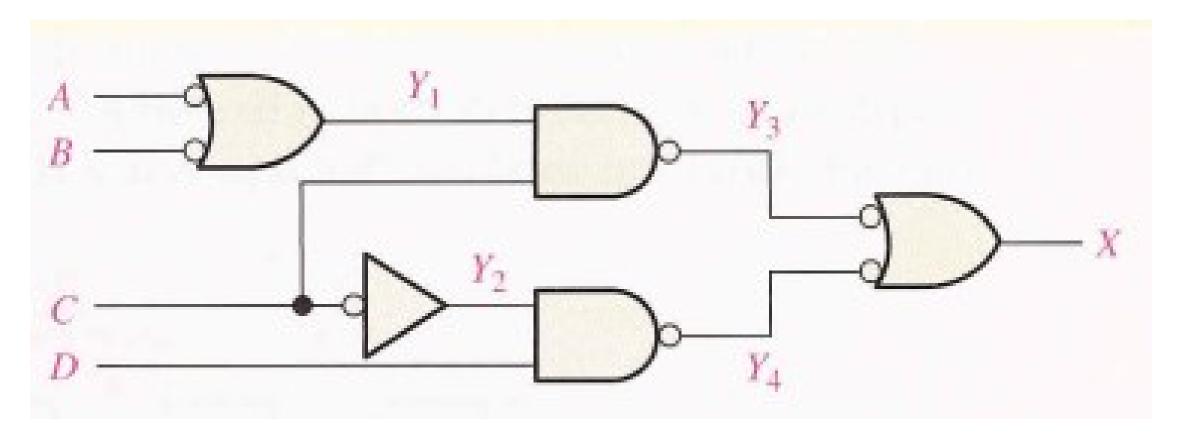

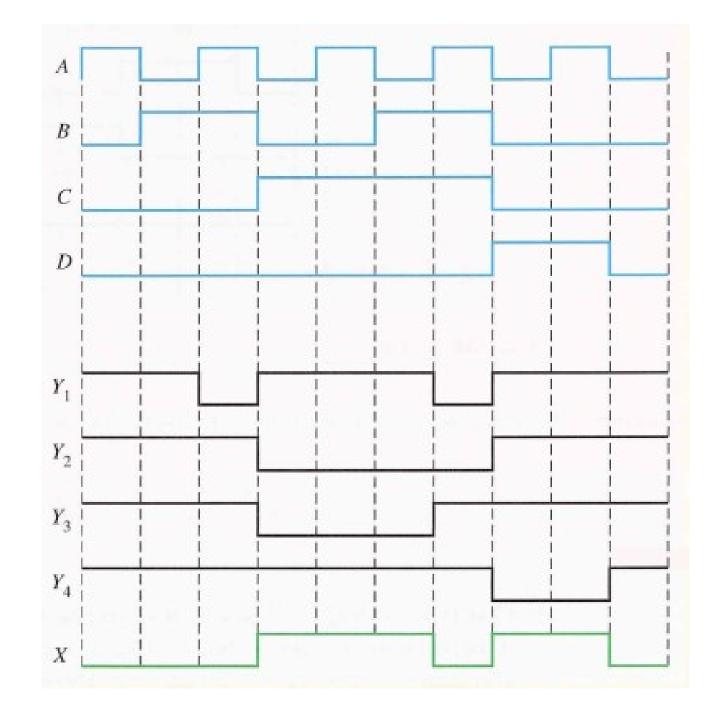

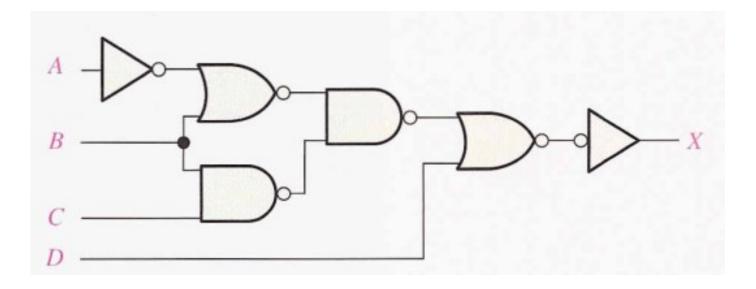

### Circuit Minimization

The expression for the output of the circuit is

$$X = (\overline{\overline{A}}\overline{\overline{B}}\overline{\overline{C}})C + \overline{\overline{A}}\overline{\overline{B}}\overline{\overline{C}} + D$$

Applying DeMorgan's theorem and Boolean algebra,

$$X = (\overline{A} + \overline{B} + \overline{C})C + \overline{A} + \overline{B} + \overline{C} + D$$

$$= AC + BC + CC + A + B + C + D$$

$$= AC + BC + C + A + B + C + D$$

$$= AC + BC + C + A + B + C + D$$

$$= C(A + B + 1) + A + B + D$$

$$X = A + B + C + D$$

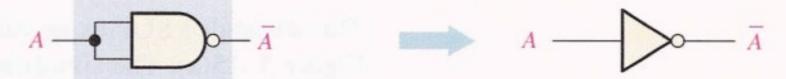

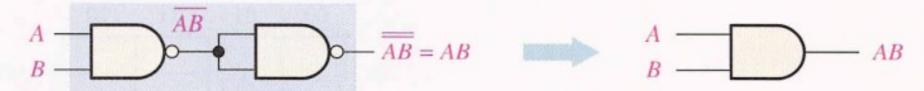

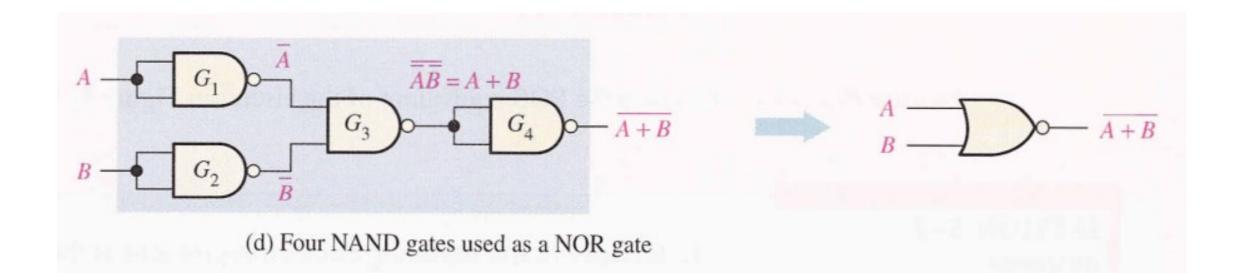

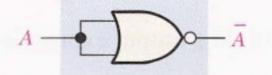

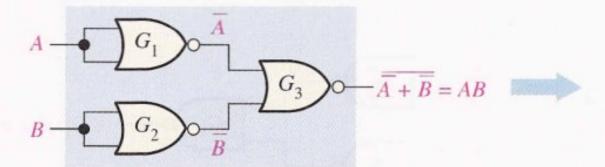

### **Universal NAND**

(a) One NAND gate used as an inverter

(b) Two NAND gates used as an AND gate

(c) Three NAND gates used as an OR gate

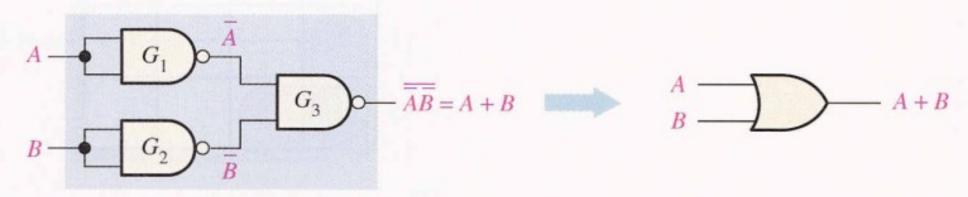

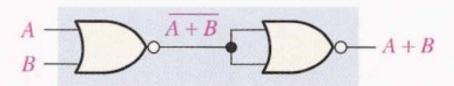

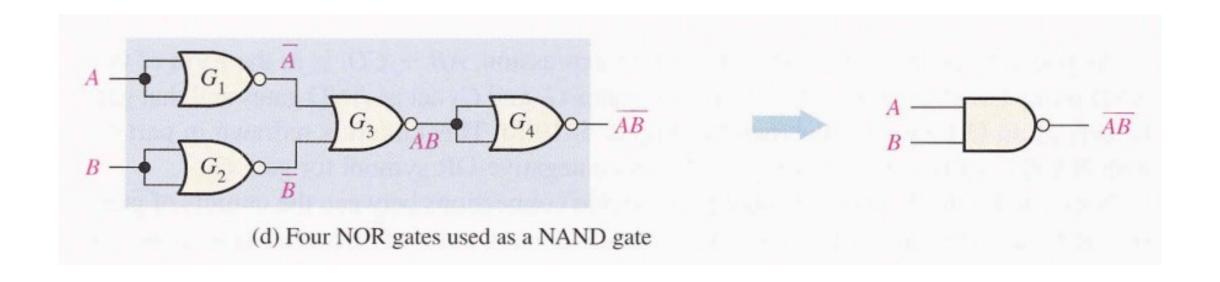

### **Universal NOR**

(a) One NOR gate used as an inverter

$$A + B$$

(b) Two NOR gates used as an OR gate

$$A \longrightarrow AB$$

(c) Three NOR gates used as an AND gate

#### Timing Diagram for Combinational Circuit

### Home Work (Due date 18-11-2023)

1 Implement the expression  $X = (\overline{A} + \overline{B} + \overline{C})DE$  by using NAND logic.

2- Develop a truth

Table for the

circuit

Note: Home works are to be uploaded via the below google form <a href="https://forms.gle/9rCnjuzHguKhf5H89">https://forms.gle/9rCnjuzHguKhf5H89</a>

#### 3- Minimize the circuit

#### University of Technology Laser & Optoelectronics Engineering Department

#### DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 6: Functions of Combinational Logic 1: 2023-Nov-15

## Lecture Outline

- 1. Half Adders

- 2. Full Adders

- 3. Parallel Binary Adders

- 4. Cascading

- 5. Comparators

- 6. IC Sets

- **7.** HW

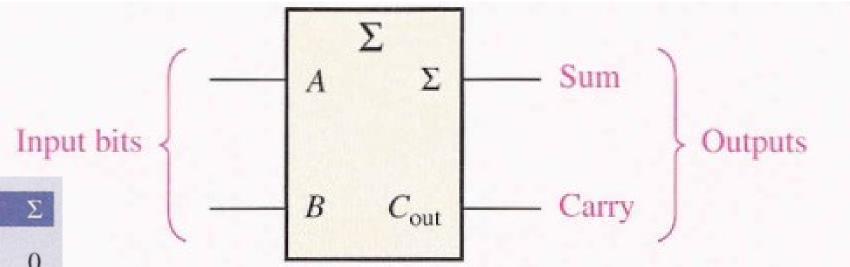

## Half Adder

| Α | В | $C_{ m out}$ | Σ |

|---|---|--------------|---|

| 0 | 0 | 0            | 0 |

| 0 | 1 | 0            | 1 |

| 1 | 0 | 0            | 1 |

| 1 | 1 | 1            | 0 |

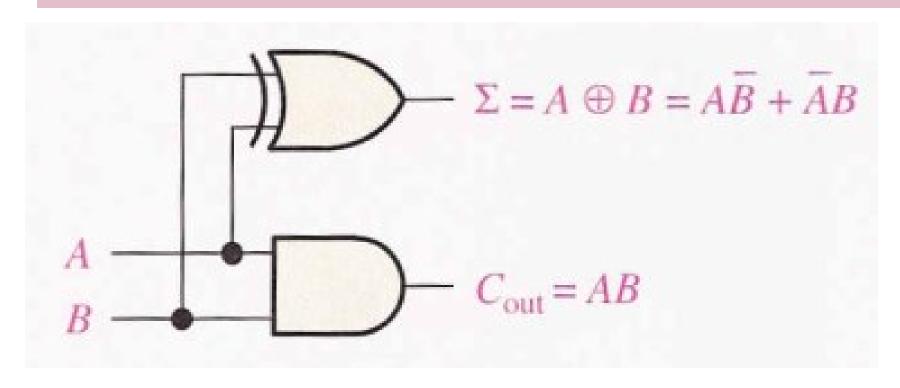

$$\Sigma = A \oplus B$$

$$C_{\rm out} = AB$$

$$\Sigma = sum$$

$C_{\rm out} = {\rm output\ carry}$

A and B = input variables (operands)

## Half Adder Equivalent Circuit

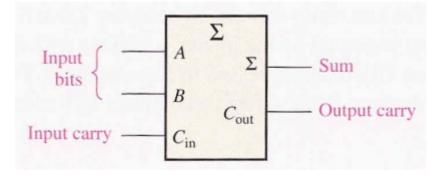

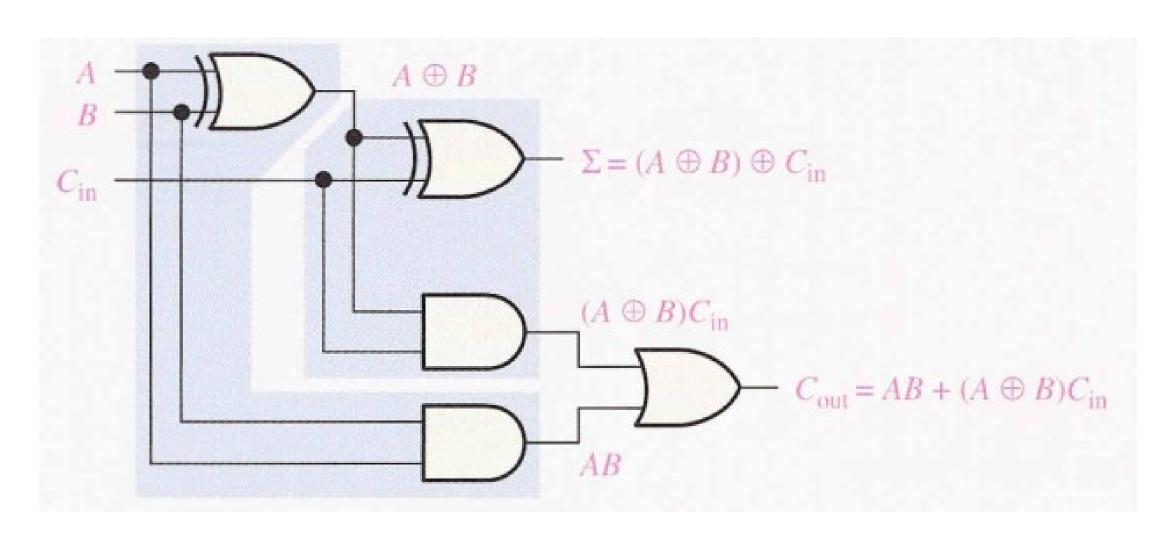

### Full Adder

| Α | В | Cin | Cout | Σ |

|---|---|-----|------|---|

| 0 | 0 | 0   | 0    | 0 |

| 0 | 0 | 1   | 0    | 1 |

| 0 | 1 | 0   | 0    | 1 |

| 0 | 1 | 1   | 1    | 0 |

| 1 | 0 | 0   | 0    | 1 |

| 1 | 0 | 1   | 1    | 0 |

| 1 | 1 | 0   | 1    | 0 |

| 1 | 1 | 1   | 1    | 1 |

$C_{\rm in}$  = input carry, sometimes designated as CI

$C_{\text{out}} = \text{output carry, sometimes designated as } CO$

$\Sigma = \text{sum}$

A and B = input variables (operands)

$$C_{\text{out}} = AB + (A \oplus B)C_{\text{in}}$$

$$\Sigma = (A \oplus B) \oplus C_{\rm in}$$

# Full Adder Equivalent Circuit

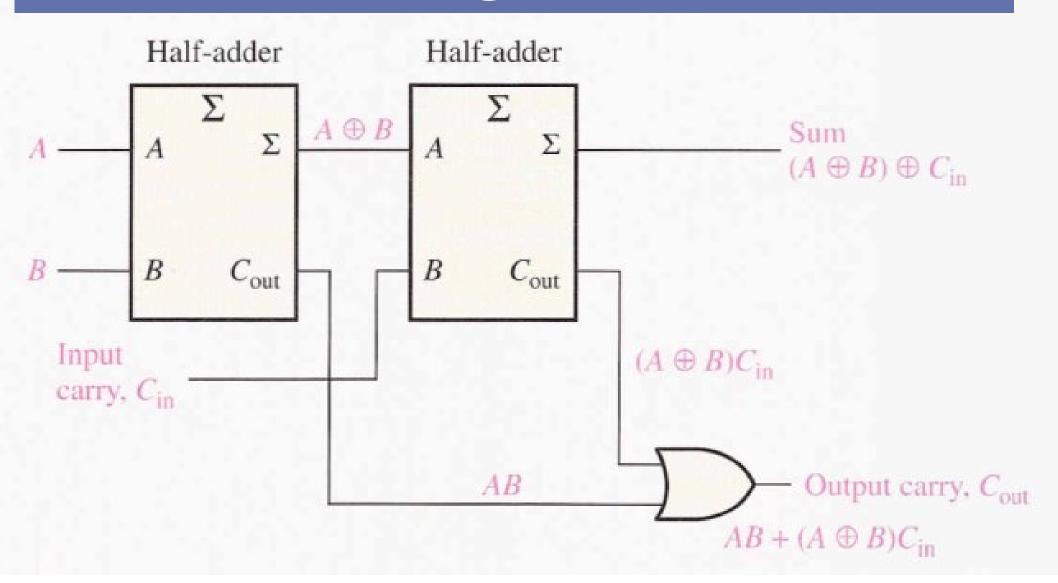

## Full Adder Using Two Half Adders

### Ex-1

### 101+011=1000

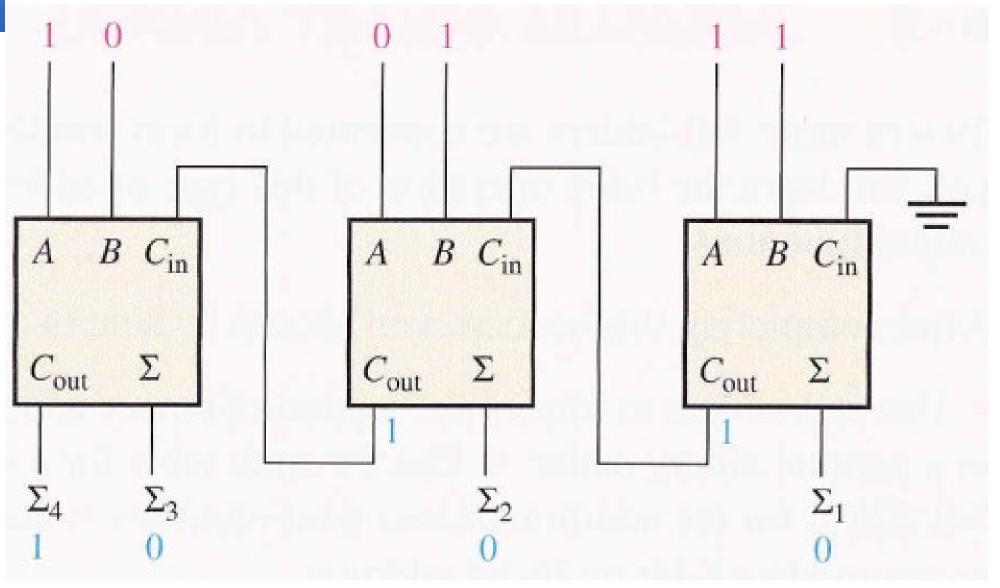

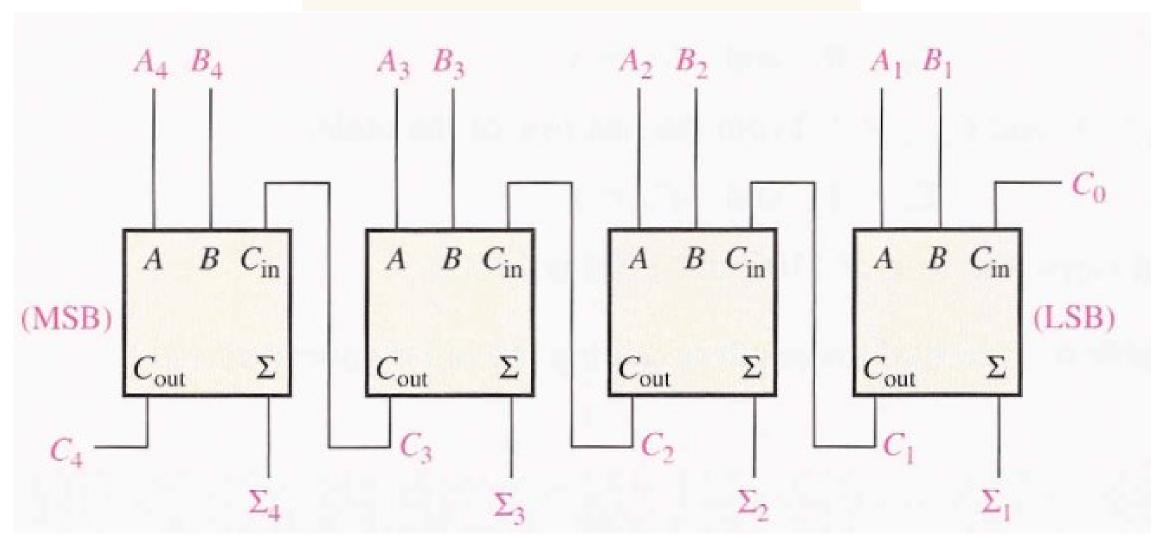

# 4-bit Binary Adder

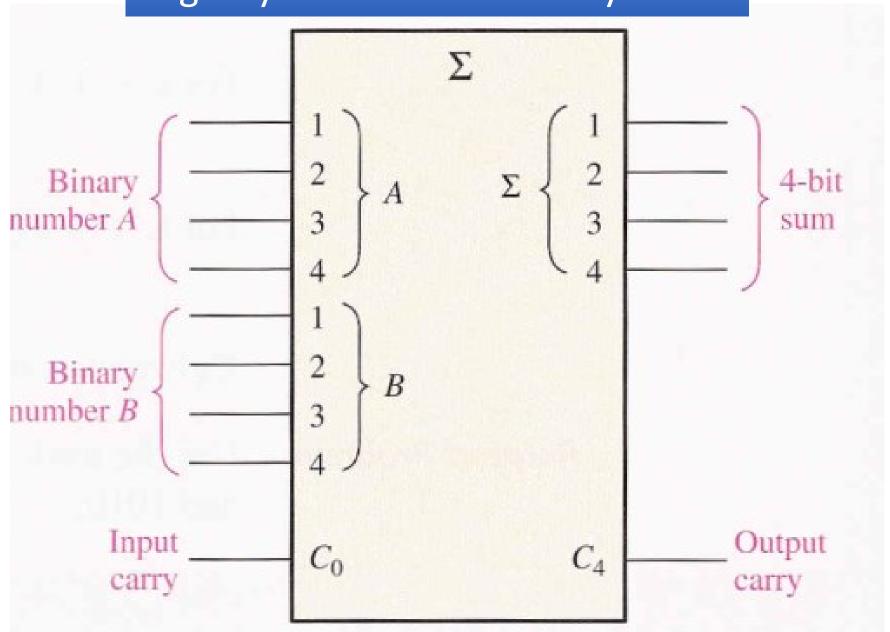

#### Logic Symbol of 4-Bit Binary Adder

### T-T for 4-Bit Binary Adder

| $C_{n-1}$ | $A_n$ | $\boldsymbol{B}_n$ | $\Sigma_n$ | $C_n$ |

|-----------|-------|--------------------|------------|-------|

| 0         | 0     | 0                  | 0          | 0     |

| 0         | 0     | 1                  | 1          | 0     |

| 0         | 1     | 0                  | 1          | 0     |

| 0         | 1     | 1                  | 0          | 1     |

| 1         | 0     | 0                  | 1          | 0     |

| 1         | 0     | 1                  | 0          | 1     |

| 1         | 1     | 0                  | 0          | 1     |

| 1         | 1     | 1                  | 1          | 1     |

#### Ex-2

Use the 4-bit parallel adder truth table to find the sum and output carry for the addition of the following two 4-bit numbers if the input carry  $(C_{n-1})$  is 0:

$$A_4A_3A_2A_1 = 1100$$

and  $B_4B_3B_2B_1 = 1100$

For n = 1:  $A_1 = 0$ ,  $B_1 = 0$ , and  $C_{n-1} = 0$ . From the 1st row of the table,

$$\Sigma_1 = \mathbf{0}$$

and  $C_1 = 0$

For n = 2:  $A_2 = 0$ ,  $B_2 = 0$ , and  $C_{n-1} = 0$ . From the 1st row of the table,

$$\Sigma_2 = \mathbf{0}$$

and  $C_2 = 0$

For n = 3:  $A_3 = 1$ ,  $B_3 = 1$ , and  $C_{n-1} = 0$ . From the 4th row of the table,

$$\Sigma_3 = \mathbf{0}$$

and  $C_3 = 1$

For n = 4:  $A_4 = 1$ ,  $B_4 = 1$ , and  $C_{n-1} = 1$ . From the last row of the table,

$$\Sigma_4 = 1$$

and  $C_4 = 1$

$C_4$  becomes the output carry; the sum of 1100 and 1100 is 11000.

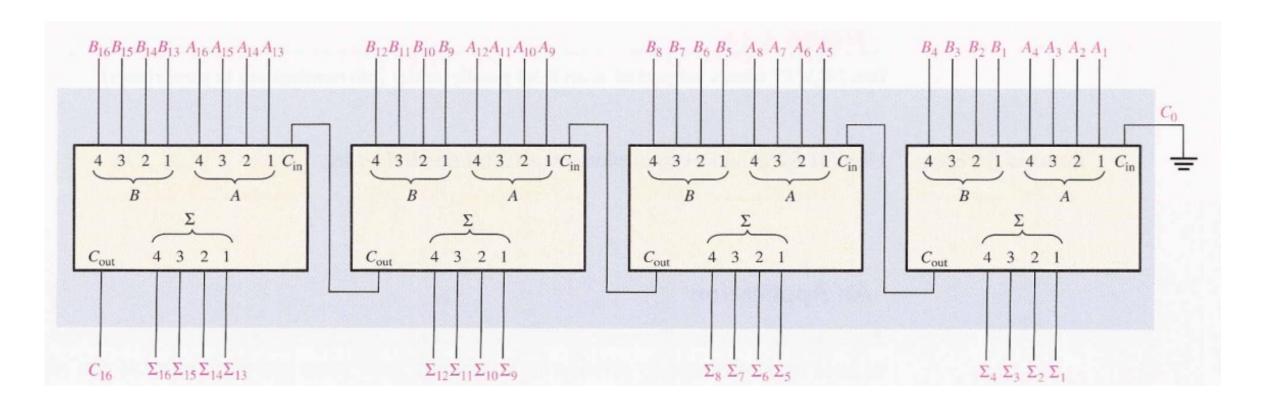

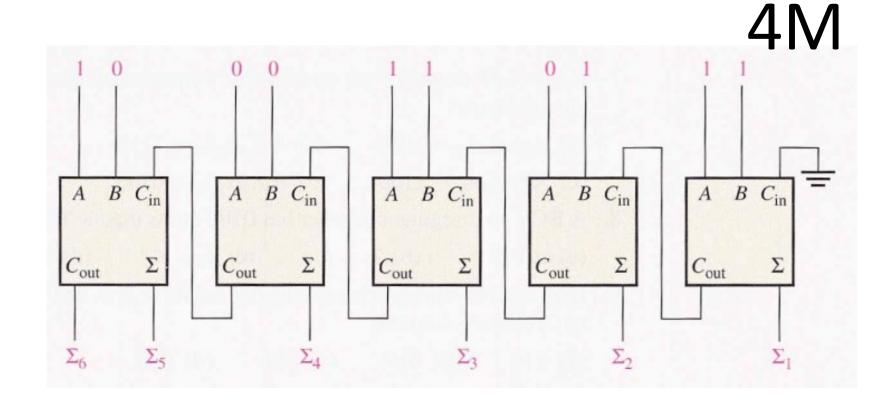

## Cascading of four 4-bit adders to form a 16-bit adder

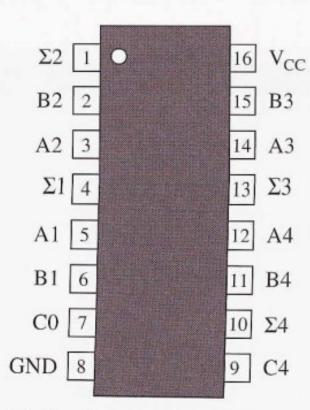

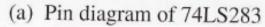

# 74LS283 IC

(b) 74LS283 logic symbol

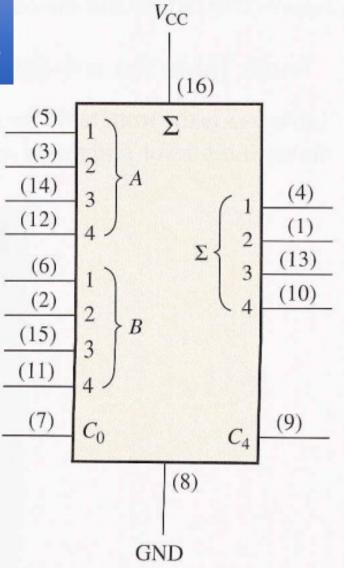

# Ex-3

Show how two 74LS283 adders can be connected to form an 8-bit parallel adder. Show output bits for the following 8-bit input numbers:

$$A_8A_7A_6A_5A_4A_3A_2A_1 = 10111001$$

and  $B_8B_7B_6B_5B_4B_3B_2B_1 = 10011110$

$$\Sigma_9 \Sigma_8 \Sigma_7 \Sigma_6 \Sigma_5 \Sigma_4 \Sigma_3 \Sigma_2 \Sigma_1 = 1010101111$$

# Solution

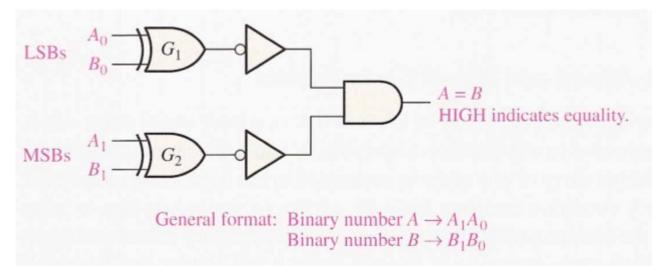

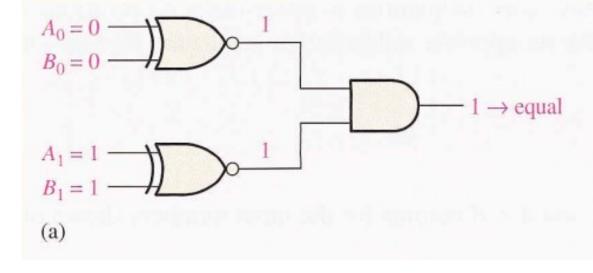

# Comparators

#### Ex-4: Compare the following two 2-bit Binary numbers

## (a) 10 and 10

### (b) 11 and 10

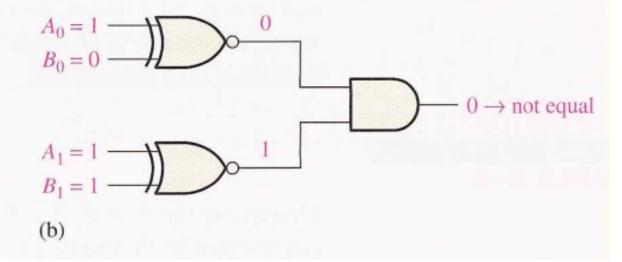

## 4-bit Comparator Logic Symbol

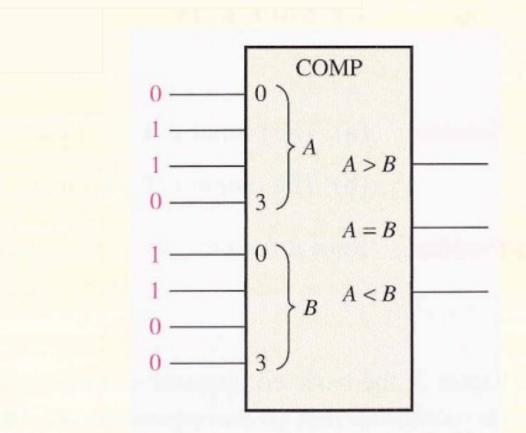

Determine the A = B, A > B, and A < B outputs for the input numbers shown on the comparator in Figure

The number on the A inputs is 0110 and the number on the B inputs is 0011. The A > B output is HIGH and the other outputs are LOW.

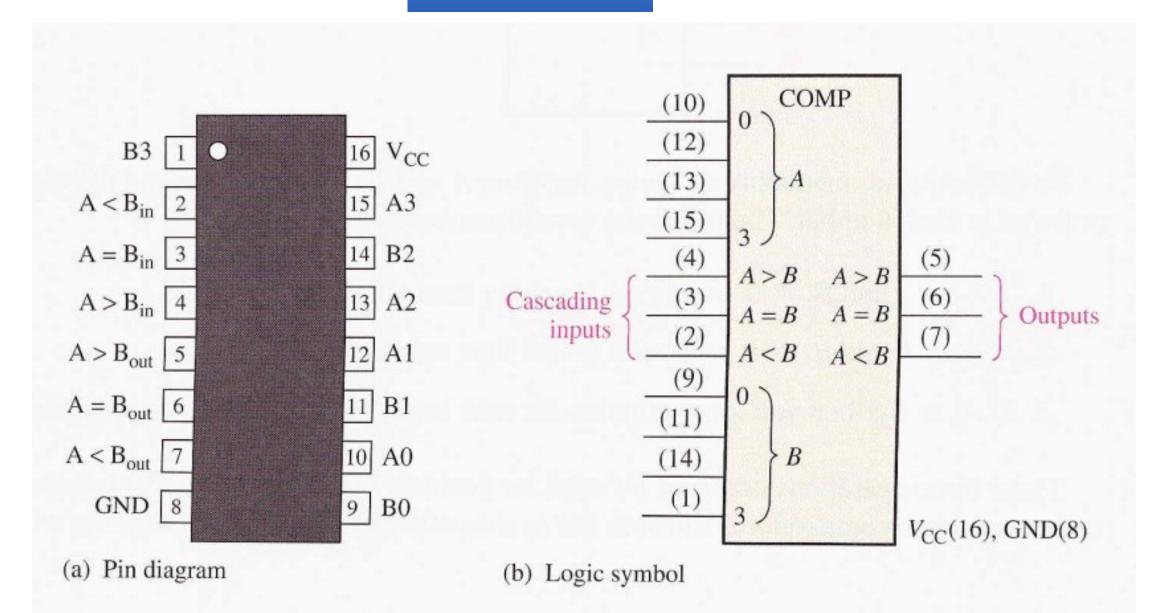

#### 74HC85 IC

### EX-6

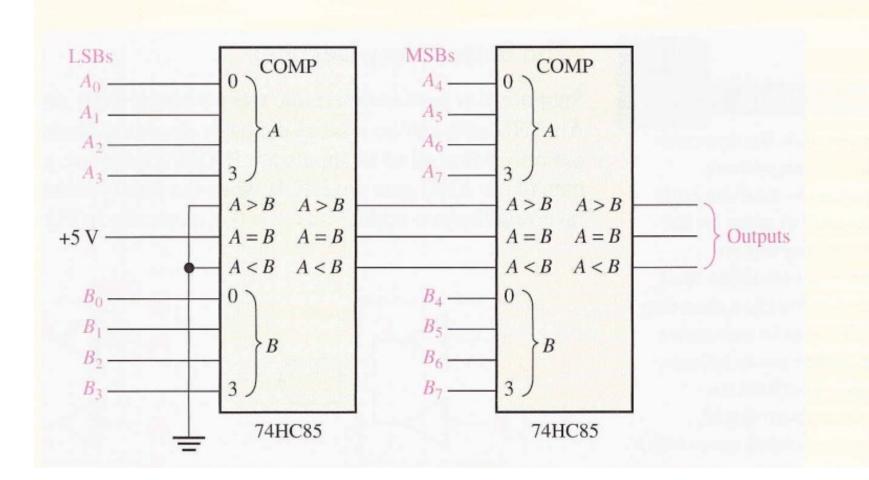

Use 74HC85 comparators to compare the magnitudes of two 8-bit numbers. Show the comparators with proper interconnections.

Two 74HC85s are required to compare two 8-bit numbers.

# Home Work (Due date 25-11-2023)

1 Use 4-bit Binary adder to find 1011+1010

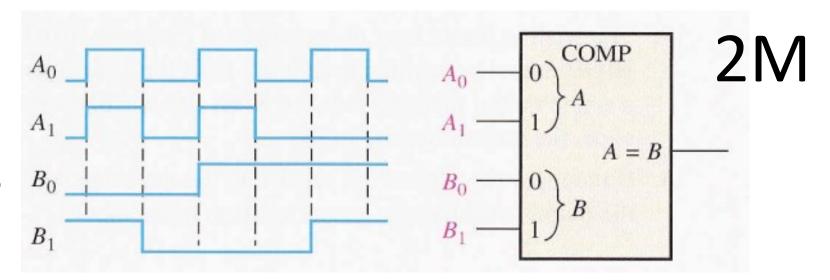

2M

2 Sketch the waveform A=B

Note: Home works are to be uploaded via the below google form <a href="https://forms.gle/FLuhwDqXWEAe2iFC8">https://forms.gle/FLuhwDqXWEAe2iFC8</a>

In the process of checking a 74LS283 4-bit parallel adder, the following voltage levels are observed on its pins: 1-HIGH, 2-HIGH, 3-HIGH, 4-HIGH, 5-LOW, 6-LOW, 7-LOW, 9-HIGH, 10-LOW, 11-HIGH, 12-LOW, 13-HIGH, 14-HIGH, and 15-HIGH. Determine if the IC is functioning properly.

4- Determine the complete Sum

#### University of Technology Laser & Optoelectronics Engineering Department

### DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 7: Functions of Combinational Logic 2: 2023-Nov-22

# Lecture Outline

- 1. Decoders

- 2. Encoders

- 3. Multiplexers

- 4. Demultiplexers

- 5. 74HC47 IC (BCD/7-SEG)

- 6. HW

# Decoders

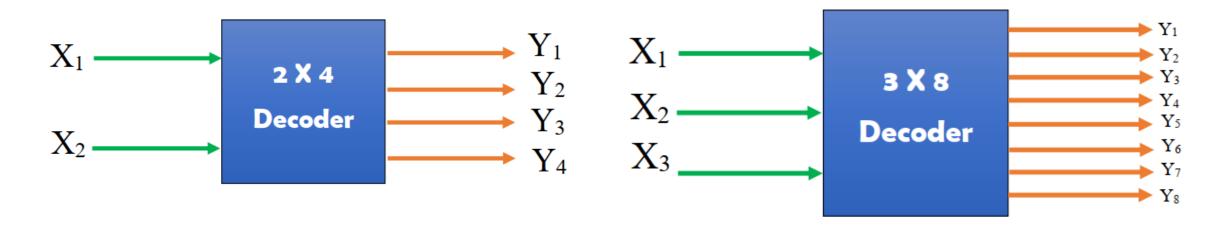

A **decoder** is a digital circuit that detects the presence of a specified combination of bits (code) on its inputs and indicates the presence of that code by a specified output level. In its general form, a decoder has n input lines to handle n bits and from one to  $2^n$  output lines to indicate the presence of one or more n-bit combinations

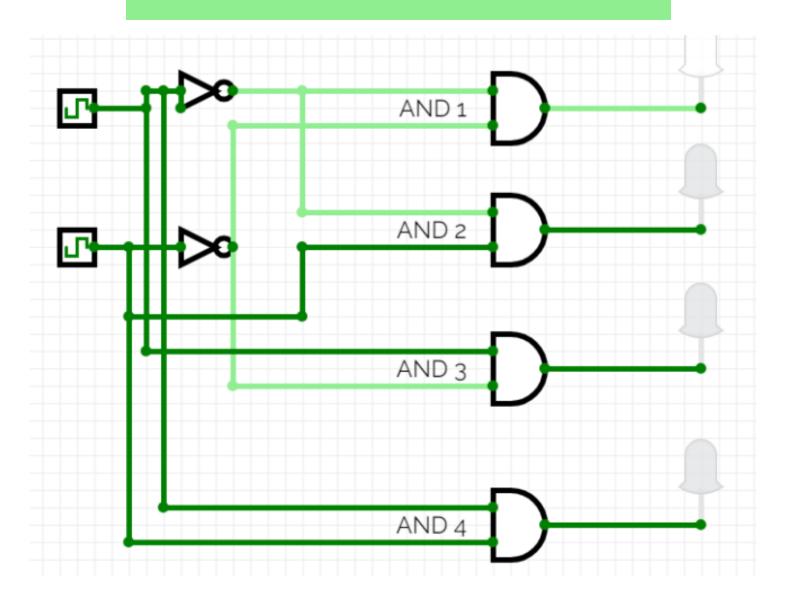

## 2X4 LINE Decoder

#### **Truth Table for 2X4 Line Decoder**

| Inp | outs | Outputs |    |    |    |  |  |

|-----|------|---------|----|----|----|--|--|

| X1  | X2   | Y1      | Y2 | Y3 | Y4 |  |  |

| 0   | 0    | 1       | 0  | 0  | 0  |  |  |

| 0   | 1    | 0       | 1  | 0  | 0  |  |  |

| 1   | 0    | 0       | 0  | 1  | 0  |  |  |

| 1   | 1    | 0       | 0  | 0  | 1  |  |  |

$$Y_1 = \overline{X_1}\overline{X_2}$$

$$Y_2 = \overline{X_1}X_2$$

$$Y_3 = X_1 \overline{X_2}$$

$$Y_4 = X_1 X_2$$

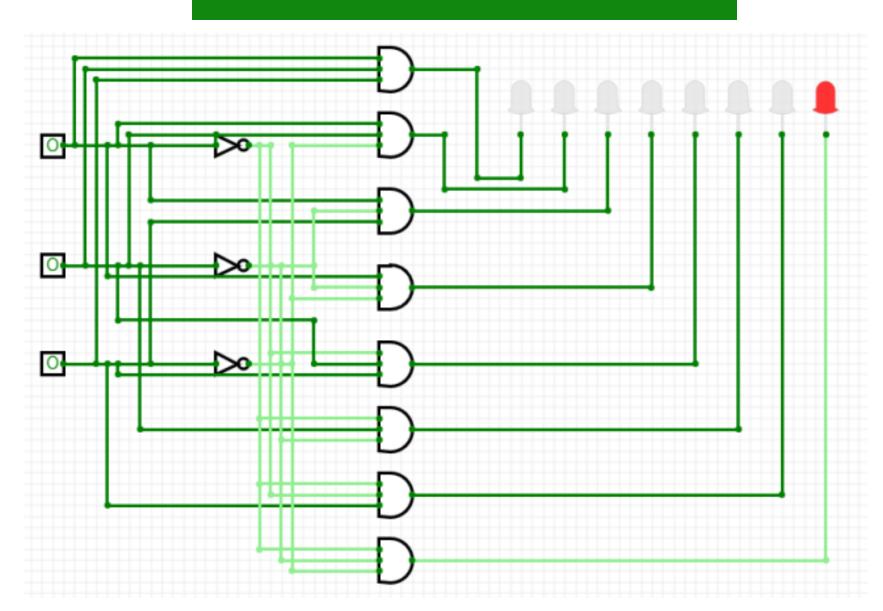

# 3X8 LINE Decoder

### **Truth Table for 3X8 Line Decoder**

|    | Inputs    |    |    | Outputs   |           |            |    |            |            |    |  |

|----|-----------|----|----|-----------|-----------|------------|----|------------|------------|----|--|

| X1 | <b>X2</b> | X3 | Y1 | <b>Y2</b> | <b>Y3</b> | <b>Y</b> 4 | Y5 | <b>Y</b> 6 | <b>Y</b> 7 | Y8 |  |

| 0  | 0         | 0  | 1  | 0         | 0         | 0          | 0  | 0          | 0          | 0  |  |

| 0  | 0         | 1  | 0  | 1         | 0         | 0          | 0  | 0          | 0          | 0  |  |

| 0  | 1         | 0  | 0  | 0         | 1         | 0          | 0  | 0          | 0          | 0  |  |

| 0  | 1         | 1  | 0  | 0         | 0         | 1          | 0  | 0          | 0          | 0  |  |

| 1  | 0         | 0  | 0  | 0         | 0         | 0          | 1  | 0          | 0          | 0  |  |

| 1  | 0         | 1  | 0  | 0         | 0         | 0          | 0  | 1          | 0          | 0  |  |

| 1  | 1         | 0  | 0  | 0         | 0         | 0          | 0  | 0          | 1          | 0  |  |

| 1  | 1         | 1  | 0  | 0         | 0         | 0          | 0  | 0          | 0          | 1  |  |

$$Y_1 = \overline{X_1 X_2 X_3}$$

$$Y_2 = \overline{X_1} \overline{X_2} X_3$$

$$Y_3 = \overline{X_1} X_2 \overline{X_3}$$

$$Y_4 = \overline{X_1} X_2 X_3$$

$$Y_5 = X_1 \overline{X_2 X_3}$$

$$Y_6 = X_1 \overline{X_2} X_3$$

$$Y_7 = X_1 X_2 \overline{X_3}$$

$$Y_8 = X_1 X_2 X_3$$

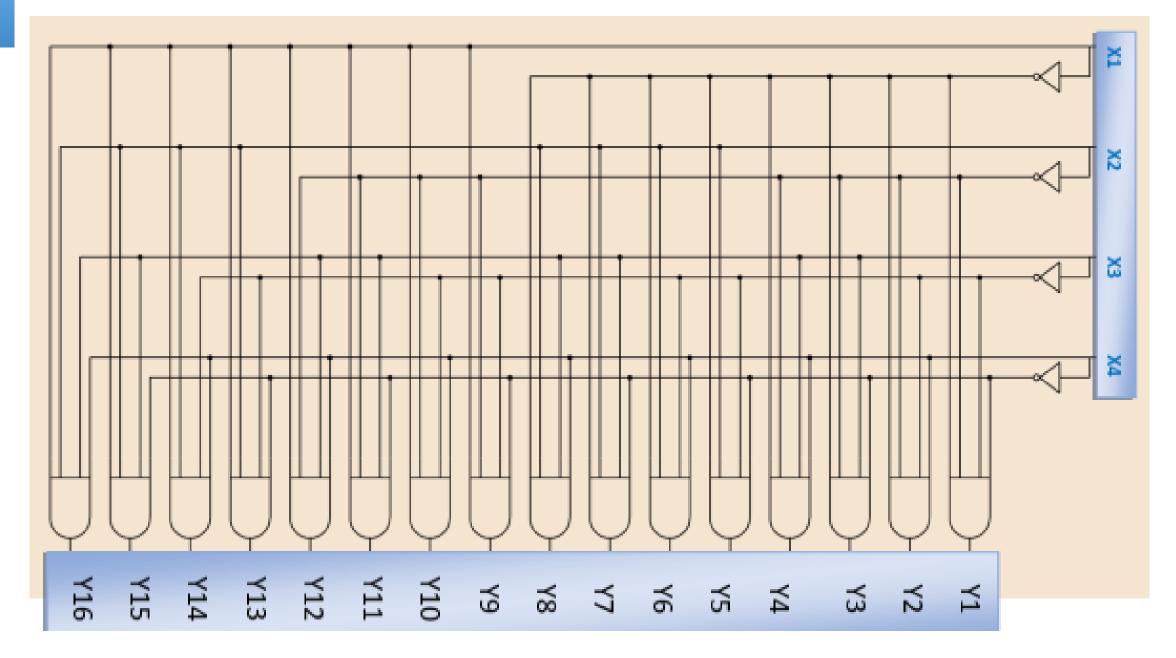

# EX-1

#### Using the equations below, design a 4X16 line decoder

# Sol

|   |    | Inp | uts |    |    | Outputs |    |    |    |    |    |    |    |     |     |     |     |     |     |     |

|---|----|-----|-----|----|----|---------|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

| X | (1 | X2  | Х3  | X4 | Y1 | Y2      | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| ( | 0  | 0   | 0   | 0  | 1  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|   | 0  | 0   | 0   | 1  | 0  | 1       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| ( | 0  | 0   | 1   | 0  | 0  | 0       | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| ( | 0  | 0   | 1   | 1  | 0  | 0       | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|   | 0  | 1   | 0   | 0  | 0  | 0       | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| ( | 0  | 1   | 0   | 1  | 0  | 0       | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| ( | 0  | 1   | 1   | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|   | 0  | 1   | 1   | 1  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| • | 1  | 0   | 0   | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| • | 1  | 0   | 0   | 1  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1   | 0   | 0   | 0   | 0   | 0   | 0   |

| • | 1  | 0   | 1   | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0   | 0   | 0   | 0   | 0   |

| • | 1  | 0   | 1   | 1  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 1   | 0   | 0   | 0   | 0   |

| • | 1  | 1   | 0   | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 1   | 0   | 0   | 0   |

| • | 1  | 1   | 0   | 1  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 1   | 0   | 0   |

| • | 1  | 1   | 1   | 0  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| • | 1  | 1   | 1   | 1  | 0  | 0       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

# Sol

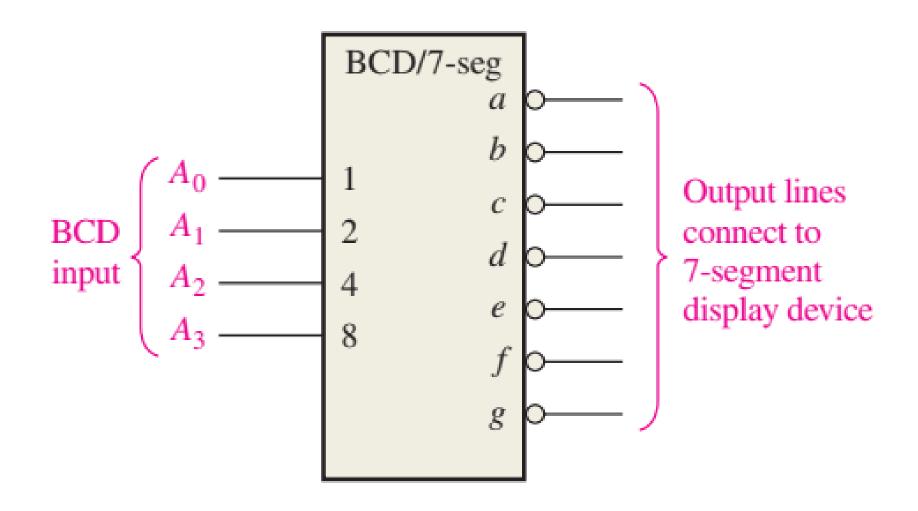

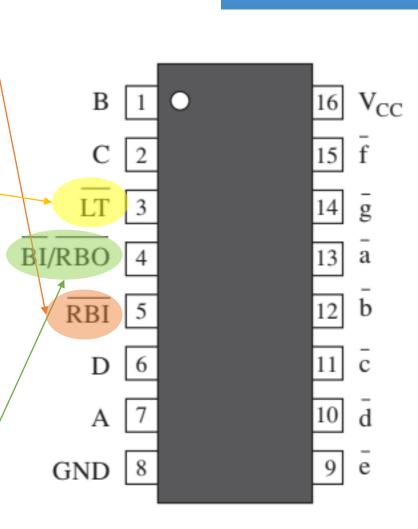

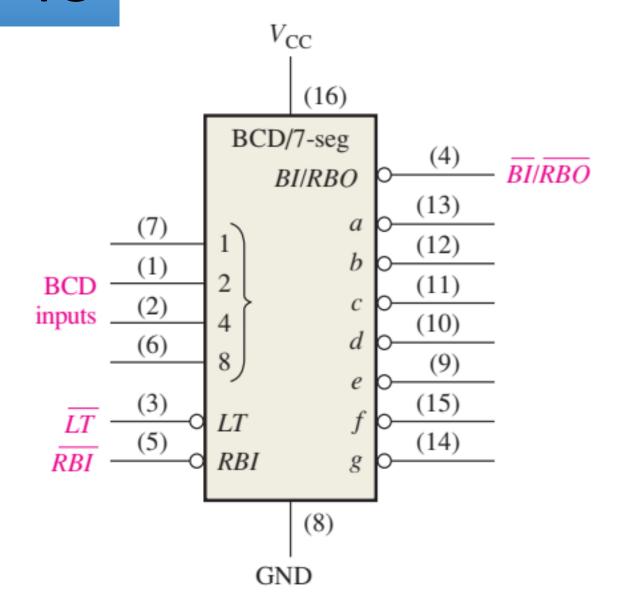

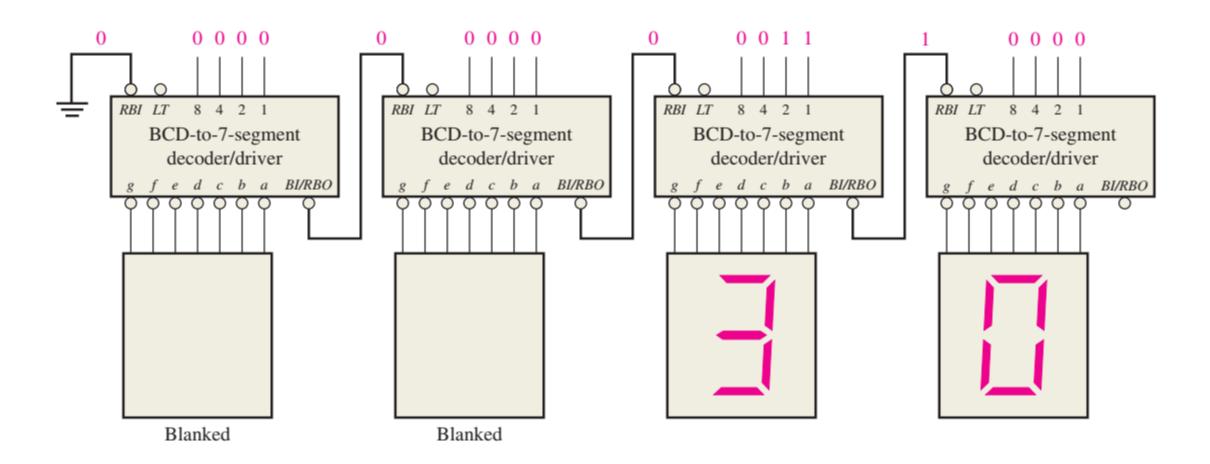

# BCD/7-SEG

## 74HC47 IC

Ripple Blanking Input

Lamp Test

Blanking

Input /

Ripple

Blanking

Output

#### Leading zero suppression

#### Trailing zero suppression

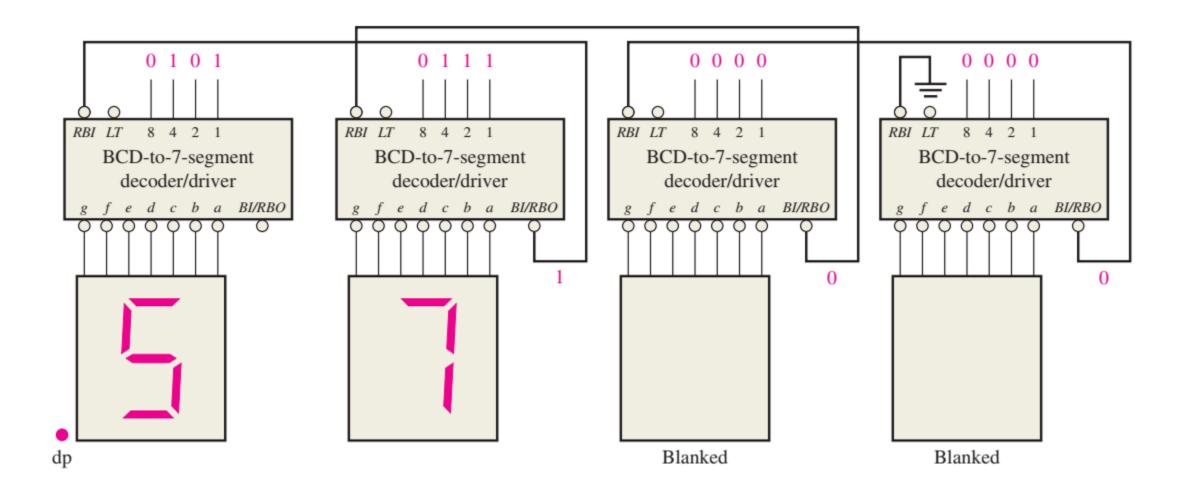

# Encoder

An **encoder** is a combinational logic circuit that essentially performs a "reverse" decoder function. An encoder accepts an active level on one of its inputs representing a digit, such as a decimal or octal digit, and converts it to a coded output, such as BCD or binary. Encoders can also be devised to encode various symbols and alphabetic characters. The process of converting from familiar symbols or numbers to a coded format is called *encoding*.

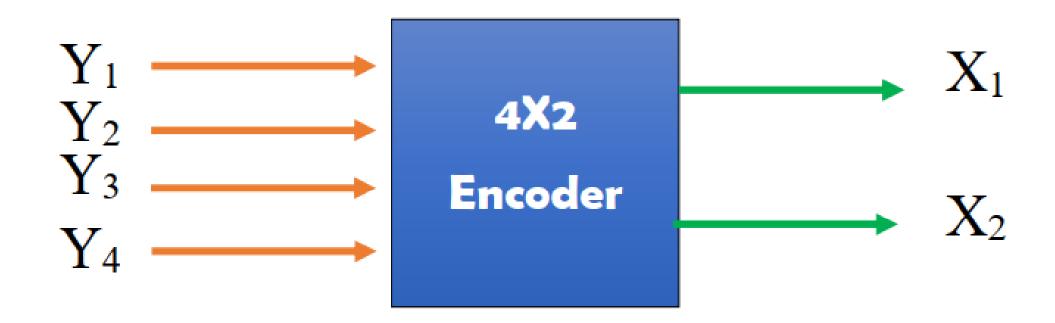

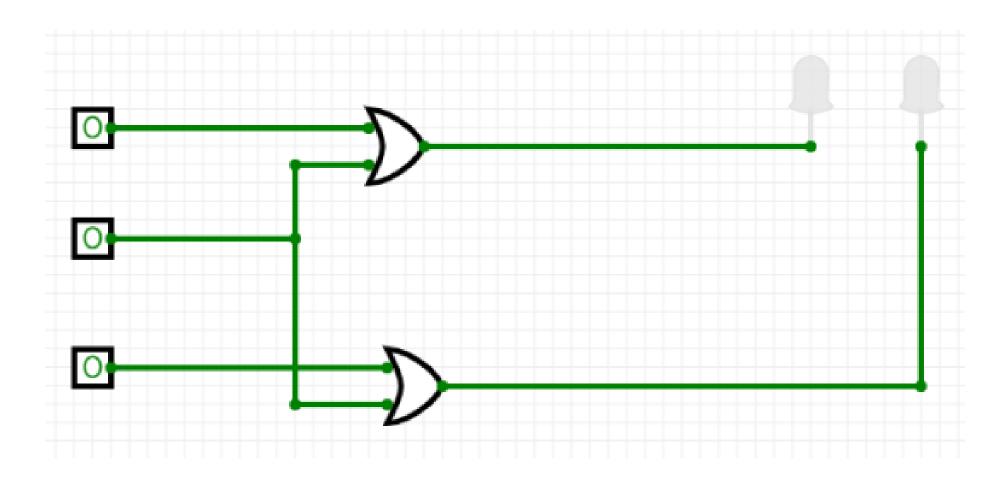

## 4 x 2 Line Encoder

#### **Truth Table for 4X2 Line Encoder**

|    | Inp | Outputs |            |    |    |

|----|-----|---------|------------|----|----|

| Y1 | Y2  | Y3      | <b>Y</b> 4 | X1 | X2 |

| 0  | 0   | 0       | 1          | 0  | 0  |

| 0  | 0   | 1       | 0          | 0  | 1  |

| 0  | 1   | 0       | 0          | 1  | 0  |

| 1  | 0   | 0       | 0          | 1  | 1  |

$$X_1 = Y_2 + Y_1$$

$X_2 = Y_3 + Y_1$

# Multiplexer

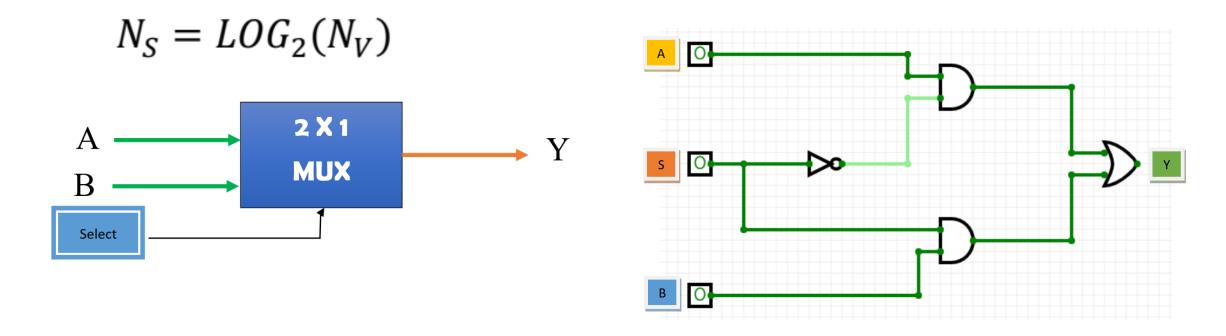

A multiplexer (MUX) is a device that allows digital information from several sources to be routed onto a single line for transmission over that line to a common destination. The basic multiplexer has several data-input lines and a single output line. It also has data-select inputs, which permit digital data on any one of the inputs to be switched to the output line. Multiplexers are also known as **data selectors**

### Truth Table for 2X1 Line Multiplexer

| Inp          | uts | Selector | Output |

|--------------|-----|----------|--------|

| $\mathbf{A}$ | В   | S        | Y      |

| 1            | X   | 0        | A      |

| X            | 1   | 1        | В      |

$$Y_1 = A$$

$$Y_2 = B$$

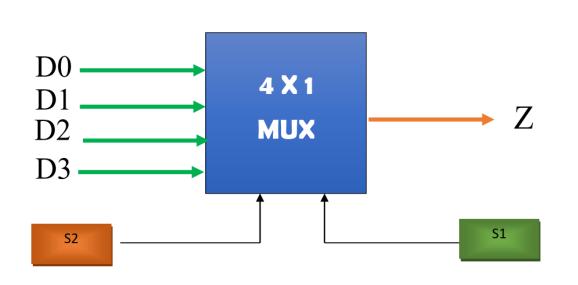

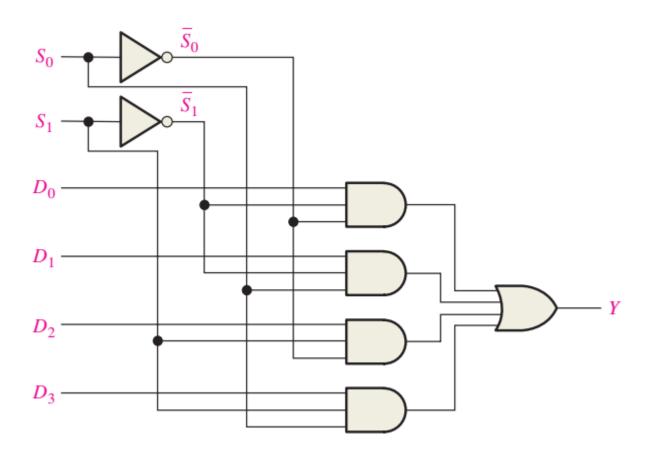

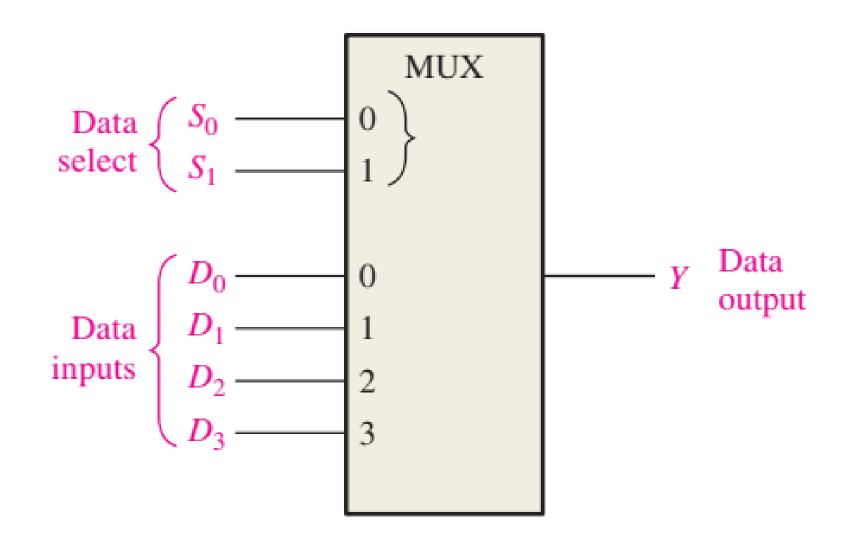

## 4x1 Multiplexer

#### **Truth Table for 4X1 Line Multiplexer**

| $Y_1$      | $= \bar{A}$ | $Y_2 =$ | A   |

|------------|-------------|---------|-----|

| <b>4</b> 1 | _ 11        | 12 —    | 4 1 |

$$Y_3 = \bar{B}$$

$Y_4 = B$

$$Y_5 = \bar{C}$$

$Y_6 = C$

$$Y_7 = \overline{D}$$

$Y_8 = D$

|    | Inp       | uts       |           | Selectors |    | Output               |

|----|-----------|-----------|-----------|-----------|----|----------------------|

| D0 | <b>D1</b> | <b>D2</b> | <b>D3</b> | S0        | S1 | Z                    |

| 0  | X         | X         | X         | 0         | 0  | $\overline{A}$       |

| 1  | X         | X         | X         | 0         | 0  | A                    |

| X  | 0         | X         | X         | 0         | 1  | $\overline{\pmb{B}}$ |

| X  | 1         | X         | X         | 0         | 1  | В                    |

| X  | X         | 0         | X         | 1         | 0  | $\overline{\it C}$   |

| X  | X         | 1         | X         | 1         | 0  | C                    |

| X  | X         | X         | 0         | 1         | 1  | $\overline{m{D}}$    |

| X  | X         | X         | 1         | 1         | 1  | D                    |

## 4x1 Multiplexer Symbol

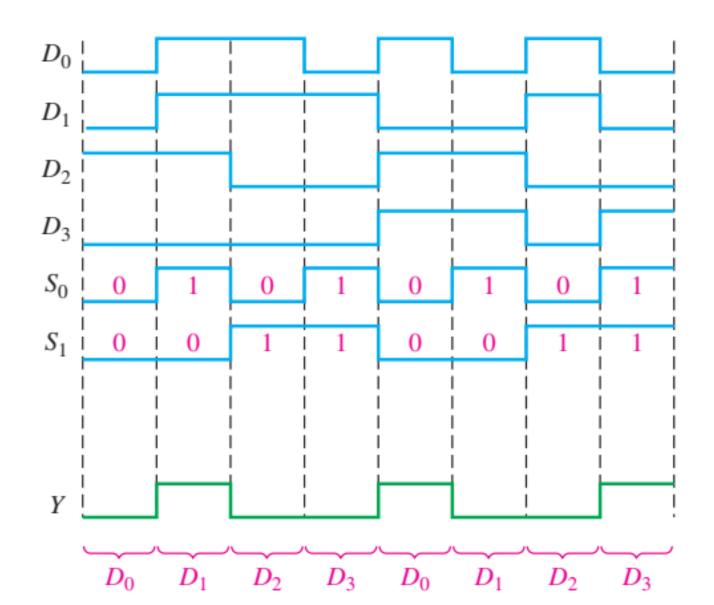

## 4x1 Multiplexer Timing Diagram

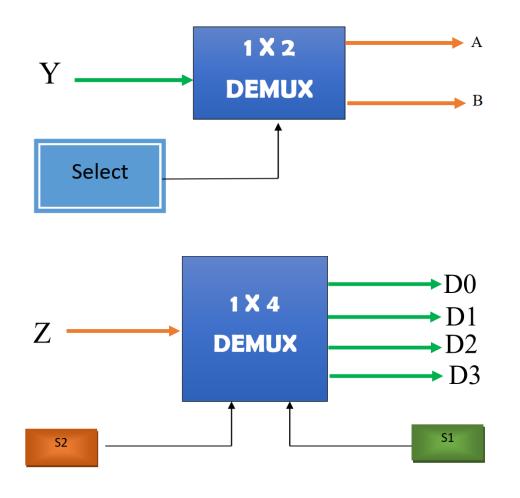

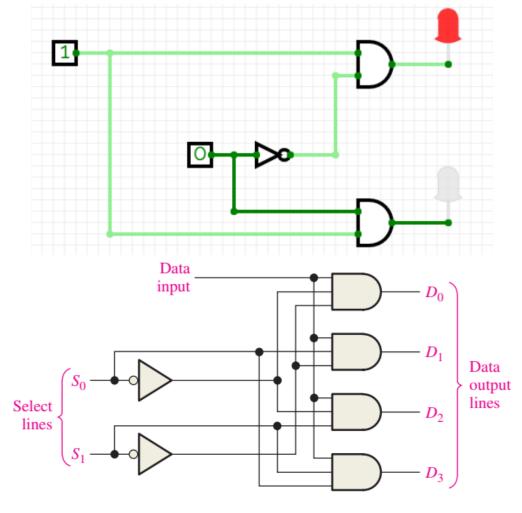

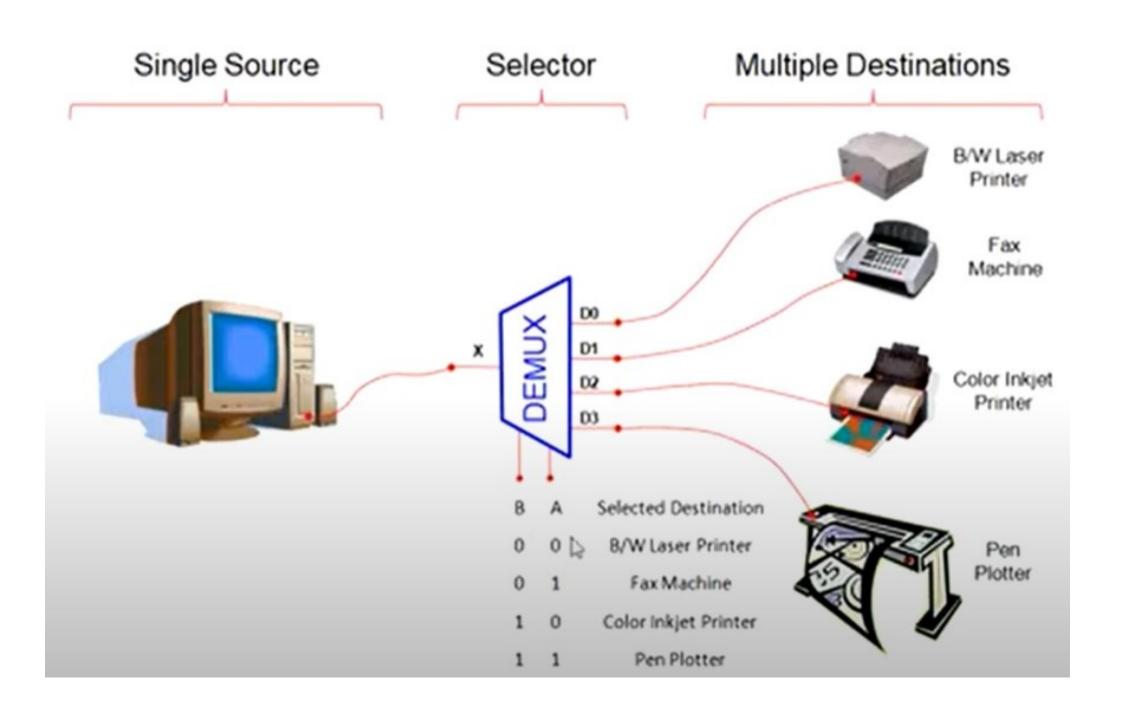

#### Demultiplexer

A demultiplexer (DEMUX) basically reverses the multiplexing function. It takes digital information from one line and distributes it to a given number of output lines (data

distributor).

### Truth Table for 1x4 Line Demultiplexer

| Inputs | Sele | ector | Output     |           |           |           |  |

|--------|------|-------|------------|-----------|-----------|-----------|--|

| ON     | S0   | S1    | <b>D</b> 0 | <b>D1</b> | <b>D2</b> | <b>D3</b> |  |

| A      | 0    | 0     | 1          | X         | X         | X         |  |

| В      | 0    | 1     | X          | 1         | X         | X         |  |

| C      | 1    | 0     | X          | X         | 1         | X         |  |

| D      | 1    | 1     | X          | X         | X         | 1         |  |

$$Y_1 = A$$

$$Y_2 = B$$

$$Y_3 = C$$

$$Y_4 = D$$

## Home Work (Due date 02-12-2023)

1 Design a 1-to-32 line demultiplexer Using Both 1-to-4 10 M and 1-to-8 line demultiplexers

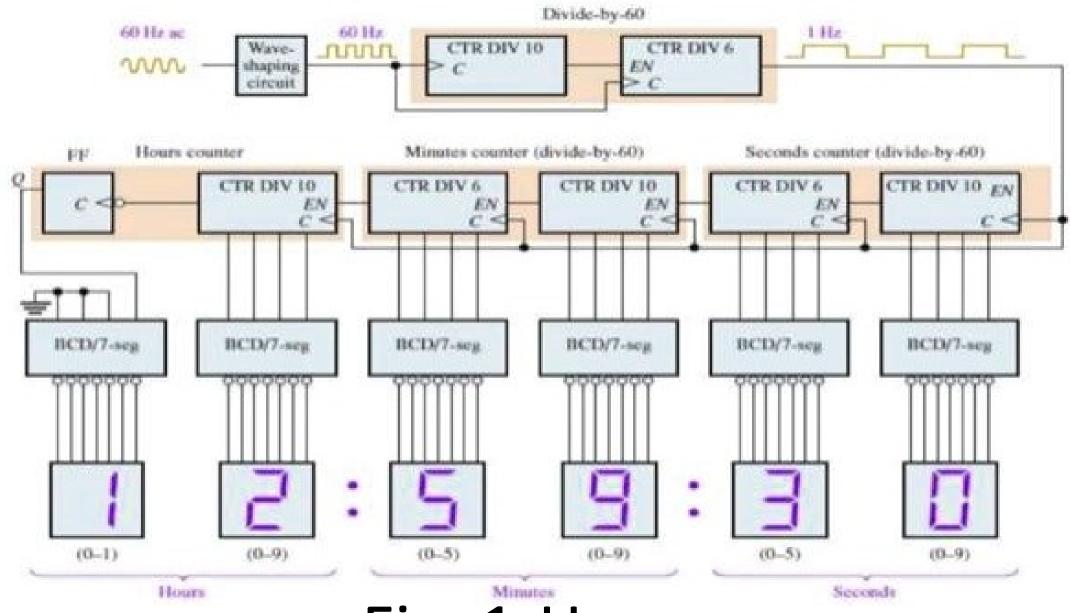

2 Explain the operation of Fig 1H, next slide 6 M

Note: Home works are to be uploaded via the below google form <a href="https://forms.gle/rwSkyv1yb5ZUNqnr7">https://forms.gle/rwSkyv1yb5ZUNqnr7</a>

Fig. 1-H

### University of Technology Laser & Optoelectronics Engineering Department

## DIGITAL ELECTRONICS

Lec. Dr. Taif Alawsi

Lec. 8: Sequential Circuits: 2023-Dec-06

## Lecture Outline

- 1. Flip-Flops

- 2. Counters

- 3. 555 Timer

- 4. Oscillator

- 5. HW

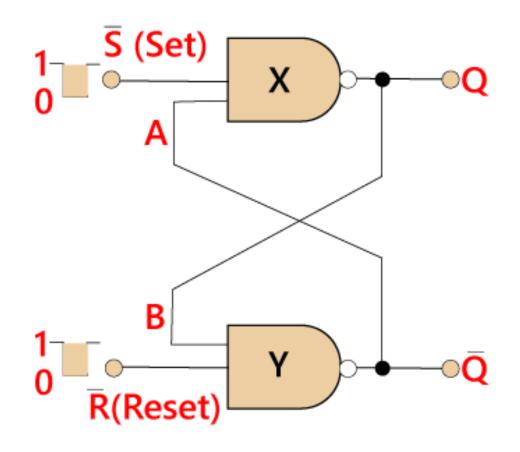

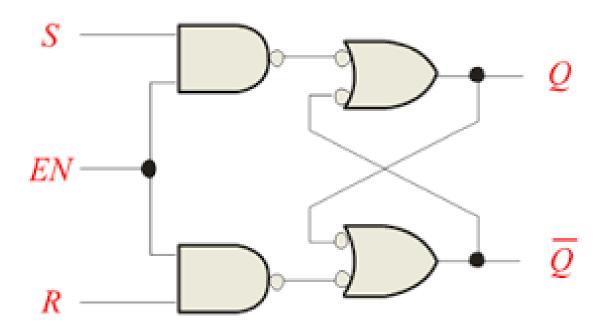

## SR & GATED SR

## State Table

| State   | S | R | α | ď | Description |

|---------|---|---|---|---|-------------|

| Set     | 1 | 0 | 0 | 1 | Set Q'>>1   |

|         | 1 | 1 | 0 | 1 | No change   |

| Reset   | 0 | 1 | 1 | 0 | Reset Q'>>0 |

|         | 1 | 1 | 1 | 0 | No change   |

| Invalid | 0 | 0 | 1 | 1 | Invalid     |

|         |   |   |   |   | Condition   |

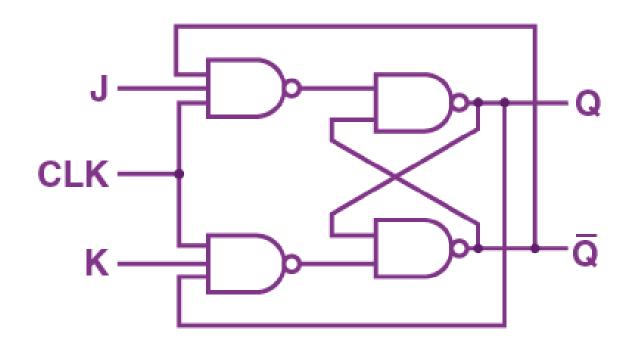

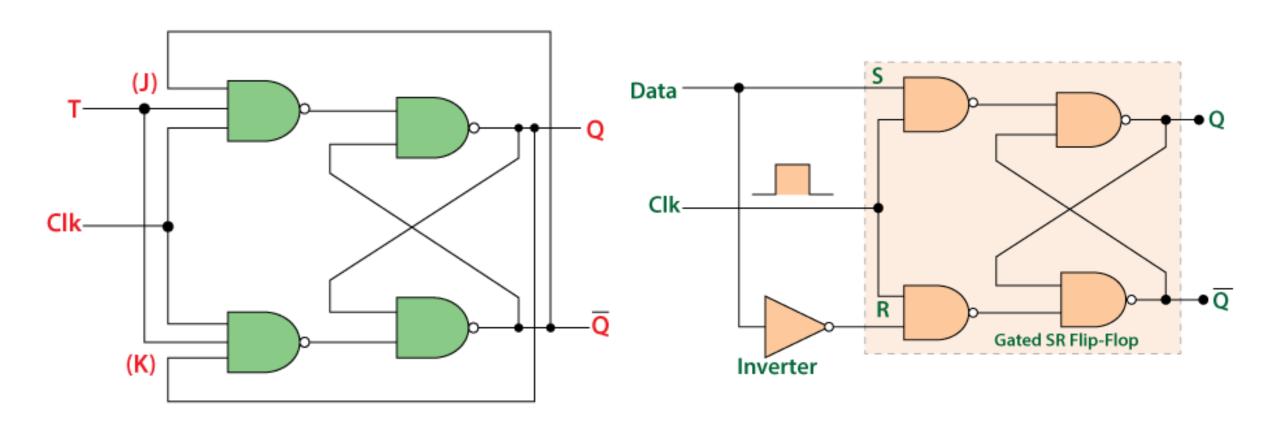

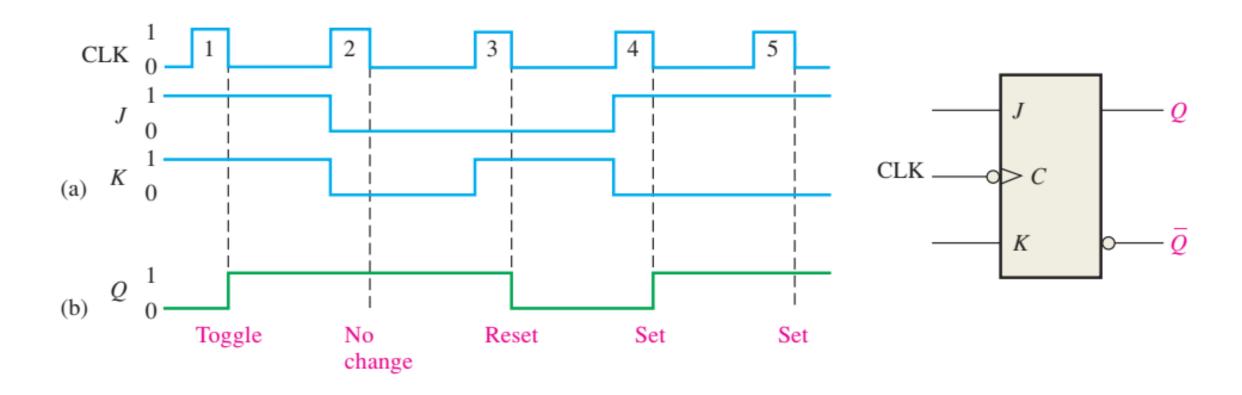

## JK FF

|   | Inputs |     | Outputs                                |                               |           |

|---|--------|-----|----------------------------------------|-------------------------------|-----------|

| J | K      | CLK | Q                                      | Q                             | Comments  |

| 0 | 0      | †   | Q <sub>o</sub>                         | $\overline{\overline{Q}}_{0}$ | No change |

| 0 | 1      | †   | 0                                      | 1                             | RESET     |

| 1 | 0      | †   | 1                                      | 0                             | SET       |

| 1 | 1      | †   | $\overline{Q}_{\scriptscriptstyle{0}}$ | $Q_0$                         | Toggle    |

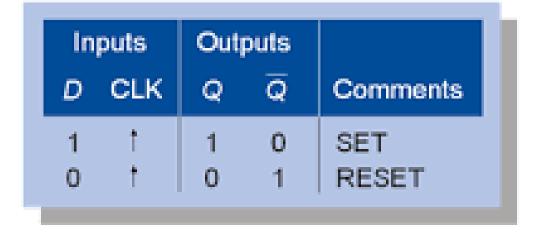

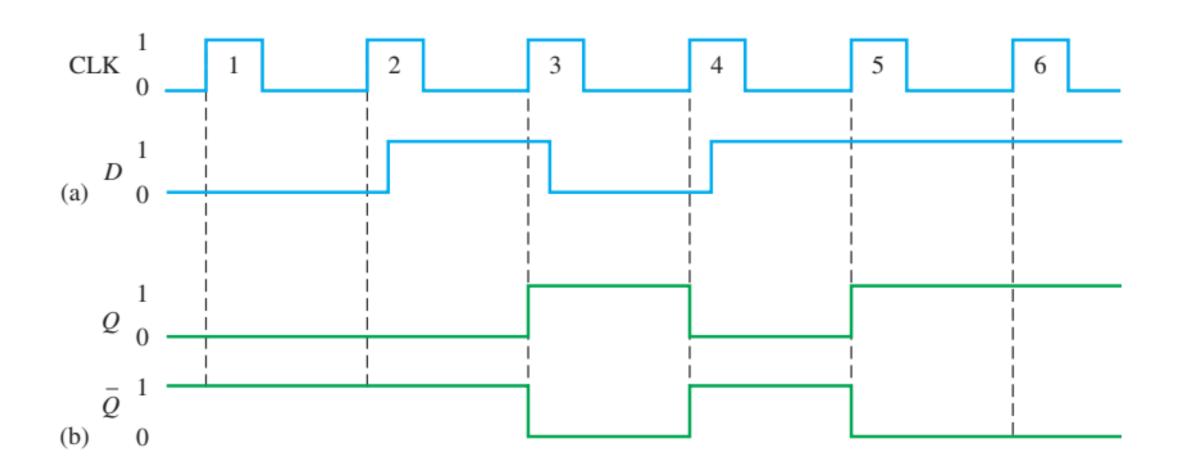

## T & D FF

#### T & D FF

| Truth table  |   |                         |            |  |  |

|--------------|---|-------------------------|------------|--|--|

| CLK          | T | Q <sub>next</sub>       | Comment    |  |  |

| Rising edge  | 0 | Q                       | Hold state |  |  |

| Falling edge | 0 | Q                       | Hold state |  |  |

| Rising edge  | 1 | $\overline{\mathbf{Q}}$ | Toggle     |  |  |

| Falling edge | 1 | Q                       | No change  |  |  |

$Q_{\mathrm{next}}\,$  - "after the clock transition" output

*Q* - the current output

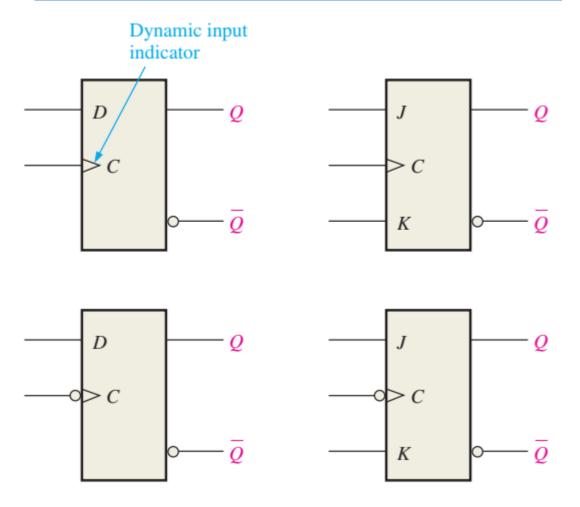

## FF (+VE & -VE Edge)

## Timing Diagram

# -ve edge JKFF Operation

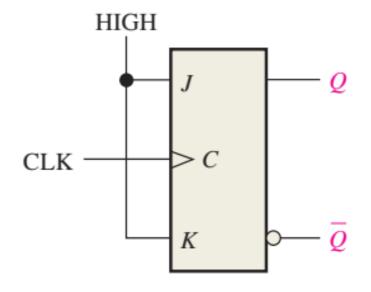

# Frequency Doubler

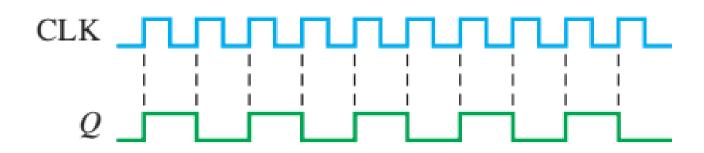

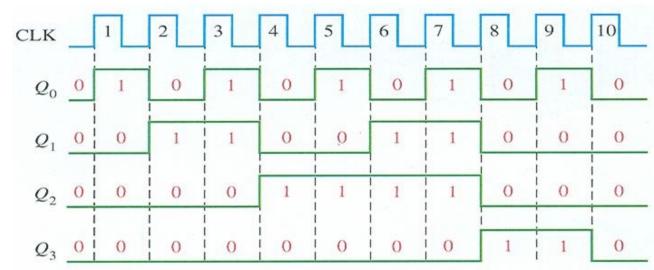

#### Counter HIGH - $Q_A$ $Q_B$ CLK -CLKKKFlip-flop B Flip-flop A $Q_B$ 3 3 Binary Binary sequence sequence

2-bit Binary

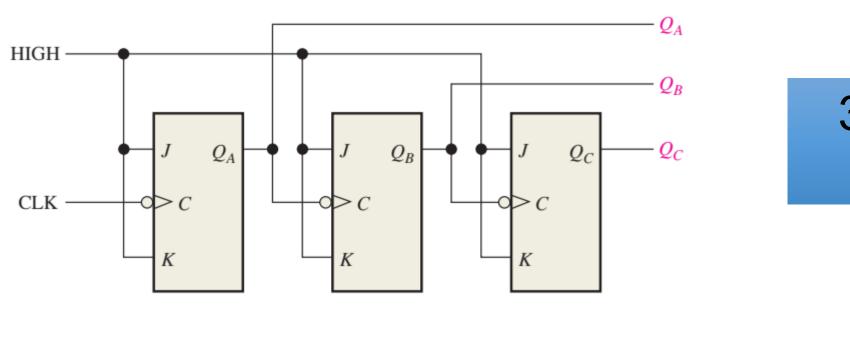

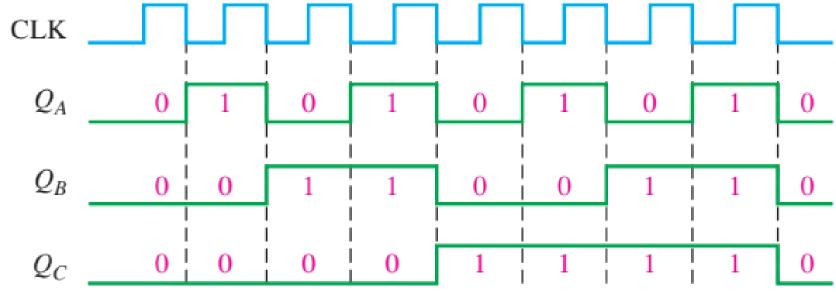

# 3-bit Binary Counter

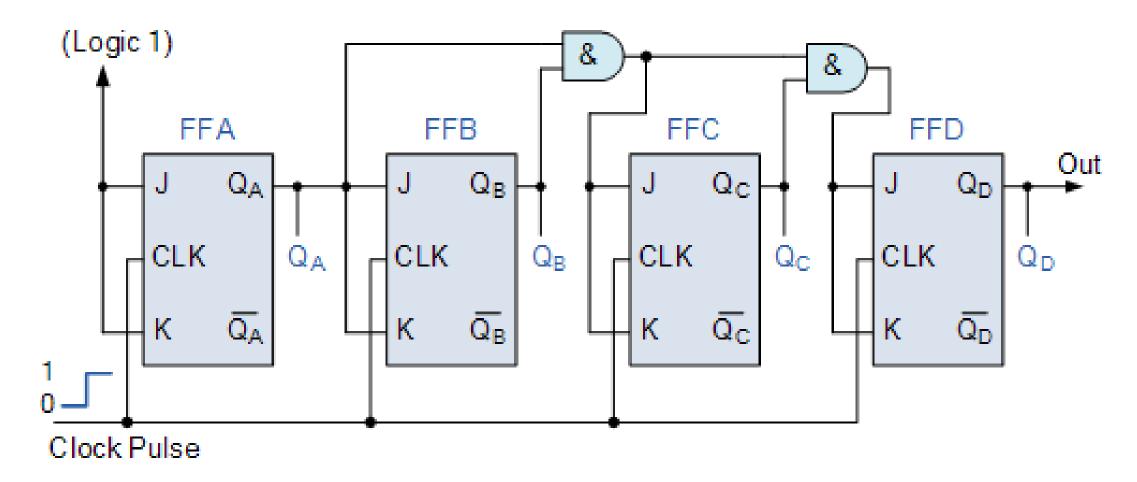

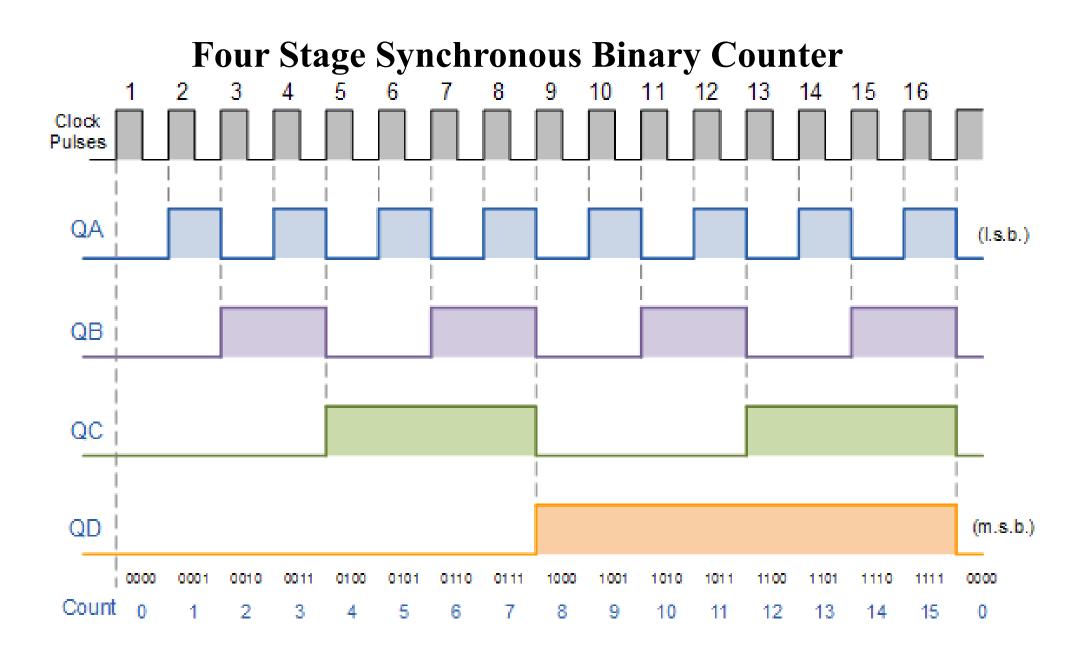

#### Four Stage Synchronous Binary Counter

#### States of a BCD decade counter.

| Clock Pulse   | $Q_3$ | $Q_2$ | $Q_1$ | $Q_0$ |

|---------------|-------|-------|-------|-------|

| Initially     | 0     | 0     | 0     | 0     |

| 1             | 0     | 0     | 0     | 1     |

| 2             | 0     | 0     | 1     | 0     |

| 3             | 0     | 0     | 1     | 1     |

| 4             | 0     | 1     | 0     | 0     |

| 5             | 0     | 1     | 0     | 1     |

| 6             | 0     | 1     | 1     | 0     |

| 7             | 0     | 1     | 1     | 1     |

| 8             | 1     | 0     | 0     | 0     |

| 9             | 1     | 0     | 0     | 1     |

| 10 (recycles) | 0     | 0     | 0     | 0     |

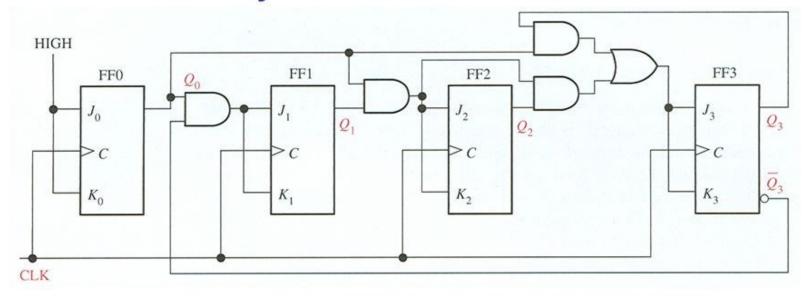

$$J_0 = K_0 = 1$$

$$J_1 = K_1 = Q_0 \overline{Q}_3$$

$$J_2 = K_2 = Q_0 Q_1$$

$$J_3 = K_3 = Q_0 Q_1 Q_2 + Q_0 Q_3$$

#### A 4 bit Synchronous Decade Counter

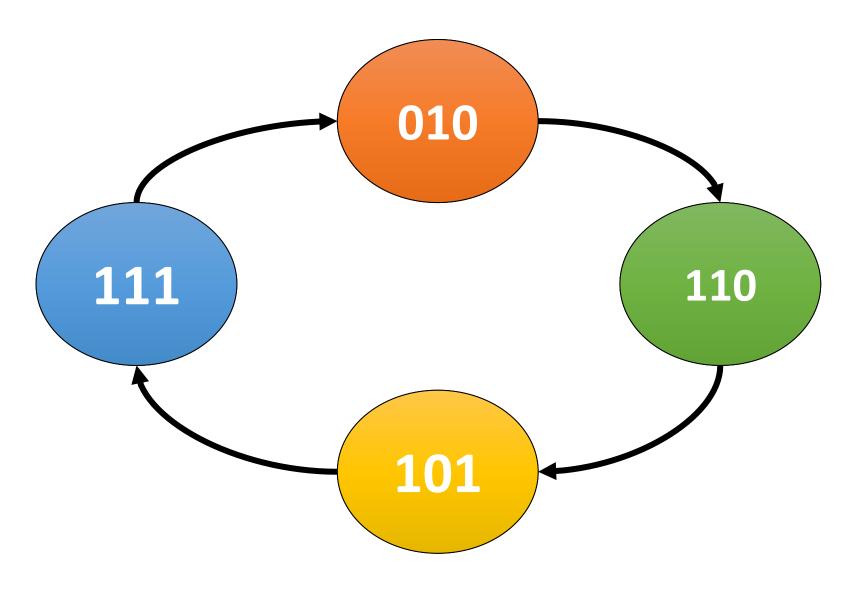

## Counters Design Steps

STEP 1

Given in the

Question

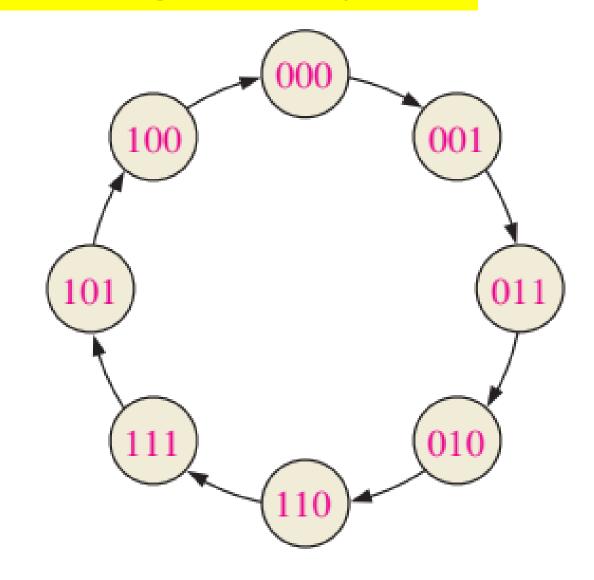

## STEP 2: Create the State Table

| Present State |    |    | Next State |    |    |  |

|---------------|----|----|------------|----|----|--|

| Q2            | Q1 | Q0 | Q2         | Q1 | Q0 |  |

| 0             | 0  | 0  | 0          | 0  | 1  |  |

| 0             | 0  | 1  | 0          | 1  | 1  |  |

| 0             | 1  | 1  | 0          | 1  | 0  |  |

| 0             | 1  | 0  | 1          | 1  | 0  |  |

| 1             | 1  | 0  | 1          | 1  | 1  |  |

| 1             | 1  | 1  | 1          | 0  | 1  |  |

| 1             | 0  | 1  | 1          | 0  | 0  |  |

| 1             | 0  | 0  | 0          | 0  | 0  |  |

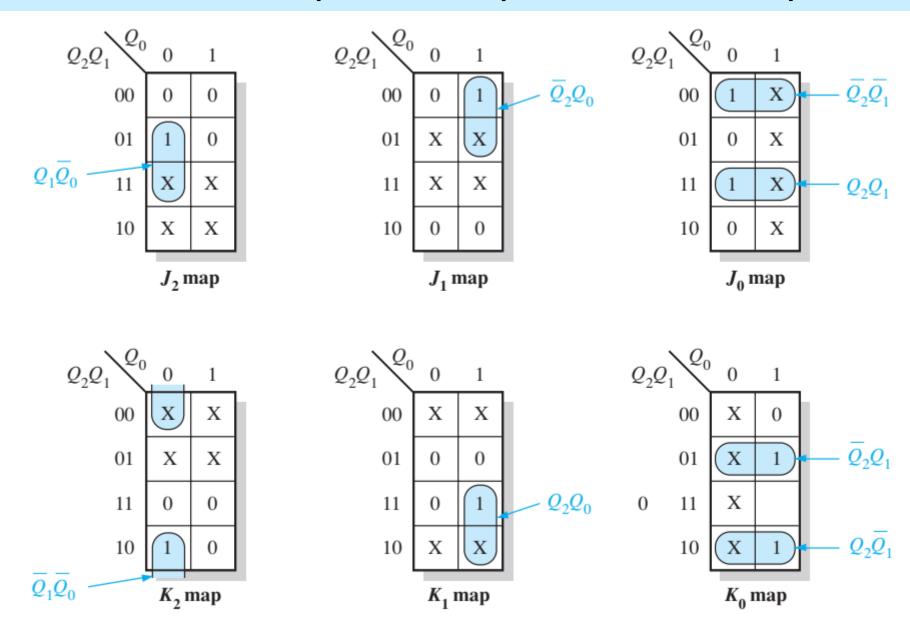

#### STEP 3: Each FF Has its own Transition Table

Transition table for a J-K flip-flop.

| Output Transitions |                   |           | Flip-Flo | p Inputs |

|--------------------|-------------------|-----------|----------|----------|

| $Q_N$              |                   | $Q_{N+1}$ | J        | K        |

| 0                  | $\longrightarrow$ | 0         | 0        | X        |

| 0                  | $\longrightarrow$ | 1         | 1        | X        |

| 1                  | $\longrightarrow$ | 0         | X        | 1        |

| 1                  | $\longrightarrow$ | 1         | X        | 0        |

$Q_N$ : present state

$Q_{N+1}$ : next state

X: "don't care"

We will use only JK FF Memorize this table

## STEP 4: Use the Transition Table to find the output

|    | Outputs |    |           |    |    |  |  |  |

|----|---------|----|-----------|----|----|--|--|--|

| J2 | K2      | J1 | <b>K1</b> | JO | K0 |  |  |  |

| 0  | X       | 0  | X         | 1  | X  |  |  |  |

| 0  | X       | 1  | X         | X  | 0  |  |  |  |

| 0  | X       | X  | 0         | X  | 1  |  |  |  |

| 1  | X       | X  | 0         | 0  | X  |  |  |  |

| X  | 0       | X  | 0         | 1  | X  |  |  |  |

| X  | 0       | X  | 1         | X  | 0  |  |  |  |

| X  | 0       | 0  | X         | X  | 1  |  |  |  |

| X  | 1       | 0  | X         | 0  | X  |  |  |  |

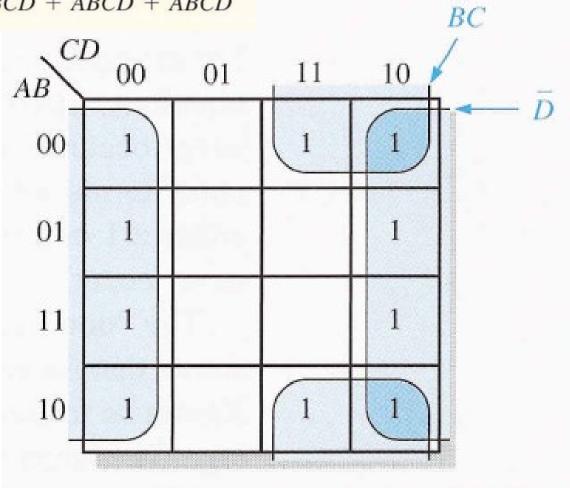

#### STEP 5: Map the Outputs into K-Map

#### STEP 6: Find the Equation Using K-Map Minimization Techniques

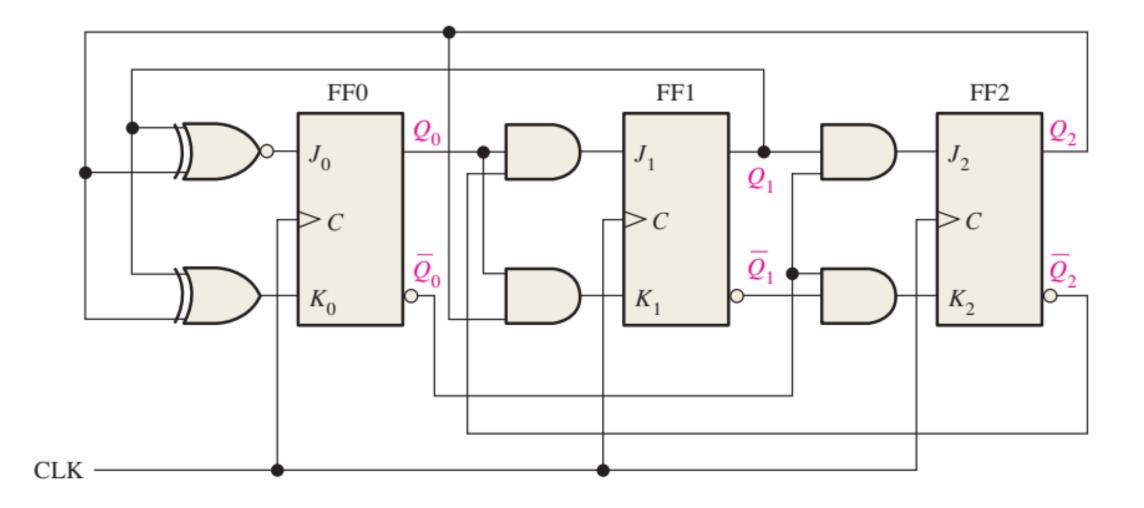

$$J_{0} = Q_{2}Q_{1} + \overline{Q}_{2}\overline{Q}_{1} = \overline{Q_{2} \oplus Q_{1}}$$

$$K_{0} = Q_{2}\overline{Q}_{1} + \overline{Q}_{2}Q_{1} = Q_{2} \oplus Q_{1}$$

$$J_{1} = \overline{Q}_{2}Q_{0}$$

$$K_{1} = Q_{2}Q_{0}$$

$$J_{2} = Q_{1}\overline{Q}_{0}$$

$$K_{2} = \overline{Q}_{1}\overline{Q}_{0}$$

## STEP 7: Build the Counter

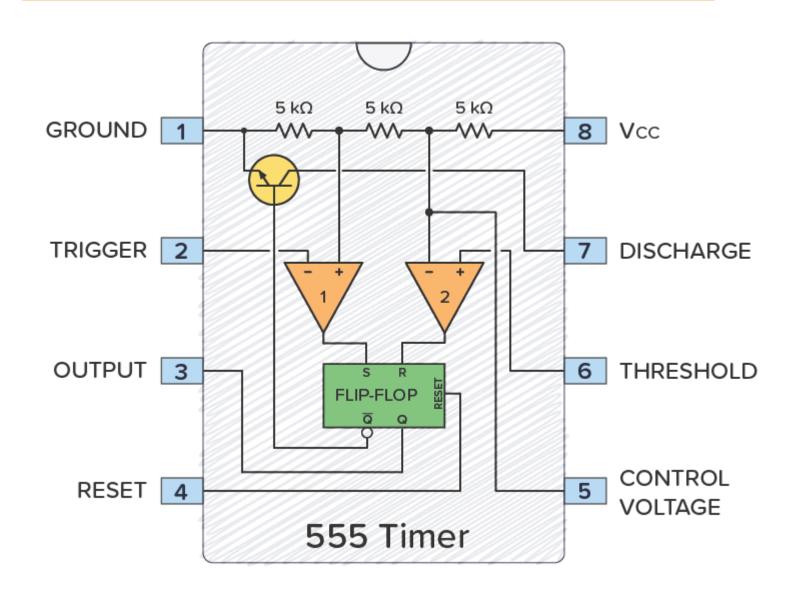

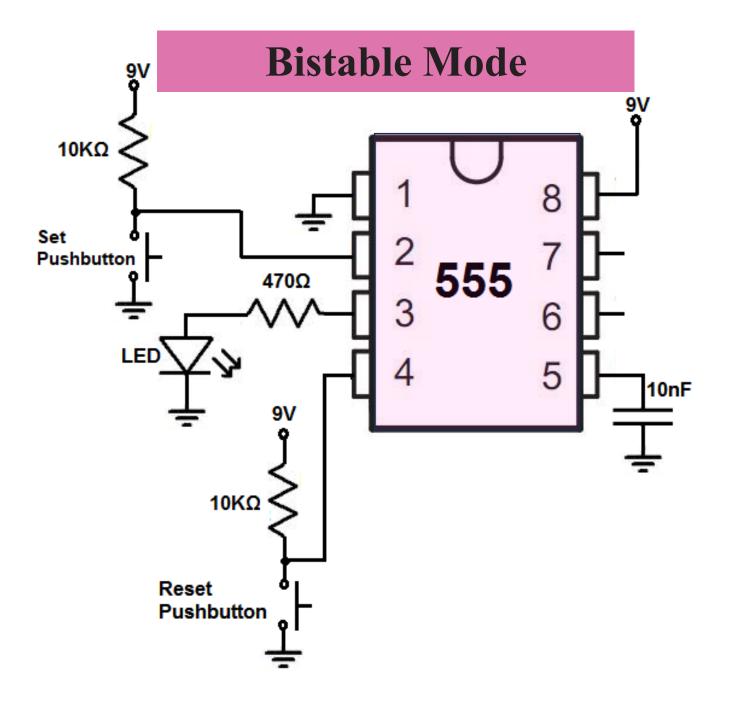

#### 555 Timer IC

## 555 Timer

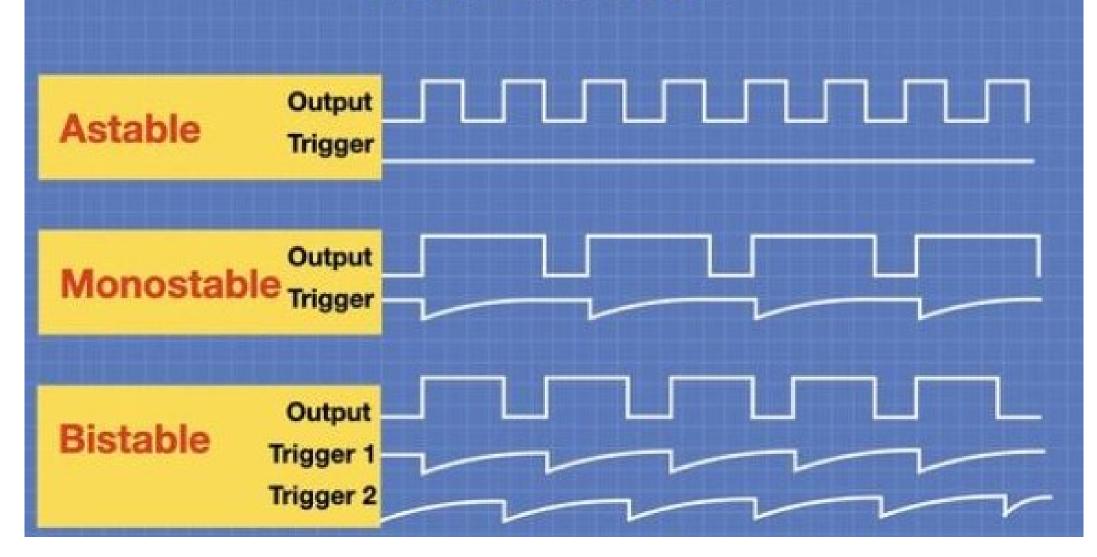

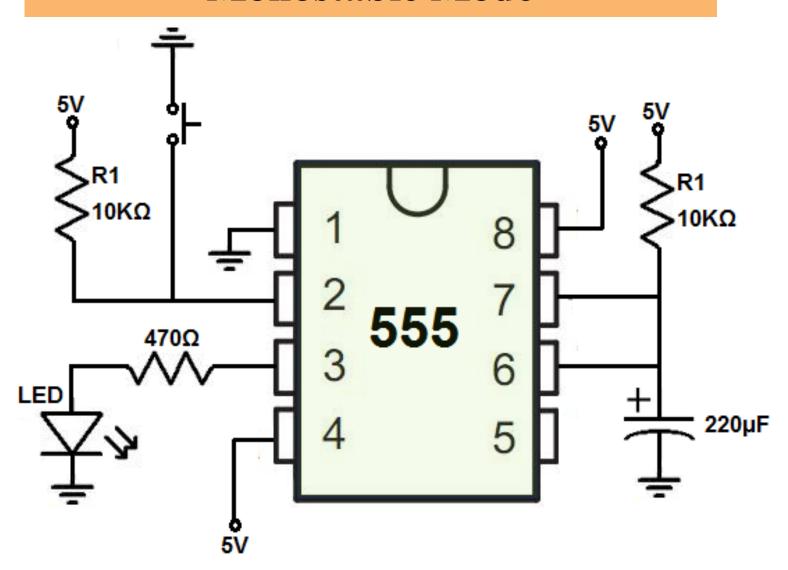

#### **Monostable Mode**

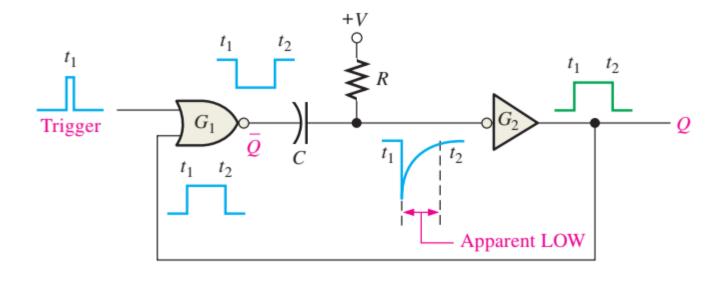

## **One-Shot**

#### Non-retriggerable

$$t_W = 0.7RC_{\rm EXT}$$

#### **The Schmitt-Trigger**

$$t_W = 0.32RC_{\text{EXT}} \left( 1 + \frac{0.7}{R} \right)$$

The 555 Timer  $t_W = 1.1R_1C_1$

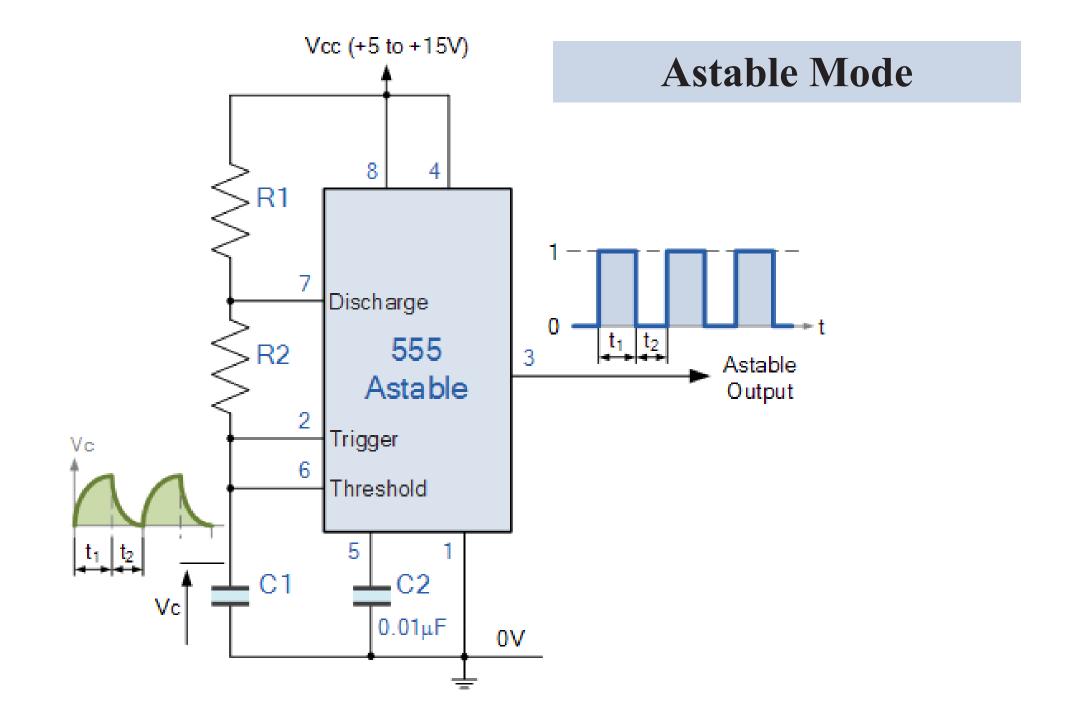

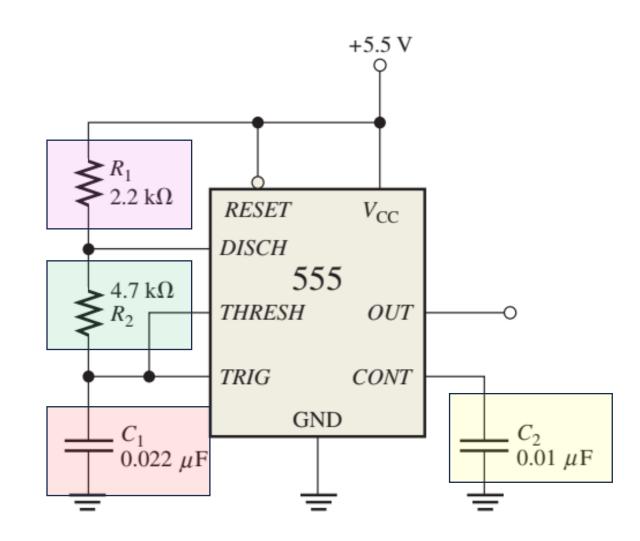

#### **Oscillators (Astable Multivibrators)**

The frequency of oscillation

$$f = \frac{1.44}{(R_1 + 2R_2)C_1}$$

The time that the output is HIGH  $(t_H)$

$$t_H = 0.7(R_1 + R_2)C_1$$

The time that the output is LOW  $(t_L)$

$$t_L = 0.7R_2C_1$$

The period, T

$$T = t_H + t_L = 0.7(R_1 + 2R_2)C_1$$

The duty cycle is

Duty cycle =

$$\left(\frac{R_1 + R_2}{R_1 + 2R_2}\right) 100\%$$

#### **EXAMPLE**

A 555 timer configured to run in the astable mode (pulse oscillator) Determine the frequency of the output and the duty cycle.

#### Solution

$$f = \frac{1.44}{(R_1 + 2R_2)C_1} = \frac{1.44}{(2.2 \text{ k}\Omega + 9.4 \text{ k}\Omega)0.022 \,\mu\text{F}} = 5.64 \text{ kHz}$$

Duty cycle =  $\left(\frac{R_1 + R_2}{R_1 + 2R_2}\right)100\% = \left(\frac{2.2 \text{ k}\Omega + 4.7 \text{ k}\Omega}{2.2 \text{ k}\Omega + 9.4 \text{ k}\Omega}\right)100\% = 59.5\%$

## Home Work (Due date 12-12-2023)

- Determine the values of the external resistors for a 555 timer used as an astable multivibrator with an output frequency of 20 kHz, if the external capacitor C is 0.002  $\mu$ F and the duty cycle is to be approximately 75%.

- 2 Design A Synchronous counter with JK flip flop 14 M that gives the sequence shown in Fig 1-H

Note: Home works are to be uploaded via the below google form <a href="https://forms.gle/VadQZdkzGSJzbkVB6">https://forms.gle/VadQZdkzGSJzbkVB6</a>

Fig 1-H